基于運(yùn)用EDA技術(shù),以FPGA器件為核心,用Verilog HDL硬件描述語言來設(shè)計(jì)各個功能模塊,采用DDS直接數(shù)字頻率合成技術(shù)設(shè)計(jì)信號發(fā)生器,通過CPU控制每個采樣點(diǎn)的輸出間隔來控制輸出波形的頻率,改變波形存儲器中的波形數(shù)據(jù)來產(chǎn)生任意波形。

0 引言

信號發(fā)生器應(yīng)用非常廣泛,包括通信、測量、控制、雷達(dá)還有教學(xué)等鄰域,是不可或缺的工具。隨著科學(xué)技術(shù)的不斷發(fā)展,信號發(fā)生器的設(shè)計(jì)方法越來越多,其設(shè)計(jì)技術(shù)也越來越先進(jìn)。傳統(tǒng)的信號源種類多樣,但大多是采用專用芯片或單片機(jī)或模擬電路,不但具有成本高、控制方式不靈活、波形種類少等特點(diǎn)不能滿足使用者的要求,而且其外圍電路也過于復(fù)雜,應(yīng)用起來效果不盡人意。

隨著FPGA(Field Programmable Gate Array)技術(shù)的引入,微電子技術(shù)的突飛猛進(jìn),在信號發(fā)生的領(lǐng)地得到了極大的拓展,技術(shù)手段呈現(xiàn)快速發(fā)展的勢頭,應(yīng)用更加廣泛和靈活,特別是其在信號發(fā)生器上的良好運(yùn)用得到了充分的體現(xiàn),有效解決了傳統(tǒng)信號發(fā)生器帶來的模式單一、運(yùn)行繁雜等一系列問題。

由于以上原因本設(shè)計(jì)提出以基于EDA技術(shù)的FPGA器件作為主控芯片,依據(jù)DDS直接數(shù)字頻率合成技術(shù),提出了一種比較簡單的信號發(fā)生器設(shè)計(jì)方法。利用Quartus II軟件結(jié)合VerilogHDL硬件描述語言進(jìn)行系統(tǒng)編程,經(jīng)過調(diào)試后下載到本設(shè)計(jì)中的FPGA器件EP1C3T100C8N中,通過實(shí)驗(yàn)驗(yàn)證表明,該信號發(fā)生器可以產(chǎn)生正弦波、方波、三角波,信號頻率范圍在0.02~1 MHz。

1信號發(fā)生器系統(tǒng)結(jié)構(gòu)

1.1 系統(tǒng)總體結(jié)構(gòu)

一個基于FPGA的DDS信號發(fā)生器,可以生成標(biāo)準(zhǔn)的正弦波、方波、三角波等常用波形。

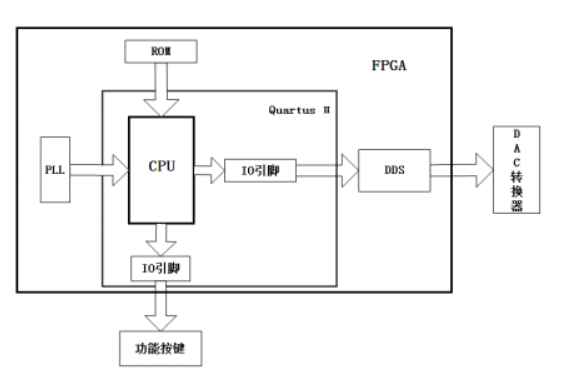

在FPGA完成DDS的功能,通過Quartus II實(shí)現(xiàn)按鍵控制,系統(tǒng)結(jié)構(gòu)框圖如圖1-1所示。

圖1-1 系統(tǒng)結(jié)構(gòu)框圖

圖1-1所示的是整個系統(tǒng)的結(jié)構(gòu)圖,下面對圖中所涉及的一些功能部分進(jìn)行簡要的說明。

a.PLL部分:此部分為系統(tǒng)鎖相環(huán),功能是為整個系統(tǒng)提供工作時鐘,并且在后面控制輸出波形的頻率提供一個基準(zhǔn)頻率。

b.ROM部分:此部分是存儲波形數(shù)據(jù)的查找表,是實(shí)現(xiàn)DDS信號發(fā)生器的必要工具,通過改變ROM查找表內(nèi)的數(shù)據(jù)就能改變輸出波形。

c.DDS部分:此部分是通過代碼實(shí)現(xiàn)的,是本設(shè)計(jì)的關(guān)鍵所在,它的作用是輸出數(shù)字信號給后面的DAC轉(zhuǎn)換器,是實(shí)現(xiàn)設(shè)計(jì)要求的核心部分。

d.DAC轉(zhuǎn)換器部分:此部分是將系統(tǒng)輸出的數(shù)字量轉(zhuǎn)換成模擬量并輸出,把前面的DDS定義為本系統(tǒng)的軟件核心,而DAC轉(zhuǎn)換器則是本系統(tǒng)的硬件核心部分。

e.功能按鍵:這部分的作用是提供給用戶所使用的,用以控制和改變輸出波形的形式以及輸出頻率。

1.2 FPGA基本性能與結(jié)構(gòu)

微電子技術(shù)在不斷進(jìn)步發(fā)展的同時,可編程邏輯器件得到了飛速的發(fā)展,相比于門陣列和其他ASIC(Application Specific Integrated Circuit),F(xiàn)PGA擁有靈活的體系結(jié)構(gòu)和邏輯單元、同時還兼有集成度高和適用范圍寬、研發(fā)單位時間短,成本低廉、選用的開發(fā)工具比較領(lǐng)先、能夠?qū)崟r在線檢驗(yàn)等優(yōu)點(diǎn)。

FPGA器件組成十分復(fù)雜,內(nèi)部擁有大量邏輯宏單元。依靠FPGA器件完成不同的功能需要配置好內(nèi)部的邏輯宏單元,將這些不同的邏輯宏單元合成不同的硬件結(jié)構(gòu),以此進(jìn)一步地構(gòu)成各種各樣的電子系統(tǒng)。FPGA擁有無可比擬的一大優(yōu)勢便是其硬件重構(gòu)具有很高的靈活性,借助這一優(yōu)勢設(shè)計(jì)者可以使用硬件描述語言(VHDL、Verilog等)在FPGA中實(shí)現(xiàn)所描述的電路。

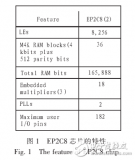

本設(shè)計(jì)所使用的是Cyclone系列中的EP1C3T100C8N,Cyclone系列器件是ALTERA公司的一款成本低、高性價比的FPGA器件,它的結(jié)構(gòu)和工作原理在FPGA器件中具有典型性。

Cyclone器件主要由邏輯陣列塊LAB、嵌入式存儲器塊、I/O單元、嵌入式硬件乘法器和PLL等模塊構(gòu)成,在各個模塊之間存在著豐富的互連線和時鐘網(wǎng)絡(luò)。Cyclone器件中所含的嵌入式存儲器可以通過多種連線與可編程資源實(shí)現(xiàn)連接和大大增強(qiáng)了FPGA的性能,擴(kuò)大了FPGA的應(yīng)用范圍。

1.3 DDS基本原理

DDS(Direct Digital Synthesizer),它具備了以往相關(guān)技術(shù)所不具備的許多特點(diǎn),它的頻率分辨率較高,這保證了它在運(yùn)行過程中能夠進(jìn)行快速的頻率轉(zhuǎn)換,與此同時它還能保持住相位的穩(wěn)定性和連續(xù)性,因此更加容易獲得信號頻率、相位變化以及震蕩幅度調(diào)制的數(shù)字控制。下面以正弦波信號發(fā)生器為例說明。

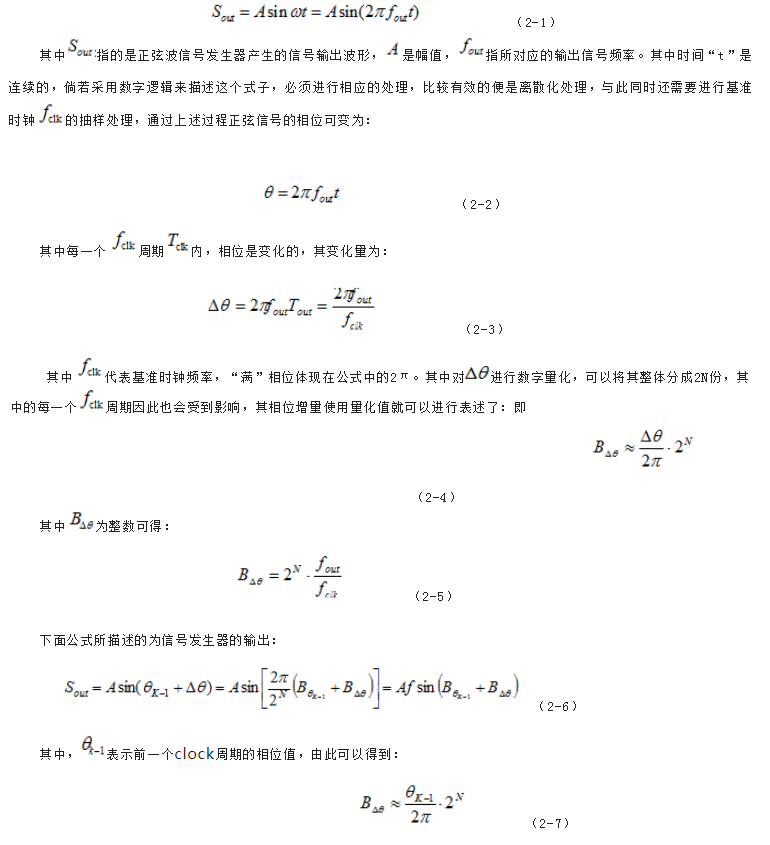

通過上面的步驟原理,可以借助于DDS直接數(shù)字合成技術(shù)設(shè)計(jì)并且實(shí)現(xiàn)所需要的數(shù)控頻率合成器。DDS直接數(shù)字合成器是用數(shù)字控制方式生成所要求的信號頻率、相位變化以及震蕩幅度等等的正弦波,同時還可以對其進(jìn)行有效地控制,典型的DDS直接數(shù)字頻率合成器由許多不可或缺的部分組成,有相位調(diào)制器、相位累加器、ROM正弦查找表和D/A數(shù)模轉(zhuǎn)換構(gòu)成,其結(jié)構(gòu)如圖1-2所示。

2 系統(tǒng)硬件與軟件的設(shè)計(jì)

2.1 鎖相環(huán)設(shè)計(jì)

鎖相環(huán)(phase locked loop),顧名思義,就是鎖定相位的環(huán)路。鎖相環(huán)(PLL)能提供先進(jìn)的時鐘管理能力,例如頻率合成、可編程相移、可編程占空比、時鐘倍頻、分頻等完整的時鐘管理方案。在本設(shè)計(jì)中除了是給整個系統(tǒng)提供工作時鐘信號,還有一個非常重要的作用,決定了本設(shè)計(jì)最終輸出波形的頻率大小,以及頻率分辨率。

2.2 ROM設(shè)計(jì)

本設(shè)計(jì)的最終結(jié)果得到正弦、方波、三角波的輸出信號,這個過程是通過將數(shù)字量通過DAC轉(zhuǎn)換器不斷的轉(zhuǎn)換來完成。因此需要事先將這些波形的的數(shù)字量數(shù)據(jù)存在ROM模塊中,以便系統(tǒng)讀取波形數(shù)據(jù)。通過定制波形數(shù)據(jù)文件來設(shè)計(jì)出需要的正弦波ROM模塊、方波ROM模塊和三角波ROM模塊。

2.3 D/A數(shù)模轉(zhuǎn)換電路

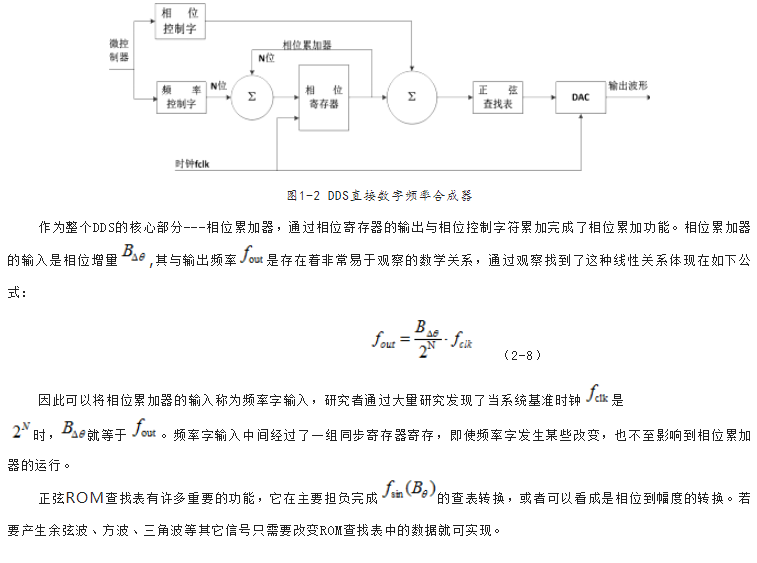

采用非常普遍的8位D/A轉(zhuǎn)換器DAC0832作為數(shù)模轉(zhuǎn)換芯片。其轉(zhuǎn)換時間為1us,工作電壓為+5V~+15V,基準(zhǔn)電壓為+15V。它主要由兩個8位寄存器和一個8位D/A轉(zhuǎn)換器組成。

圖2-1 低速DAC0832數(shù)模轉(zhuǎn)換電路

2.4 電源電路設(shè)計(jì)

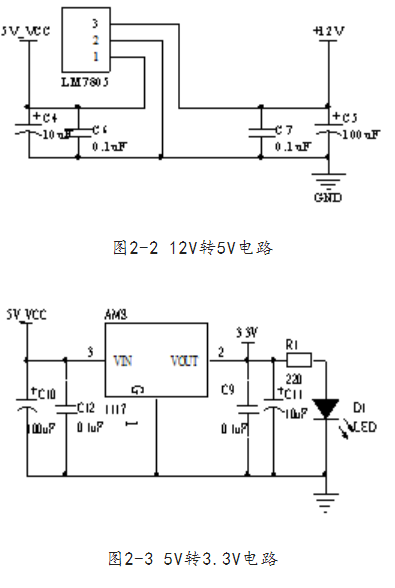

由于系統(tǒng)中各個模塊用到的電壓不同,所以就需要對電壓進(jìn)行轉(zhuǎn)換。外接12V電源,通過轉(zhuǎn)換電路來實(shí)現(xiàn)各個系統(tǒng)所需要的電壓,轉(zhuǎn)換電路如下圖所示。

2.5軟件設(shè)計(jì)

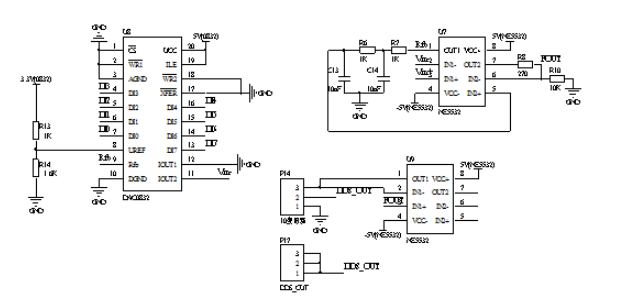

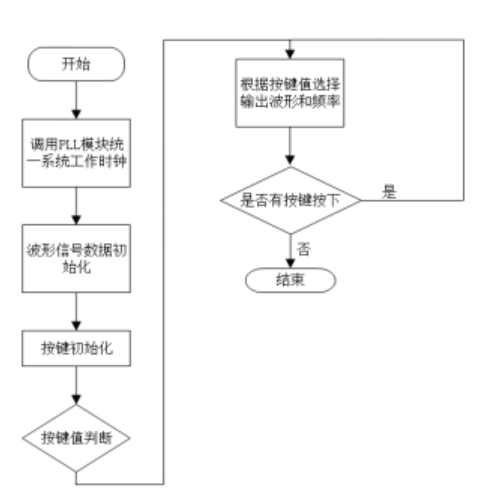

本設(shè)計(jì)通過Quartus II軟件對FPGA主控進(jìn)行編程配置,實(shí)現(xiàn)了用按鍵控制輸出的波形和頻率,程序流程圖如圖2-4所示。

圖2-4 程序流程圖

3 誤差分析

3.1相位截斷誤差分析

本設(shè)計(jì)相位累加器設(shè)定為32位,正弦表數(shù)據(jù)為8位,因此在ROM查找表里的容量為232×8=34,359,738,368(bits),在理論上這可以獲得精細(xì)的頻率分辨率,但是這么大容量的數(shù)據(jù)卻很難實(shí)現(xiàn)。所以,在本設(shè)計(jì)中的DDS中采用了相位截斷法,只用了相位累加器輸出的高10位作為地址對ROM查找表進(jìn)行查表,其他低位的地址就簡單的舍棄了。查表時相位值就會出現(xiàn)誤差,使得最后輸出波形的幅度值產(chǎn)生誤差,就會有很多的雜散信號存在。

3.2電源噪聲誤差

由于電源部分存在多種電壓值,相互間有一定的干擾,會造成輸出波形一定的失真。因此對電源的穩(wěn)定性有更高的要求,可以對數(shù)字地和模擬地隔開,降低對輸出波形的影響。

3.3后級運(yùn)放誤差分析

數(shù)字量經(jīng)數(shù)模轉(zhuǎn)換器轉(zhuǎn)換后信號經(jīng)過集成運(yùn)放放大后輸出,會有一定的失真。因?yàn)榧蛇\(yùn)放自身會存在一些不可避免的因素,如:輸入電壓失調(diào),輸入電流失調(diào)、增益帶寬積、上長速度限制。這會導(dǎo)致,當(dāng)輸入較高的頻率時,產(chǎn)生相位失真。雖然這些誤差是系統(tǒng)自身的,不可避免,但是只要通過給予合適的頻率控制字,相位累加器位數(shù)、查找表地址位數(shù)以及控制好系統(tǒng)時鐘頻率和盡量使用高品質(zhì)的電源,盡量提高濾波器的性能,輸出的波形還是能夠很好的滿足使用者的需要。

4 結(jié)論

本設(shè)計(jì)提出了一種基于FPGA信號發(fā)生器的設(shè)計(jì)方法,以Quartus II為軟件開發(fā)平臺,以EP1C3T100C8N器件為硬件平臺,采用Verilog HDL硬件描述語言進(jìn)行編程,將DDS直接頻率合成技術(shù)實(shí)現(xiàn)在FPGA器件上,通過數(shù)模轉(zhuǎn)換電路,將系統(tǒng)輸出的數(shù)字信號轉(zhuǎn)換為模擬信號,實(shí)現(xiàn)信號頻率范圍在0.02~1MHz的正弦波、方波和三角波的產(chǎn)生,并且可以通過按鍵對正弦波、方波和三角波進(jìn)行切換。

參考文獻(xiàn):

[1] 阮圍.基于 FPGA 的 DDS 設(shè)計(jì)[D].成都:成都理工大學(xué),2011.

[2] 陳科,葉建芳,馬三涵.基于DDS+PLL技術(shù)頻率合成器的設(shè)計(jì)與實(shí)現(xiàn)[J].研究與開發(fā), 2010,29(4):43~47.

[3] 韓軍功.基于 DDS 的任意波形發(fā)生器的研制[D].西安:西安電子科技大學(xué),2002.

[4] 潘松,黃繼業(yè).EDA與VHDL語言[M].科學(xué)出版社,2005:57—68.

[5] 張志剛.FPGA與SOPC設(shè)計(jì)教程—DE2實(shí)踐[M].西安電子科技大學(xué)出版社.2007:30~38.

-

FPGA

+關(guān)注

關(guān)注

1626文章

21678瀏覽量

602047 -

寄存器

+關(guān)注

關(guān)注

31文章

5325瀏覽量

120054 -

信號發(fā)生器

+關(guān)注

關(guān)注

28文章

1456瀏覽量

108663 -

相位累加器

+關(guān)注

關(guān)注

0文章

10瀏覽量

9181

發(fā)布評論請先 登錄

相關(guān)推薦

如何利用FPGA設(shè)計(jì)DDS信號發(fā)生器?

怎么實(shí)現(xiàn)基于FPGA+DDS的正弦信號發(fā)生器的設(shè)計(jì)?

怎么實(shí)現(xiàn)信號發(fā)生器系統(tǒng)的FPGA設(shè)計(jì)?

基于FPGA 的數(shù)字移相信號發(fā)生器設(shè)計(jì)

基于FPGA數(shù)字移相信號發(fā)生器設(shè)計(jì)

基于FPGA的信號發(fā)生器設(shè)計(jì)

iBoard教程之(dds信號發(fā)生器)任意波發(fā)生器硬件電路分析

基于FPGA和PWM的多路信號發(fā)生器設(shè)計(jì)

基于FPGA的DDS信號發(fā)生器設(shè)計(jì)方案解析

基于fpga實(shí)現(xiàn)信號發(fā)生器

基于FPGA的信號發(fā)生器系統(tǒng)結(jié)構(gòu)分析

信號發(fā)生器的組成結(jié)構(gòu)和應(yīng)用

文氏橋信號發(fā)生器的工作原理和結(jié)構(gòu)

基于FPGA的信號發(fā)生器系統(tǒng)結(jié)構(gòu)分析

基于FPGA的信號發(fā)生器系統(tǒng)結(jié)構(gòu)分析

評論