電子發燒友網報道(文/李寧遠)傳統的線性穩壓器輸出電壓條件很嚴苛,這才有了LDO類的電壓轉換芯片的誕生。在LDO的選擇和設計上,常常令人犯難。首先我們不僅要考慮輸入電壓的類型和范圍,例如穩壓器前面的DC/DC變換器或者開關電源的輸出電壓。其他需要考量的因素也不少,輸出電壓、最大負載電流、最小壓差、靜態電流以及功耗等等。

LDO和DC/DC的抉擇

眾所周知DC/DC轉換器的優點在于效率高、大電流輸出、小靜態電流。隨著器件的集成度越來越高,不少新型的DC/DC轉換器僅需要幾只外接電感器和濾波電容器即可。美中不足的是這一類電源控制器的輸出脈動和開關噪聲偏大,成本也相對偏高。LDO需要的外接元件也不多,一般只需要一到兩個旁路電容即可。相比DC/DC器件,LDO壓降低、噪聲低、成本也更低。 二者因為工作原理的不同,從效率上來說,DC/DC的效率會普遍的高于LDO。如果輸入電壓和輸出電壓很接近,那么LDO穩壓器也能達到很高的效率;但如果并不接近,壓降太大,消耗在LDO上的能量會增加不少,影響效率,這時候就需要考慮開關型DC/DC了。 效率只是一方面,DC/DC因為開關頻率的原因,電源噪聲會很大,而且遠比LDO大得多。一旦涉及比較敏感的模擬電路,這時候就有必要犧牲效率來保證電源的純凈。尺寸也是在二者之間權衡時需要取舍的,DC/DC需要的外圍器件例如電感、二極管、電容自不用說,有的還會需要MOSFET,在外圍器件的選擇上比LDO復雜了太多同時尺寸也會更大。

旁路電容與LDO相輔相成

上面說到,LDO需要的外接元件也不多,一般只需要一到兩個旁路電容即可。雖然簡單,但是旁路電容卻十分重要。旁路輸出電容自帶的寄生等效串聯電阻(ESR)會直接影響LDO控制環路的穩定性。

(超低壓降穩壓器,TI) 寄生等效串聯電阻(ESR)在LDO環路中添加一個零點的同時引入一個極點。當旁路電容寄生等效串聯電阻較高時,會將零點轉移至較低的頻率,增大環路帶寬導致極點增加更多的相移造成環路不穩定,表現為LDO產生振蕩。LDO可以與很多小型的陶瓷電容配合使用,前提是這些電容的寄生等效串聯電阻(ESR)足夠低。一般為了保證LDO控制環路的穩定性,電容至少1μF且寄生等效串聯電阻最大不超過1Ω。 另外輸出電容會影響調節器對負載電流變化的響應,因為控制環路的大信號帶寬有限,輸出電容需要能夠提供快速瞬變所需的絕大部分負載電流。因為電容可采用的電介質各不相同,其特性在直流表現上也不盡相同。有些直流偏置特性不佳的電介質就不適合與LDO一起使用。

噪聲如何抑制?

LDO的噪聲來源分為內部噪聲與外部噪聲,內部噪聲可能來自電路的帶隙基準源、放大器以及晶體管。器件這一部分抑制噪聲通常不會表明在器件手冊中,數據表中的PSRR是LDO抑制來自輸入的外部噪聲能力。

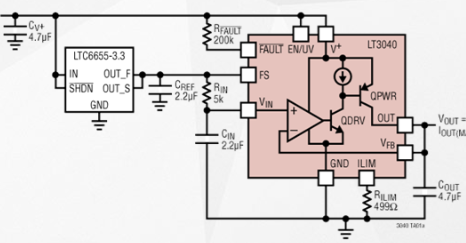

(超低噪聲LDO設計,ADI) 為了抑制這種內部噪聲,如果選擇降低誤差放大器的帶寬,這樣雖然可以有效地降低帶隙基準源的高頻噪聲,但是降低的帶寬一定會使LDO的動態性能降低。如果不希望LDO的動態性能降低,可以在帶隙基準源和誤差放大器之間加低通濾波,也可以在反饋電阻上增加前饋電容。 外部噪聲的抑制更多的需要LDO在內部設計上做文章,也可以通過增加額外的濾波器/旁路電容來減小噪聲。不過考慮到增加額外器件會增加成本與體積,合理且靈活的內部設計更重要一些。

小結

用于模擬和射頻負載的LDO一般看重低噪聲和高電源抑制能力,器件需要能夠抑制住上游電源和下游負載的噪聲,而且自身不增加噪聲。這和模擬器件對噪聲更敏感有關。而LDO用于數字負載尤其看重功耗,對噪聲的要求就沒有那么嚴格,為了響應軟件導致的負載變化而發生的時鐘頻率變化對LDO的負載調整能力提出了非常嚴格的要求,這需要注意。 總的來看,如果DC輸入電壓是由經整流的AC電源提供,那么標準穩壓器可能是更好的選擇,畢竟成本低而且負載電流大;如果需要低功耗的精密輸出電壓,那LDO無疑是更合適的選擇。

-

轉換器

+關注

關注

27文章

8639瀏覽量

146894 -

電容

+關注

關注

99文章

6001瀏覽量

150039 -

噪聲

+關注

關注

13文章

1118瀏覽量

47372 -

ldo

+關注

關注

35文章

1919瀏覽量

153190 -

DCDC

+關注

關注

29文章

808瀏覽量

71126

原文標題:LDO電容與噪聲,如何在LDO與DC/DC中選擇

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

在LDO與DC/DC中怎么選擇 LDO電容與噪聲怎么考量

在LDO與DC/DC中怎么選擇 LDO電容與噪聲怎么考量

評論