在 2019 年初,英特爾終于公開承認(rèn)他們搞砸了——他們雄心勃勃的 10 納米工藝失敗了。這主要?dú)w因于其瘋狂的密度改進(jìn)目標(biāo)以及太多新穎的技術(shù)特征證明。伺候,該公司承諾通過更平衡的 PPA 和衡量的風(fēng)險(xiǎn)承擔(dān)恢復(fù)到更規(guī)律的節(jié)點(diǎn)更新節(jié)奏來糾正這一問題。歷經(jīng)兩次的CEO 更換,在 Gelsinger 的監(jiān)督下,我們終于看到了芯片巨頭為重回正軌所做的一些努力。

在本周早些時(shí)候在夏威夷舉行的 2022 年 IEEE VLSI 技術(shù)和電路研討會上,英特爾展示了許多涉及其英特爾 4 工藝的論文。這些論文主要由英特爾公司技術(shù)開發(fā)副總裁 Ben Sell 發(fā)表。

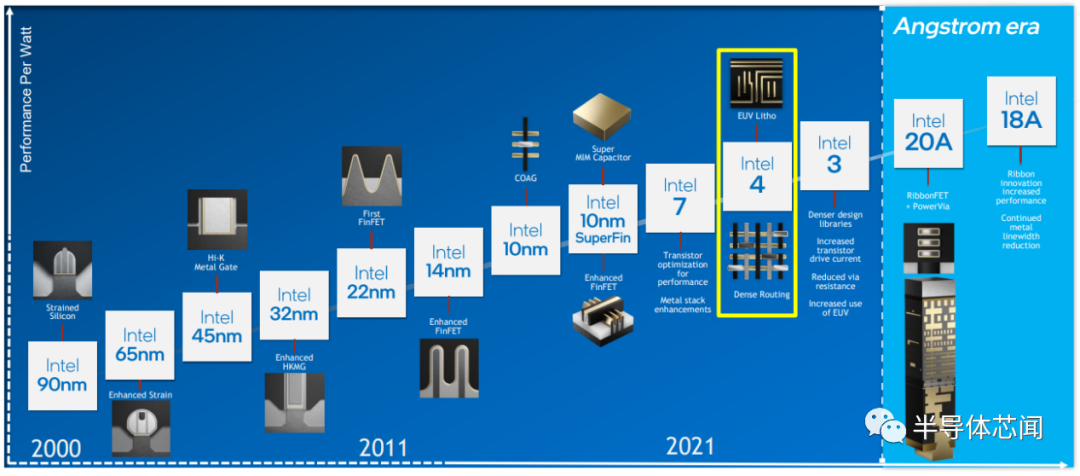

這個(gè)新節(jié)點(diǎn)稱為 Intel 4。出于所有實(shí)際目的,它是適當(dāng)?shù)?10 納米繼任者。換句話說,如果它在 2020 年發(fā)布,它應(yīng)該被正確地稱為“7nm”。今天,它被稱為“Intel 4”,是“Intel 7”(以前稱為“10nm Enhanced SuperFin”,以前稱為“10nm++”)的繼任者。

Intel 4 很好但很奇怪,真的很奇怪。在時(shí)間方面,英特爾預(yù)計(jì)這一制程將在今年晚些時(shí)候加速——這意味著會是明年產(chǎn)品使用的工藝。如果一切按計(jì)劃進(jìn)行,Intel 4 的繼任者“Intel 3”將在幾乎整整一年之后(2023 年底開始升級)。這應(yīng)該開始讓您了解英特爾如何看待這個(gè)制程。

在深入研究細(xì)節(jié)之前,我們想強(qiáng)調(diào)一下Intel 4 并非設(shè)計(jì)為一個(gè)典型的成熟(full-fledged)節(jié)點(diǎn)。雖然它是一個(gè)高容量(high-volume )節(jié)點(diǎn),但它可以在其上制作的內(nèi)容非常有限(因此可能會大大限制其容量)。例如。它不會提供許多您通常會從英特爾節(jié)點(diǎn)看到的大型庫,例如高密度和中檔性能密度庫,這些庫對圖形和其他應(yīng)用程序等事物很重要,但對 CPU 核心設(shè)計(jì)來說,這并不重要。

從這個(gè)角度看,英特爾的這個(gè)節(jié)點(diǎn)是為為那些想把使用不同工藝的chiplet合封到一起的compute tile而準(zhǔn)備的。

從小處著手,讓它發(fā)揮作用,建立起來

Intel 4 代表了公司處理其節(jié)點(diǎn)設(shè)計(jì)方式的范式轉(zhuǎn)變。 從歷史上看,該公司專注于推出傳統(tǒng)上所謂的全節(jié)點(diǎn)——大約每兩年推出一個(gè)節(jié)點(diǎn),帶來整整一代的改進(jìn)。代工廠(例如,臺積電以及十年前的富士通、東芝、NEC 等)過去常常引入稱為半節(jié)點(diǎn)的后續(xù)節(jié)點(diǎn),這將進(jìn)一步改進(jìn)節(jié)點(diǎn)以及較小的間距縮放。 前提很簡單:擴(kuò)展和增強(qiáng)現(xiàn)有的高收益節(jié)點(diǎn)既便宜又容易。 而傳統(tǒng)的“全節(jié)點(diǎn)”和“半節(jié)點(diǎn)”模型被淘汰了。隨著最近 FinFET 節(jié)點(diǎn)的復(fù)雜性激增,代工廠轉(zhuǎn)向新的“nodelet”方案。在此模型下,首先引入一個(gè)基本節(jié)點(diǎn)(例如,7LPP 或 N7),然后由一個(gè)或多個(gè)增強(qiáng)節(jié)點(diǎn)(nodelet)接替,幾乎每年都會帶來微小但增量的變化(例如,N7P、N7+、 N6,6LPP)。 快速接替Intel 4 的是Intel 3,預(yù)計(jì)將在明年年底推出。該公司表示,該制程將引入新的庫,在密度、功率和性能方面都比Intel 4 有所提高。此外,Intel 4 與Intel 3 向前兼容,使設(shè)計(jì)遷移更容易。更重要的是,Intel 3 將擁有完整的代工產(chǎn)品。 在許多方面可以看出,英特爾都在借鑒代工手冊。很明顯,他們正在限制Intel 4 特性和功能的復(fù)雜性以降低風(fēng)險(xiǎn)。此外,他們今年推出 Intel 4 的能力將對他們明年按時(shí)將 Intel 3 推向市場的能力發(fā)揮重要作用,而正確執(zhí)行是最重要的。他們的目標(biāo)是構(gòu)建更廣泛、改進(jìn)的功能組合、庫、和其他 IP ,這在成熟的制程中要容易得多,并且這是解決此問題的正確方法。鑒于Intel 3 被定位為英特爾代工服務(wù) (IFS) 的初始旗艦節(jié)點(diǎn),這一點(diǎn)至關(guān)重要。 由于Intel 4 的范圍有限,并且其快速跟進(jìn)的成熟Intel 3 節(jié)點(diǎn)具有全節(jié)點(diǎn)密度/PPA 特性,我們認(rèn)為最好將Intel 4 視為臨時(shí)權(quán)宜之計(jì)節(jié)點(diǎn)。

產(chǎn)品

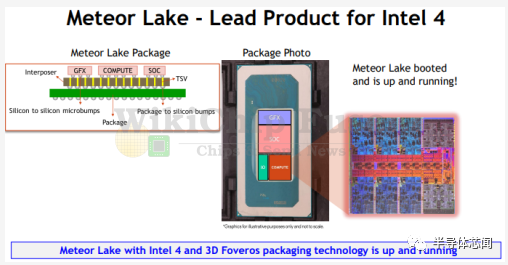

最初,英特爾透露 Meteor Lake 客戶端 SoC 和 Granite Rapids 數(shù)據(jù)中心 SoC 都將在Intel 4 工藝上制造。然而,在今年早些時(shí)候的公司 2022 年投資者會議上,該公司宣布Granite Rapids的制造工藝將從Intel 4 升級到Intel 3 制程。出于我們今天對Intel 4 和Intel 3 之間關(guān)系的了解,這種切換對于Granite Rapids來說更有意義。 在諸如 IEEE VLSI Symposium 等技術(shù)會議上,英特爾通常將其演講的范圍僅限于其工藝的技術(shù)方面。在這個(gè)相當(dāng)罕見和不尋常的場合,Sell 談到了即將推出的第一款 Intel 4 產(chǎn)品——Meteor Lake。采用 Intel 4 的 Meteor Lake 將成為 3D foveros 封裝技術(shù)的量產(chǎn)產(chǎn)品。Intel 4 支持最新的封裝技術(shù),并為 Foveros 提供了更激進(jìn)的微凸點(diǎn)間距——從 50μm 擴(kuò)展到 36μm。Meteor Lake 包含一個(gè)圖形tiles、SoC tiles、計(jì)算tiles和 I/O tiles,所有這些都位于一個(gè) Si 中介層上。Meteor Lake 封裝和 die shot 如下所示。

制程概述

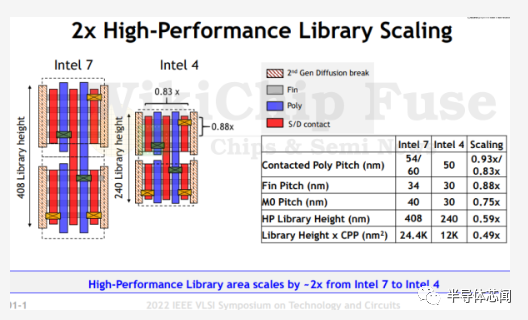

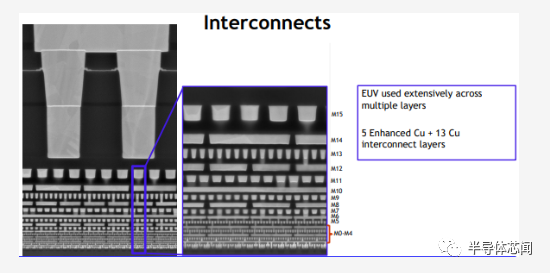

Intel 4(連同其增強(qiáng)版 Intel 3)是 Intel 最后一個(gè)基于 FinFET 的節(jié)點(diǎn)。在高層次上,這是繼 22nm、14nm 和 10nm 之后第四個(gè)使用 FinFET 的主要節(jié)點(diǎn)。據(jù)說該工藝?yán)昧说诙?COAG 和第二代單虛擬門( single dummy gate)。英特爾聲稱新的Intel 4 工藝為高性能庫提供了大約 2 倍的面積擴(kuò)展。最后,值得強(qiáng)調(diào)的是,這是該公司的首個(gè) EUV 支持的工藝,有望顯著簡化工藝。

極紫外 (EUV) 光刻

自對準(zhǔn)四邊形圖案 (SAQP)

有源柵極接觸 (COAG)

單虛擬門 (SDB)

增強(qiáng)型銅互連

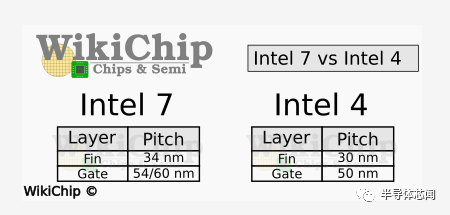

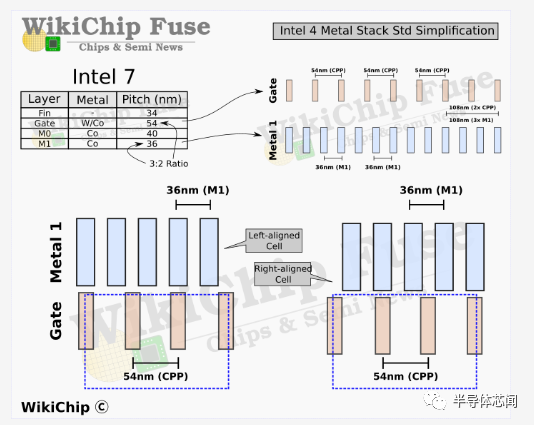

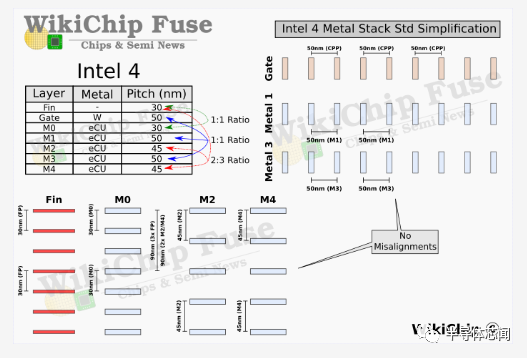

在晶體管級別,各種間距適度縮小。例如,與 Intel 7 相比,Intel 4 的鰭片間距為 30 納米,柵極間距為 50 納米,分別縮小了 0.83 倍和 0.88 倍。互連堆棧經(jīng)歷了一些更重要的變化,包括材料變化。例如,M0 金屬間距經(jīng)歷了較大的間距從 40 nm 縮小到 30 nm 或 0.75 倍。 在進(jìn)一步討論之前,我們想重申一下,由于使用該節(jié)點(diǎn)的產(chǎn)品有限,Intel 4 將僅提供高性能單元庫。通常,英特爾至少為邏輯設(shè)計(jì)了三個(gè)標(biāo)準(zhǔn)庫。例如,使用英特爾 10nm,該公司擁有高密度單元、高性能/移動性能單元和超高性能單元。雖然它們使用相同的底層晶體管,但它們的特點(diǎn)是性能、功率和密度特性是 pMOS 和 nMOS 器件的函數(shù)。對于 FinFET 器件,這是鰭片數(shù)量的直接函數(shù)。因此,英特爾 10nm 具有每個(gè)器件可容納 2 個(gè)鰭的 HD 單元、每個(gè)器件可容納 3 個(gè)鰭的 HP 單元和每個(gè)器件可容納 4 個(gè)鰭的 UHP 單元。

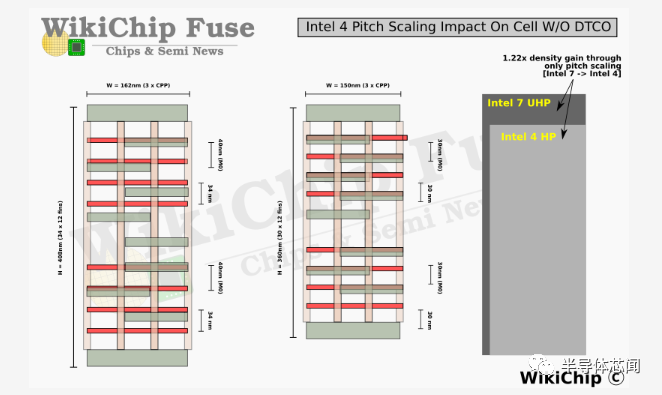

擴(kuò)展(Scaling)是 DTCO-Heavy

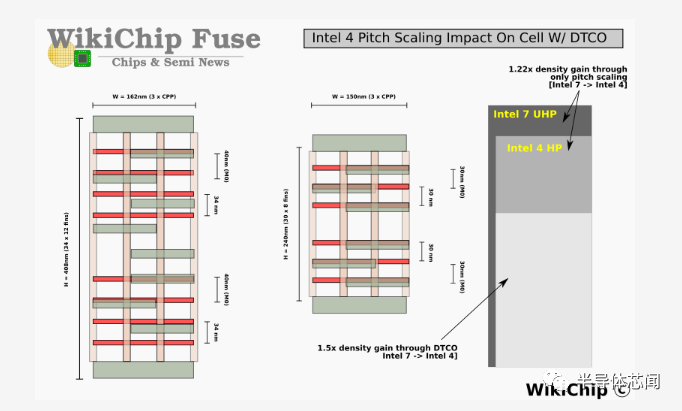

正如我們在過去幾個(gè)節(jié)點(diǎn)中看到的那樣,PPA 目標(biāo)現(xiàn)在在很大程度上都涉及 DTCO。Intel 4 也不例外。事實(shí)上,如果我們將intel 7 單元轉(zhuǎn)移到intel 4 上并僅調(diào)整間距,我們將獲得 1.22 倍的晶體管密度改進(jìn)或大約 0.82 倍的縮放。這意味著,DTCO 不是pitch 縮放,而是intel 4 中密度改進(jìn)的絕大部分。

許多關(guān)鍵技術(shù)在這里發(fā)揮作用。 首先,intel 4 使用第二代 COAG 和第二代單虛擬門,允許它們隨著新的柵極和鰭片間距進(jìn)行擴(kuò)展,同時(shí)保持單元高度和單元寬度的優(yōu)勢,從而實(shí)現(xiàn)我們在intel 7 中看到的密度改進(jìn)。以前,英特爾在 nMOS 和 pMOS 器件之間的區(qū)域(柵極輸入的前接觸區(qū)域)有兩條擴(kuò)散線(diffusion lines)的間距。Intel 4 利用了單元的這一區(qū)域并消除了其中一條擴(kuò)散線,從而縮短了單元高度并獲得了寶貴的空間。我們估計(jì)僅此一項(xiàng)就產(chǎn)生了大約 11.5% 的面積縮放。 最后,由于其更高的性能,intel 4 經(jīng)歷了 4:3 的鰭片減少。這是對整體面積額外縮小 25% 的最大貢獻(xiàn)。總而言之,DTCO 在傳統(tǒng)pitch縮放的基礎(chǔ)上增加了 1.5 倍的縮放。這證明了 DTCO 在現(xiàn)代前沿節(jié)點(diǎn)中的重要性,以及 STCO 將如何在引入未來技術(shù)(如埋入式電源軌和背面供電網(wǎng)絡(luò))中發(fā)揮更大的作用。

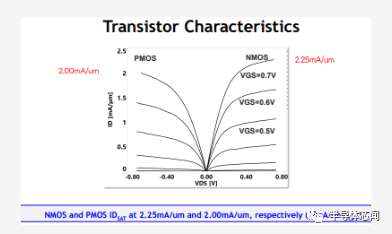

為了促進(jìn)鰭的減少,必須增強(qiáng)設(shè)備性能。對于 Intel 4,該公司報(bào)告稱,nMOS 和 pMOS 的驅(qū)動電流均超過每微米 2mA。對于 0.7 V 的 nMOS,驅(qū)動電流為每微米 2.25 mA,漏電流為每微米 20 nA。同樣,對于 pMOS,在相同泄漏情況下,每微米的驅(qū)動電流為 2 mA。這些數(shù)字代表了比 10 納米設(shè)備大約 25-30% 的改進(jìn)。

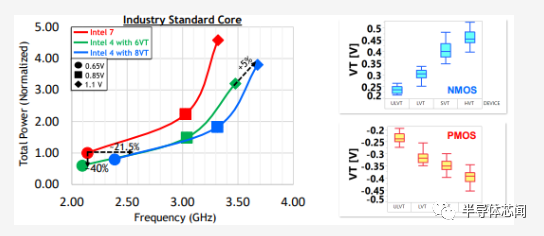

Intel 4 提供 8 個(gè)閾值(threshold )電壓器件 (4 nMOS / 8 pMOS)。與 Intel 7 相比,這些新設(shè)備提供了額外 5% 的功率不受限制的性能提升。

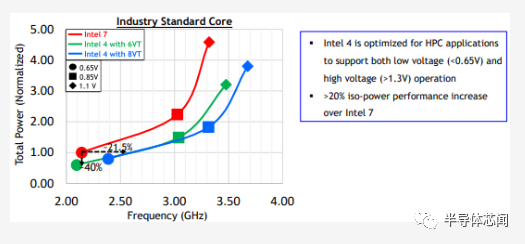

英特爾還報(bào)告了一些使用標(biāo)準(zhǔn)可授權(quán)內(nèi)核(可能是 Cortex-A7x 內(nèi)核)的功率性能數(shù)據(jù)。下面的電源頻率圖展示了在intel 7 與intel 4 上制造相同內(nèi)核的對比情況。在低電壓下,英特爾報(bào)告在等功率下的頻率比intel 7 提高了 20% 以上。或者,在相同的低電壓下,相同的內(nèi)核結(jié)果在等頻處能量減少約 40%。

密度

綜上所述,英特爾表示,根據(jù)內(nèi)部估計(jì),他們看到從intel 7 到intel 4 的完整高性能庫擴(kuò)展為 2 倍。

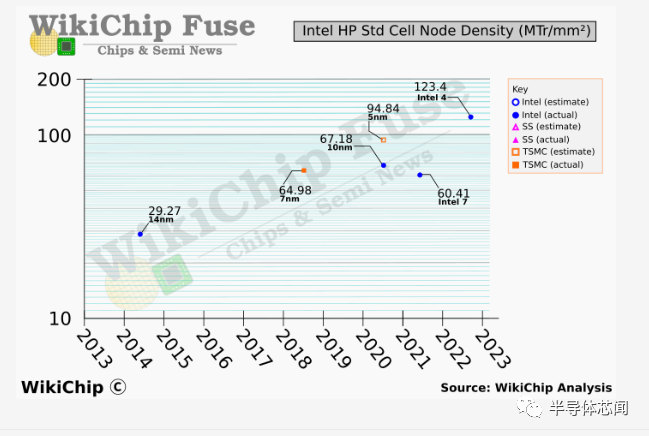

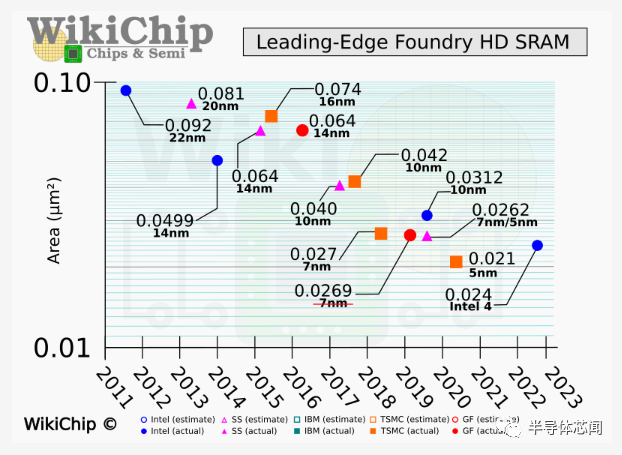

像往常一樣,WikiChip 根據(jù)當(dāng)前公開的代工數(shù)據(jù)生成自己的獨(dú)立估計(jì)。 我們自己的估計(jì)表明,intel 4 的密度比英特爾 7/10nm 提高了 1.83 倍。但是,我們的估計(jì)還表明,intel 4 提供的密度比intel 7 提高了 2.04 倍。這是怎么算出來的?答案實(shí)際上在英特爾自己的 VLSI 演示幻燈片中。 隨著 10 納米 SuperFin 及其后繼產(chǎn)品增強(qiáng)型 SuperFin(現(xiàn)在稱為 Intel 7)的推出,英特爾推出了一種具有 60 納米多晶間距的新型晶體管,以實(shí)現(xiàn)更高的驅(qū)動電流性能。在生產(chǎn)性能顯著提高的晶體管的同時(shí),它的不利影響是將邏輯密度降低了 0.9 倍。值得注意的是,這些cell被用于Alder Lake中的 Golden Cove 和 Gracemont 核心。 為此,我們估計(jì)intel 4 密度為 123.4 MTr/mm2,是英特爾 7 中 60.5 MTr/mm2 的 2.04 倍。我們對 TSMC N5 的數(shù)據(jù)非常不完整,但我們基于已知間距的粗略估計(jì)將其 HP 庫為 94.85 MTr/平方毫米。根據(jù)最近公開的大多數(shù)代工數(shù)據(jù),intel 4 HP 單元似乎比 TSMC N5 HP 更密集,并且可能更接近或優(yōu)于 TSMC N3 HP 單元,并且比三星的 3GAE 更密集。鑒于過去三年 10nm 對公司造成的動蕩,以這樣的數(shù)字出現(xiàn)是相當(dāng)令人驚訝的。它還強(qiáng)烈表明intel 3 可以匹配并超越即將推出的 3nm 級代工產(chǎn)品。

以匹配并超越即將推出的 3nm 級代工產(chǎn)品。

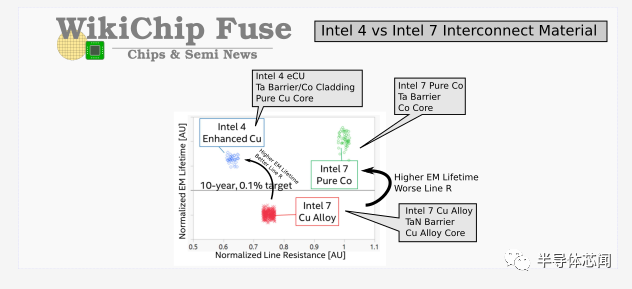

互連

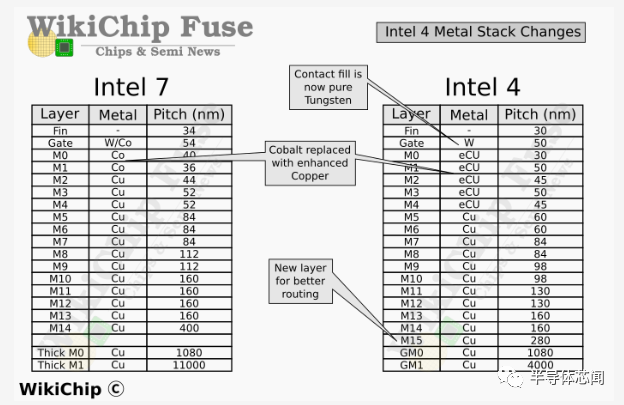

Intel 4 互連堆棧經(jīng)歷了相當(dāng)大的變化。

Intel 4 的基本設(shè)計(jì)規(guī)則的一個(gè)亮點(diǎn)如下所示,與具有 17 個(gè)金屬層的 Intel 7 相比,Intel 4 增加了一層。M4 上方的大多數(shù)互連都看到了通常的間距縮小,其中大部分在 0.7x-0.85x 縮放左右。與之前的節(jié)點(diǎn)一樣,兩個(gè)頂層是厚金屬層。與大多數(shù)其他wires相比,英特爾大幅縮小了最后一層厚金屬層。最受關(guān)注的區(qū)域是前四個(gè)路由層(routing layers)。在那里,不僅某些間距沒有縮小,有些實(shí)際上變寬了。這些層也經(jīng)歷了新的材料變化。

盡管英特爾沒有詳細(xì)說明確切的層,但 EUV 和 SAQP 都以最緊密的間距使用。此外,使用單一鑲嵌(damascene )工藝來形成 M0 軌道的觸點(diǎn),這可能有助于在該步驟中形成 EUV 圖案。

四個(gè)最低金屬層在兩個(gè)正交方向上橫跨芯片,用于cell本地電源和路由。在 Intel 4 中,它們具有非常規(guī)則的pitches。為什么有些間距縮小而其他間距變寬似乎有一個(gè)很好的理由,這主要與單元布局優(yōu)化有關(guān)。 在 Intel 7 中,M1 層非常激進(jìn)的鰭片間距意味著該公司采用了 3:2 的間距比。這有一些奇怪的副作用。在Intel 4 中,英特爾實(shí)際上將間距縮小了近 1.4 倍,以通過相同的間距將其固定到門上。正如我們將在下面展示的那樣,這不僅簡化了設(shè)計(jì),而且完全消除了布局的一些不合適。英特爾似乎對 M3 層做了同樣的事情。我們在這里的最后觀察涉及也與鰭平行的 M2 和 M4 層。這些具有2:3的比例。

正如我們之前提到的,在 Intel 7 中,該公司選擇了非常激進(jìn)的 M1 間距 ——36 nm。該軌道( track)平行于多邊形軌道。選擇該間距是為了便于金屬層和柵極間距之間的比率為 3:2。換句話說,更緊密的間距允許每個(gè)單元的每個(gè)poly有更多的 M1 軌道,這意味著更多的引腳命中位置。這種設(shè)計(jì)提供了更好的單元間連接和更好的塊級訪問。不幸的是,在 M1 處具有此比率也會導(dǎo)致一些單元級別的奇怪,其中取決于cell poly count的均勻/奇數(shù),您最終可能會得到左對齊或右對齊的單元格。解決這個(gè)問題意味著減少面積利用率。

為了簡單起見,Intel 4 顯然完全放棄了該方案。M1 和 M3 層現(xiàn)在都與poly掛鉤,完全消除了這種錯(cuò)位問題。有趣的是,該公司還將 M0 軌道固定在鰭上。那些垂直于多邊形。在 Intel 7 中具有 44nm 和 52nm 間距的上 M2 和 M4 層在 Intel 4 中都具有 45nm。從布局的角度來看,選擇 45nm 是非常清楚的,因?yàn)樗鼈儸F(xiàn)在以 2 :3的比例固定在鰭片上。請記住,由于單元格高度是一個(gè)固定屬性,因此在該方向上沒有對齊問題。

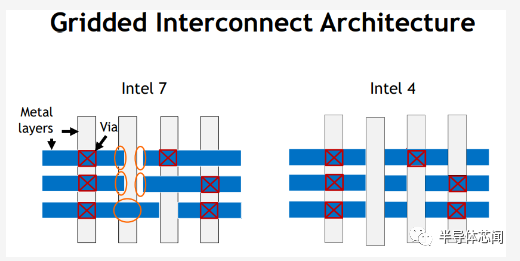

在 VLSI 上,英特爾還討論了intel 4 引入的新網(wǎng)格互連架構(gòu)。在之前的節(jié)點(diǎn)中,英特爾定義了通孔和track end caps的最小間距。但是,沒有具體說明它們的確切位置。這導(dǎo)致了大量的patterns,由于增加的patterns可變性而引入了新的分析復(fù)雜性層。在 Intel 4 中,線端和過孔現(xiàn)在嚴(yán)格放置在網(wǎng)格上,從而減少了可能的放置。據(jù)說新的簡單網(wǎng)格限制通過減少圖案可變性以及通過更好地識別問題和優(yōu)化自動布局布線 (APR) 設(shè)計(jì)流程來提高良率。

銅回來了

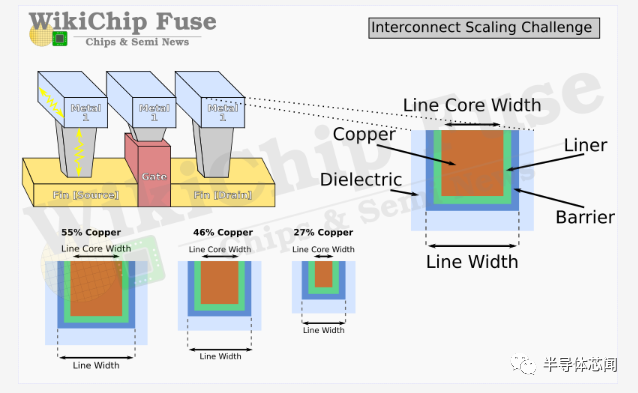

當(dāng)英特爾首次推出他們的 10 納米工藝時(shí),他們宣布推出新的互連材料——鈷。主要?jiǎng)訖C(jī)是其更好的電遷移特性。隨著我們繼續(xù)縮小互連,銅互連的高電阻率襯墊和阻擋層的厚度基本保持不變(the thickness of the high-resistivity liner and barrier for the copper interconnects stayed about the same)。這主要是由于工程上難以將其減薄到比現(xiàn)有的幾納米更小。最終結(jié)果是,隨著wires規(guī)模的提升,屏障(barrier )本身開始在互連橫截面積中占據(jù)越來越大的份額。隨著High-resistivity barriers慢慢構(gòu)成互連的大部分,它開始主導(dǎo)導(dǎo)線本身的電阻率。

、 雖然由于鈷及其更薄的襯里,在10nm工藝上,兩個(gè)局部互連層(M0 和 M1)處的wire電阻確實(shí)增加了,但英特爾報(bào)告稱線路電阻降低了 2 倍。此外,這兩層也使電遷移提高了 5-10 倍。但最終,英特爾似乎在Intel 4 中退出了鈷。鈷是一種更難使用的材料,并且被推測是導(dǎo)致其良率難以提升的根源之一。 在下圖中,英特爾展示了intel 7 與具有鉭阻擋層(Tantalum barrier )的純鈷內(nèi)核與具有氮化鉭阻擋層(Tantalum nitride barrier)的傳統(tǒng)銅合金內(nèi)核之間的關(guān)系。這兩個(gè)選項(xiàng)具有互補(bǔ)的屬性。純 Co 提供了相當(dāng)好的電遷移特性,但提供了更差的線路電阻。同樣,Cu 合金提供更好的線路電阻但更差的電遷移壽命。事實(shí)上,與純鈷相比,銅合金提供了 0.75 倍的線路電阻,這是相當(dāng)大的電阻下降。對于 Intel 4,該公司選擇在最低的四個(gè)金屬層中使用增強(qiáng)型銅 (eCu)。這種增強(qiáng)的銅線包括一個(gè)鉭阻擋層,而在純銅芯周圍也有鈷包層。

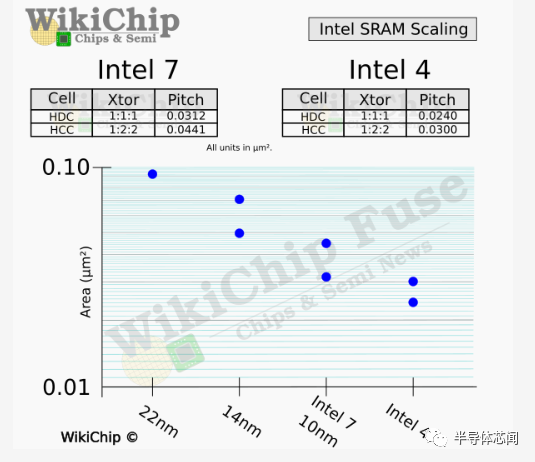

內(nèi)存

與仍然提供雙倍晶體管密度的邏輯縮放不同,內(nèi)存縮放正在面臨嚴(yán)峻挑戰(zhàn)。

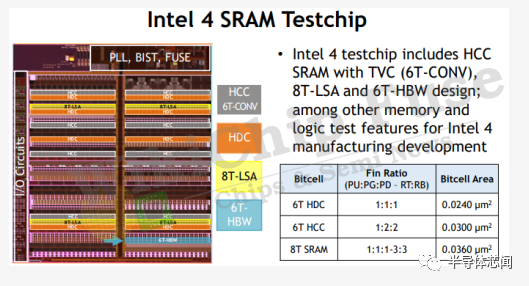

Intel 4 引入了兩個(gè)標(biāo)準(zhǔn)的 6T SRAM 單元——高密度和大電流單元。高密度 (PUPD = 11) cell從 0.0312 平方微米縮小到 0.0240,而高性能 (PUPD = 12) cell縮小到 0.0300 平方微米. 這些cell分別看到了 0.77 倍和 0.68 倍的縮放比例,這與我們過去看到的約 0.6 倍的歷史縮放比例相去甚遠(yuǎn)。除了 6T 單元之外,英特爾還開發(fā)了一個(gè) 8T SRAM 位單元,它在 6T 寫入端口的基礎(chǔ)上增加了一個(gè) 3 鰭讀取端口,總面積為 0.0360 平方微米。雖然占用 1.74 倍的面積,但它使用的讀/寫能量分別比 HDC 和 HCC 低 6 倍和 12 倍。

將Intel 4 的密度與臺積電和三星的代工產(chǎn)品進(jìn)行比較時(shí),英特爾 4 SRAM 的尺寸實(shí)際上相當(dāng)令人失望。對于我們在這里的密度估計(jì),我們使用我們的標(biāo)準(zhǔn)等輔助電路開銷方法,該方法可能與公司自己報(bào)告的數(shù)字不同。為此,intel 4 HDC 產(chǎn)生了大約 27.8 Mib/mm2 的內(nèi)存密度。與密度為 31.8 Mib/mm2 的 TSMC N5 SRAM 相比,英特爾的密度大約低 14.5%。

英特爾還展示了其intel 4 SRAM shuttle 測試芯片。test vehicle具有 57 Mib 的高密度cell和 50 Mib 的高性能cell。硅測量表明,高密度cell的 90% Vim 工作電壓(percentile Vim operation)為 0.6 V,高性能cell的工作電壓為 0.55 V。

intel 4 還改進(jìn)了intel 7 的 MIM 電容器。intel 4 上的新 MIMcap 提供了令人印象深刻的兩倍于intel 7 的電容,達(dá)到 376 fF/μm2。

結(jié)論

在經(jīng)歷了五年的制造問題折磨之后,英特爾終于出現(xiàn)了復(fù)蘇的跡象。 在 2022 年 IEEE VLSI 技術(shù)和電路研討會上,英特爾終于公布了他們的下一代領(lǐng)先的高性能工藝節(jié)點(diǎn)——intel 4。該節(jié)點(diǎn)預(yù)計(jì)將在今年年底前量產(chǎn)。雖然在功能方面不如他們通常的節(jié)點(diǎn)那么全面,但intel 4 提供了足夠的功能來支持他們的下一代客戶端 SoC(代號 Meteor Lake)所需的計(jì)算塊。該節(jié)點(diǎn)充分利用 EUV 并提供比 Intel 7 大約 20% 的性能/瓦特增益。 在 SoC 級別,該節(jié)點(diǎn)在等頻下可降低多達(dá) 40% 的功率或在等頻下提供 >20% 的頻率提升-力量。此外,該節(jié)點(diǎn)的高性能庫擁有完整的 2.04 倍密度縮放,超過intel 7 中用于 Alder Lake 的最高性能單元。在紙面上,這些 PPA 特性使公司的新intel 4 工藝的性能水平優(yōu)于臺積電 N3 和三星 3GAE。在密度方面,英特爾 4 與 N3 高性能庫相比似乎極具競爭力。 很明顯,Intel 4 是經(jīng)過精心制作的。仔細(xì)的標(biāo)準(zhǔn)單元縮放以及架構(gòu)簡化有助于降低工藝復(fù)雜性。隨著 EUV 的引入,回歸到更簡單的材料有助于大大減少掩模、步驟和圖案的可變性和復(fù)雜性。英特爾表示,與英特爾 7 相比,新節(jié)點(diǎn)還大大降低了每個(gè)晶體管的成本。 盡管如此,我們認(rèn)為英intel 4 是一個(gè)權(quán)宜之計(jì)節(jié)點(diǎn)——一個(gè)最小可行的產(chǎn)品,是通往intel 3 的中間節(jié)點(diǎn),這預(yù)計(jì)將發(fā)生在intel 4 之后大約一年(明年年底)。Intel 3 將是 Intel 的最終 FinFET 工藝。此后的一切都將使用該公司稱為 RibbonFET 的新的環(huán)柵晶體管架構(gòu)。intel 3 恰好也是英特爾代工服務(wù) (IFS) 即將推出的旗艦節(jié)點(diǎn)。intel 3 建立在intel 4 的基礎(chǔ)上,這就是為什么及時(shí)正確地將intel 4 提升到良好的良率和高產(chǎn)量如此重要的原因。該公司已經(jīng)透露,intel 3 將再提供 18% 的性能/瓦特改進(jìn),這本身就是一個(gè)全節(jié)點(diǎn)改進(jìn)。該過程還將引入一個(gè)新的更密集的高性能庫以及一組更完整的其他庫和 IP。

從本文詳述的 Intel 4 工藝,該公司能否重新獲得其在半導(dǎo)體行業(yè)的領(lǐng)先地位,完全取決于其執(zhí)行力。

審核編輯 :李倩

-

英特爾

+關(guān)注

關(guān)注

60文章

9886瀏覽量

171531 -

intel

+關(guān)注

關(guān)注

19文章

3480瀏覽量

185755 -

半導(dǎo)體行業(yè)

+關(guān)注

關(guān)注

9文章

403瀏覽量

40473

原文標(biāo)題:英特爾首個(gè)使用EUV的工藝詳解

文章出處:【微信號:iotmag,微信公眾號:iotmag】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

英特爾考慮出售Altera股權(quán)

英特爾向聯(lián)想交付首款18A工藝CPU樣品

英特爾取消Intel 20A,提前押注Intel 18A

英特爾:最新節(jié)點(diǎn)上的產(chǎn)品設(shè)計(jì)和工藝準(zhǔn)備進(jìn)展順利,已具備更早地過渡到Intel 18A的能力

英特爾1.8nm成功點(diǎn)亮!

英特爾3nm制程工藝“Intel 3”投入大批量生產(chǎn)

英特爾正在順利推進(jìn)的Intel 20A和Intel 18A兩個(gè)節(jié)點(diǎn)

新思科技與英特爾在UCIe互操作性測試進(jìn)展

英特爾宣布代工虧損70億美元

新思科技與英特爾深化合作加速先進(jìn)芯片設(shè)計(jì)

英特爾首推面向AI時(shí)代的系統(tǒng)級代工

英特爾首推面向AI時(shí)代的系統(tǒng)級代工—英特爾代工

英特爾的Intel 4工藝詳述

英特爾的Intel 4工藝詳述

評論