為什么有些CPU的主頻更低,但運(yùn)算效率卻更高呢?

比如:51單片機(jī)30M主頻,STM32單片機(jī)20M主頻,執(zhí)行相同一段代碼,主頻更低的STM32所花的時(shí)間卻更短。

這里就牽涉到CPU流水線的問(wèn)題,本文圍繞CPU流水線描述相關(guān)內(nèi)容。

早期CPU流水線

1.流水線來(lái)源

流水線的概念來(lái)源于工業(yè)制造領(lǐng)域,以汽車裝配為例來(lái)解釋流水線的工作方式,假設(shè)裝配一輛汽車需要四個(gè)步驟:

1.沖壓:制作車身外殼和底盤等部件; 2.焊接:將沖壓成形后的各部件焊接成車身; 3.涂裝:將車身等主要部件清洗、化學(xué)處理、打磨、噴漆和烘干; 4.總裝:將各部件(包括發(fā)動(dòng)機(jī)和向外采購(gòu)的零部件)組裝成車;

汽車裝配需要沖壓、焊接、涂裝和總裝四個(gè)工人,最簡(jiǎn)單的方法是一輛汽車依次經(jīng)過(guò)上述四個(gè)步驟裝配完成之后,下一輛汽車才開(kāi)始進(jìn)行裝配,最早期的工業(yè)制造就是采用的這種原始的方式,即同一時(shí)刻只有一輛汽車在裝配。

不久之后人們發(fā)現(xiàn),某個(gè)時(shí)段中一輛汽車在進(jìn)行裝配時(shí),其它三個(gè)工人都處于閑置狀態(tài),顯然這是對(duì)資源的極大浪費(fèi),于是思考出能有效利用資源的新方法,即在第一輛汽車經(jīng)過(guò)沖壓進(jìn)入焊接工序的時(shí)候,立刻開(kāi)始進(jìn)行第二輛汽車的沖壓,而不是等到第一輛汽車經(jīng)過(guò)全部四個(gè)工序后才開(kāi)始,這樣在后續(xù)生產(chǎn)中就能夠保證四個(gè)工人一直處于運(yùn)行狀態(tài),不會(huì)造成人員的閑置。這樣的生產(chǎn)方式就好似流水川流不息,因此被稱為流水線。

2.CPU流水線

1989 年推出的 i486 處理器引入了五級(jí)流水線。這時(shí),在 CPU 中不再僅運(yùn)行一條指令,每一級(jí)流水線在同一時(shí)刻都運(yùn)行著不同的指令。這個(gè)設(shè)計(jì)使得 i486 比同頻率的 386 處理器性能提升了不止一倍。

五級(jí)流水線中的取指階段將指令從指令緩存中取出(i486 中的指令緩存為 8KB);

第二級(jí)為譯碼階段,將取出的指令翻譯為具體的功能操作;

第三級(jí)為轉(zhuǎn)址階段,用來(lái)將內(nèi)存地址和偏移進(jìn)行轉(zhuǎn)換;

第四級(jí)為執(zhí)行階段,指令在該階段真正執(zhí)行運(yùn)算;

第五級(jí)為退出階段,運(yùn)算的結(jié)果被寫回寄存器或者內(nèi)存。

由于處理器同時(shí)運(yùn)行了多條指令,大大提升了程序運(yùn)行的性能。

CPU流水線技術(shù)

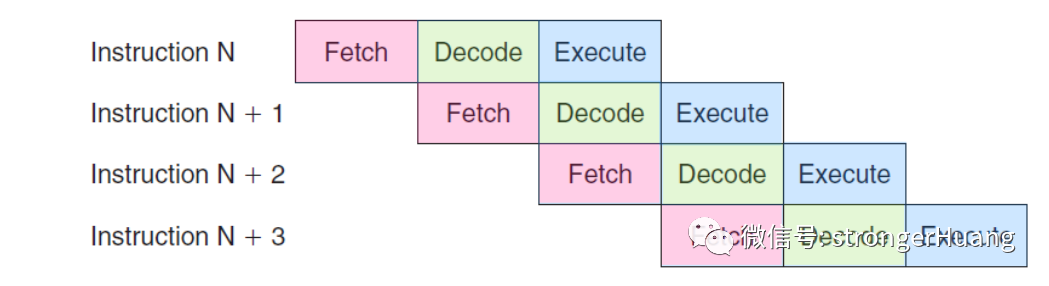

CPU流水線技術(shù)是一種將指令分解為多步,并讓不同指令的各步操作重疊,從而實(shí)現(xiàn)幾條指令并行處理,以加速程序運(yùn)行過(guò)程的技術(shù)。

指令的每步有各自獨(dú)立的電路來(lái)處理,每完成一步,就進(jìn)到下一步,而前一步則處理后續(xù)指令。

采用流水線技術(shù)后,并沒(méi)有加速單條指令的執(zhí)行,每條指令的操作步驟一個(gè)也不能少,只是多條指令的不同操作步驟同時(shí)執(zhí)行,因而從總體上看加快了指令流速度,縮短了程序執(zhí)行時(shí)間。

流水線技術(shù)是通過(guò)增加計(jì)算機(jī)硬件來(lái)實(shí)現(xiàn)的。它要求各功能段能互相獨(dú)立地工作,這就要增加硬件,相應(yīng)地也加大了控制的復(fù)雜性。如果沒(méi)有互相獨(dú)立的操作部件,很可能會(huì)發(fā)生各種沖突。例如要能預(yù)取指令,就需增加指令的硬件電路,并把取來(lái)的指令存放到指令隊(duì)列緩沖器中,使微處理器能同時(shí)進(jìn)行取指令和分析、執(zhí)行指令的操作。

流水線與代碼執(zhí)行效果

為什么說(shuō)同主頻的51單片機(jī)相比STM32執(zhí)行效率低呢?

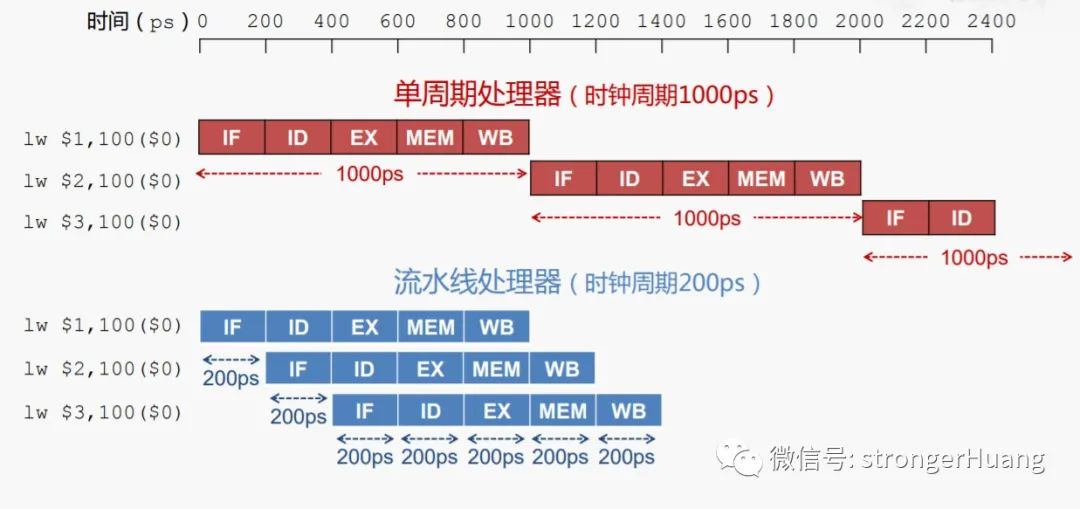

除了大家認(rèn)為的8位和32位寬度區(qū)別之外,還有一個(gè)就是51單片機(jī)不支持流水線(也可以理解為單流水線),而STM32支持流水線。

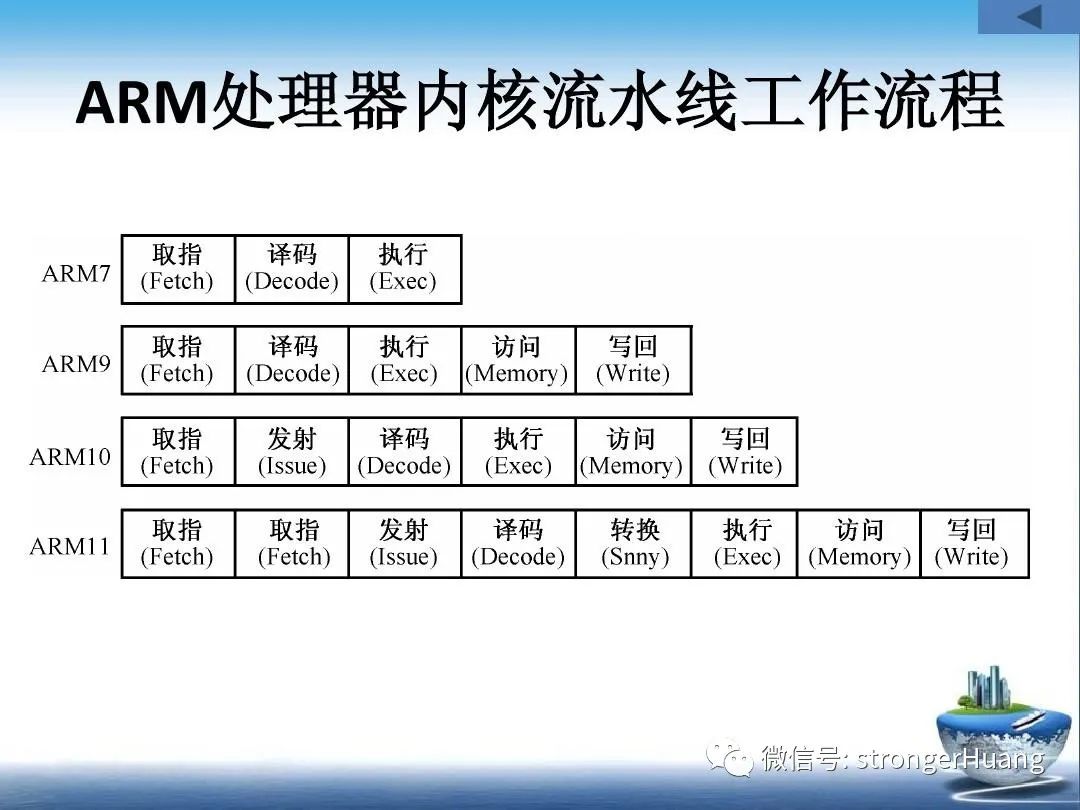

Cortex‐M3處理器使用一個(gè) 3 級(jí)流水線。流水線的 3 級(jí)分別是:取指、解碼和執(zhí)行, 如圖:

通過(guò)下面一張圖來(lái)對(duì)比單流水線和多級(jí)流水線,你就更能明白為什么51單片機(jī)執(zhí)行效率低了。

多級(jí)流水線優(yōu)缺點(diǎn)

并非在所有情況下流水線技術(shù)都起作用,可能有一些缺點(diǎn)。如果一條指令流水線能夠在每一個(gè)時(shí)脈周期接納一條新的指令,被稱為完整流水線(fully pipelined)。因流水線中的指令需要延遲處理而要等待數(shù)個(gè)時(shí)脈周期,被稱為非完整流水線。

當(dāng)一名程序員(或者組合者/編譯者)編寫組合代碼(或者匯編碼)時(shí),他們會(huì)假定每個(gè)指令是循序運(yùn)行的。而這個(gè)假設(shè)會(huì)使流水線無(wú)效。當(dāng)此現(xiàn)象發(fā)生后程序會(huì)表現(xiàn)的不正常,而此現(xiàn)象就是危害。不過(guò)當(dāng)前有提供幾種技術(shù)來(lái)解決這些危害像是轉(zhuǎn)發(fā)與延遲等。

1.優(yōu)點(diǎn)

減少了處理器執(zhí)行指令所需要的時(shí)脈周期,在通常情況下增加了指令的輸入頻率(issue-rate)。

一些集成電路,例如加法器或者乘法器,通過(guò)添加更多的環(huán)路使其工作得更快,如果以流水線替代,能相對(duì)地減少環(huán)路。

2.缺點(diǎn)

流水線處理器設(shè)計(jì)復(fù)雜度更高、生產(chǎn)成本更高;

流水線的處理器必須在數(shù)據(jù)路徑中添加額外觸發(fā)器。

非流水線處理器有固定指令位寬,流水線處理器的性能更難以預(yù)測(cè),并且不同的程序之間的變化可能更大。

審核編輯 :李倩

-

cpu

+關(guān)注

關(guān)注

68文章

10829瀏覽量

211193 -

流水線

+關(guān)注

關(guān)注

0文章

120瀏覽量

25629 -

焊接

+關(guān)注

關(guān)注

38文章

3069瀏覽量

59609

原文標(biāo)題:ARM流水線如何提高代碼執(zhí)行效率

文章出處:【微信號(hào):strongerHuang,微信公眾號(hào):strongerHuang】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

CPU主頻是什么意思

CPU時(shí)鐘周期與主頻的關(guān)系和區(qū)別

雙核cpu和單核cpu的區(qū)別

提高高開(kāi)關(guān)頻率下更高負(fù)載的效率應(yīng)用報(bào)告

CPU主要參數(shù)有哪些

使用TPS25961獲得性能更高、空間更小、成本更低的保護(hù)功能

有沒(méi)有參數(shù)和THS4521差不多,但功耗更低的高速運(yùn)放?

cpu的運(yùn)算器和控制器的作用是什么

cpu控制器負(fù)責(zé)什么運(yùn)算

cpu控制器和運(yùn)算器組成的部件有哪些

什么是cpu的主頻和外頻,它們之間關(guān)系如何

提高系統(tǒng)效率的幾個(gè)誤解解析

一文了解CPU高速緩存

為什么有些CPU的主頻更低,但運(yùn)算效率卻更高呢?

為什么有些CPU的主頻更低,但運(yùn)算效率卻更高呢?

評(píng)論