一、Verilog 編碼風格

(本文的語法高亮因為瀏覽器的緣故,所以不準確)

1.1 使用“`include編譯器指令”

文件包含“`include編譯器指令”用于在合成過程中將源文件的全部內容插入到另一個文件中。它通常用于包括全局項目定義,而無需在多個文件中重復相同的代碼。另一個用例是將代碼的一部分插入模塊,如以下示例所示:

// file test_bench_top.v

// top-level simulation testbench

module test_bench_top;

`include “test_case.v”

endmodule

// file test_case.v

initialbegin

//…

end

task my_task;

//…

endtask

> include編譯器指令的語法定義為:`include

`include“test_case.v”

`include“../../includes/test_case.v”

`include“/home/myprojects/test/includes/test_case.v”

建議僅在include中使用文件名,而不要使用絕對或相對路徑名。這將使代碼位置獨立,因此更加可移植。另一個建議是保持包含文件簡單而不使用嵌套的include指令。

1.2使用`define編譯器指令,parameter和localparam

`define是文本宏替換編譯器指令。它定義為:`define

`define具有全局范圍。一旦定義了文本宏名稱,就可以在項目中的任何地方使用它。文本宏通常是用于定義狀態名稱,常量或字符串的簡單標識符。

parameter關鍵字定義模塊特定的參數,該參數在特定模塊實例的范圍生效。參數用于為模塊實例提供不同的自定義,例如,輸入或輸出端口的寬度。以下是使用parameter關鍵字的示例:

module adder #(parameter WIDTH = 8) (

input[WIDTH-1:0] a,b, output [WIDTH-1:0] sum );

assign sum = a+ b;

endmodule // adder

// aninstance of adder module

adder # (16) adder1 (.a(a[15:0]),.b(b[15:0]),.sum(sum[15:0]));

localparam關鍵字與parameter相似。它被分配了一個常量表達式,并在特定模塊內具有作用域。它定義為:

1.3 使用函數

以下是執行XOR操作的Verilog函數的簡單示例:

module function_example( inputa,b, output func_out);

functionfunc_xor;

inputa, b;

begin

func_xor = a^ b;

end

endfunction

assign func_out = func_xor(a,b);

endmodule // function_example

建議使用Verilog函數來實現組合邏輯和其他不需要非阻塞分配的操作,例如同步邏輯。使用函數可以編寫更緊湊和模塊化的代碼。所有綜合工具均支持Verilog函數。

1.4使用 generate塊

在Verilog-2001中引入了generate塊,以使對同一模塊,函數,變量,網絡和連續分配的多個實例的實例化變得容易。以下是使用generate的兩個示例:

// aconditional instantiation of modules

parameter COND1 = 1;

generate

if(COND1) begin : my_module1_inst

my_module1 inst (.clk(clk), .di(di), .do(do));

end

elsebegin : my_module2_inst

my_module2 inst (.clk(clk), .di(di), .do(do));

end

endgenerate

// using forloop in generate block

genvar ii;

generate

for(ii = 0; ii < 32; ii = ii+1) begin: for_loop

my_module1 inst (.clk(clk), .di(di[ii]), .do(do[ii]));

end

end

endgenerate

1.5 開發簡單的代碼

始終努力開發簡單的代碼。與每種編程語言一樣,Verilog允許編寫詳細的語句,從功能的角度來看,這些語句很優美,但可讀性不高。下面的簡單示例說明了這一點:

reg [5:0] sel;

reg [3:0] result1,result2,a,b;

always @(*) begin

result1 = sel[0] ? a + b : sel[1] ? a - b :

sel[2] ? a & b : sel[3] ? a ^ b :

sel[4] ? ~a : ~ b;

if(~|sel)

result1 = 4'b0;

end// always

reg [5:0] sel;

reg [3:0] result1,result2,a,b;

always @(*) begin

casex(sel)

6'bxxxxx1: result2 = a + b;

6'bxxxx10: result2 = a - b;

6'bxxx100: result2 = a & b;

6'bxx1000: result2 = a ^+ b;

6'bx10000: result2 = ~a;

6'b100000: result2 = ~b;

default: result2 = 4'b0;

endcase

end // always

實現result1和result2的邏輯在功能上是等效的。但是,在result1中使用嵌套三元運算符和兩個賦值語句不太透明,并且與result2邏輯的更清晰的case語句相比,需要花更多的精力來理解。

通常,代碼清晰度高容易實現高效率。同一段代碼能在其生命周期內被多個開發人員讀取。編寫更清晰的代碼更容易調試,并且一般不容易包含錯誤。

二、為FPGA編寫可綜合的代碼

2.1考慮資源

Verilog語言參考手冊(LRM)提供了豐富的功能來描述硬件。但是,只有一部分語言可以為FPGA綜和。即使有些特定的語言結構是可綜合的,也不能保證該代碼能在特定FPGA上實現物理電路。考慮以下示例:

reg [7:0] memory[1:2**22];

initial begin

memory[1] = 8’h1;

memory[2] = 8’h2;

end

該示例能正確模擬出來,但會導致FPGA物理實現失敗。該代碼需要4 MB的內存,這是一些FPGA所沒有的。此外,綜合工具將忽略初始塊,該塊將初始化內存的最低兩個字節。

該技巧提供了一些指導方針和建議,以幫助編寫用于FPGA的可綜合代碼。

2.2 遵循同步設計原則

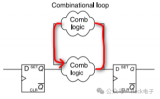

建議開發人員遵守FPGA同步設計的原則,其中包括以下內容:

1、使用同步復位。后續會詳細討論,同步,異步復位的問題

2、避免使用鎖存

3、避免使用門控,派生或分頻時鐘

4、使用時鐘使能而不是多個時鐘

5、對所有異步信號實行正確同步

審核編輯 :李倩-

FPGA

+關注

關注

1626文章

21678瀏覽量

602035 -

Verilog

+關注

關注

28文章

1345瀏覽量

109996

原文標題:學習FPGA的小Tips(一)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog硬件描述語言參考手冊

如何利用Verilog-A開發器件模型

Verilog編碼風格

Verilog編碼風格

評論