近兩年,隨著國家對信息技術應用創新日益重視,作為芯片行業的重要成員,許多國產CPU公司有了長足的發展。無論是面對芯片緊缺、斷供的嚴峻形式,還是工業軟件“卡脖子”的窘境,都無一例外要求我們加大國產芯片、工業軟件的研發力度和速度。包括龍芯、飛騰、海光、兆芯在內的眾多國內一線CPU芯片設計公司,正在為全力打造“中國芯”而不懈努力。在這個進程中,急需一種快速的方法,檢查芯片設計和應用中的信號完整性、電源完整性問題,從而提高CPU芯片的設計迭代和投產效率。

國產CPU市場概況CPU處理器主要面向的市場有PC、服務器、嵌入式、智能手機、安防監控、汽車電子、視頻和多媒體處理。目前,中國仍是全球CPU最大的消費市場,下游需求旺盛,隨著國際供應鏈斷裂和信息安全風險加劇,我國對國產CPU領域的政策支持力度持續提高,國內CPU正在加快發展步伐。

國產CPU中以X86架構代表的企業有兆芯、海光。其中,兆芯是來自威盛的x86技術,架構技術和性能相對Intel、AMD有所差異;海光獲得的是AMD 14nm Zen架構的IP授權。ARM架構的代表還有華為、飛騰。此外,MIPS架構的代表有龍芯。

從國產CPU的工藝制程看,16nm工藝是比較主流的先進工藝,采用7nm工藝的只有華為鯤鵬920,但其處于暫停生產狀態,而兆芯新一代7nm工藝芯片尚未正式發布,其它廠商的規劃還不明確。在政企市場,國產CPU受到重視,得到快速推進,而在消費級市場還只是剛開始。

CPU應用中的挑戰

1. 信號完整性、電源完整性挑戰

在CPU中,通常采取優化多核心、高速緩存、內存、IO等接口的方式,以達到提升運算速度并降低功耗的目的。但在這一過程中,不可避免的會存在信號完整性和電源完整性的問題,而且越是使用先進工藝節點,其挑戰就越嚴峻。無論是對于傳統封裝還是先進封裝,信號的可靠程度與電源的穩定性都是衡量芯片質量的標準。因此,在設計中必須面對這兩個老生常談的問題。除了優化設計外,如何加快設計迭代速度也是設計中的重要考量因素。

2. 先進封裝帶來挑戰

CPU的封裝,從早期的QPF、FCBGA到現在的先進封裝,有了更多的變化。對于CPU芯片來說,隨著工藝的發展,工程師利用硅載板或者TSV結構設計的先進封裝,如何能夠準確高效的處理好多個信號之間的串擾問題,也是設計的重要一環。

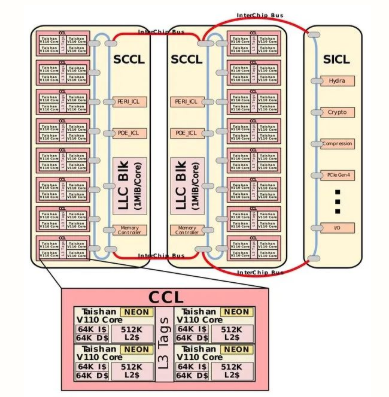

以鯤鵬920為例:下圖是三顆裸芯組成的64核芯片,其中左邊兩顆為計算DIE,每顆含32個TSV110核,由4個核組成一個簇,8個簇掛在一個環狀總線上,32MB的L3作為一個節點也掛在環上,同樣的存控也作為一個節點掛在環上。三顆裸芯之間由 chip間總線實現互連。復雜的工藝以及眾多的信號線需要一個強大計算能力的仿真工具,完成對信號和串擾的評估。

圖1 鯤鵬920內部架構圖

3. PCB板級協同挑戰

對于CPU芯片來說,在設計配套CPU的PCB測試版、demo板時,也需要進行相關的仿真工作。一方面芯片的高速接口需要PCB的協同設計,另一方面,PCB作為CPU的配套使用載體,它的性能也是直接影響整體鏈路性能是否完善的關鍵因素。對于高速PCB來說,就算是經驗豐富的工程師,在設計高速鏈路的時候,仍需要對過孔、焊盤等細節進行優化。若有SerDes或者DDR的走線,對其串擾的分析就更不可避免。

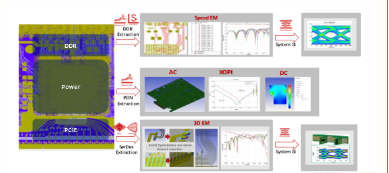

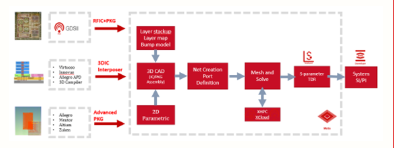

芯和CPU應用中的SI/PI解決方案芯和半導體針對CPU應用中的封裝以及PCB的SI/PI提供了完整的解決方案。對于傳統型封裝的QFN、QFP或者FCBGA,工程師可以利用芯和半導體的工具,針對其金線、Bump等結構進行分析;對于3DIC、Chiplets或者TSV結構的先進封裝,設計人員同樣可以利用工具進行設計-分析的一站式流程;而對于PCB板級,也可以根據低頻-高頻不同的應用場景進行相應的算法切換并進行分析。

圖2 CPU應用中的SI/PI解決方案

1. 信號完整性、電源完整性分析

芯和半導體的Hermes 3D、Hermes PSI提供了針對CPU封裝的SI及PI的解決方案。Hermes 3D是一款三維全波電磁場仿真工具,它可以支持主流ECAD工具輸出的版圖文件,導入生成相應的3D模型。它同時提供了自動切割版圖和自動添加端口的功能,大幅提高了工程師的建模效率。Hermes 3D采用自適應網格剖分技術和有限元算法,可以確保對任意三維結構在任意頻段都具備較高的求解精度。

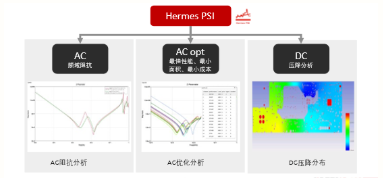

Hermes PSI 是一款專注封裝與板級電源完整性分析的工具,包括直流壓降分析和交流阻抗分析兩大功能模塊。在設計中,直流壓降分析可以幫助工程師快速分析電源的直流效應,并檢查直流壓降、電流趨勢和電流密度分布,優化電源路徑中可能存在的瓶頸。交流阻抗分析可以計算封裝基板和PCB之間的PDN阻抗,并自動優化去耦電容。

圖3 Hermes3D 幫助建模與SI仿真

圖4 HermesPSI幫助建模與PI仿真

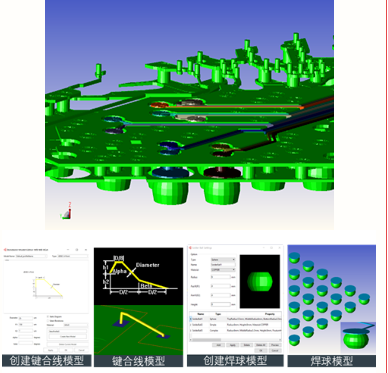

2.先進封裝仿真建模

芯和半導體的Metis工具提供了專注于先進封裝的建模和仿真流程,針對目前最為火熱的Chiplets、TSV、interposer等結構,有著明顯的建模和仿真優勢。工程師可以利用它突破傳統封裝仿真技術的極限,同時容納超大規模的信號數量,并利用矩陣級別的集群分布式計算,提高計算效率的同時,降低硬件資源消耗,真正達到快速、節省的跨尺度仿真效果。工程師在初次使用時,可以通過3DIC和先進封裝兩種分析流程向導,快速完成聯合仿真設置。利用內置的Speed、Balanced和Accuracy三種仿真模式,滿足工程師不同設計階段對精度和速度要求。

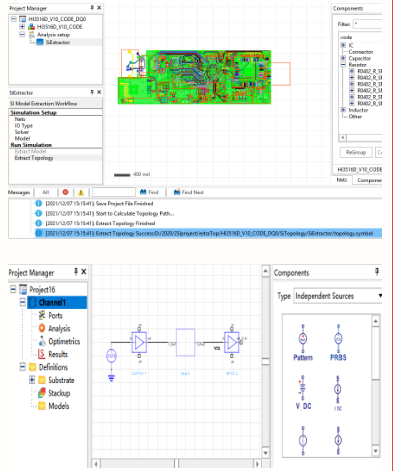

圖5 Metis提供先進封裝仿真流程

3.PCB板級協同仿真

在CPU設計時,PCB和封裝的協同設計同樣重要。工程師不但可以通過Hermes工具進行封裝設計仿真,也可以進行PCB板級設計的仿真。設計人員利用Hermes PSI的拓撲功能,可以快速進行封裝和PCB板級的協同仿真。此外還可以進行電、熱的協同仿真,讓工程師可以直觀的了解現有設計中芯片的供電質量如何,電流密度是否滿足設計規范要求。根據這些仿真結果,讓工程師可以調整優化現有封裝設計,從而大大加快產品的設計周期,提高產品的設計質量。

圖6 HermesPSI拓撲功能幫助仿真設計

總結本文首先從國內CPU的發展現狀切入,講述了目前CPU研發現狀以及市場現狀,引出CPU應用中的挑戰。無論是傳統型封裝、先進封裝還是PCB板級,CPU在設計時都會存在信號完整性、電源完整性的問題。芯和半導體的Hermes 3D、Hermes PSI可以進行信號完整性、電源完整性的分析;Metis工具可以幫助工程師進行先進封裝的仿真;同時它們也都支持PCB板級的協同仿真,可以很好的從根本上解決CPU應用中的仿真難題。

-

處理器

+關注

關注

68文章

18927瀏覽量

227230 -

pcb

+關注

關注

4294文章

22776瀏覽量

393237 -

cpu

+關注

關注

68文章

10702瀏覽量

209371 -

封裝

+關注

關注

125文章

7593瀏覽量

142145

發布評論請先 登錄

相關推薦

如何在FPGA中實現狀態機

具身智能與人形機器人領域現狀、挑戰以及未來方向

梯云物聯|全球及中國智能電梯市場:蓬勃現狀與廣闊前景

萬兆電口模塊的產業發展現狀與前景展望

三坐標測量機發展現狀以及三坐標國產化的意義

全球FPGA市場現狀和發展前景展望

國產車規級芯片發展現狀、問題及建議

CPU研發現狀以及市場現狀

CPU研發現狀以及市場現狀

評論