除了可用性、價(jià)格/性能和占地面積等明顯的選擇標(biāo)準(zhǔn)外,其他方面對于設(shè)計(jì)過程也很重要:

設(shè)計(jì)工具

HEITEC 開發(fā)團(tuán)隊(duì)對供應(yīng)商特定工具有非常好的經(jīng)驗(yàn),因?yàn)殚_發(fā)環(huán)境直觀可用且成熟。英特爾 Quartus Prime 軟件套件具有英特爾 SoC FPGA 開發(fā)所需的一切功能。它是一個(gè)完整的開發(fā)包,配備了用戶友好的用戶界面和有助于實(shí)施的技術(shù)。市場上提供的工具非常全面,包括評估套件、對各種協(xié)議、數(shù)據(jù)速率和應(yīng)用程序的支持、大量文檔以及利用 ARM 生態(tài)系統(tǒng)優(yōu)勢的 ARM 兼容軟件。軟件和適當(dāng)?shù)墓ぞ呦蛳潞拖蛏霞嫒荨3碎_源 Linux 之外,還有許多操作系統(tǒng)、開發(fā)工具、合作伙伴的IP核和專業(yè)服務(wù)。通過利用現(xiàn)有資源,可以產(chǎn)生協(xié)同效應(yīng)并利用現(xiàn)有經(jīng)驗(yàn),從而降低風(fēng)險(xiǎn)、實(shí)現(xiàn)遷移并加快上市時(shí)間。

領(lǐng)先的英特爾 DSP 設(shè)計(jì)工具包括面向硬件設(shè)計(jì)的英特爾 FPGA 的 DSP 構(gòu)建器和面向軟件程序員的 OpenCL SDK。硬化浮點(diǎn)模塊在算法設(shè)計(jì)期間自動(dòng)映射,使用 FPGA 的 DSP 構(gòu)建器或 OpenCL 的 SDK 并在軟件中實(shí)例化浮點(diǎn)數(shù)據(jù)類型。對于較小的設(shè)計(jì)任務(wù),可以使用單獨(dú)的 FPGA IP 功能和宏功能。英特爾設(shè)計(jì)工具可自動(dòng)優(yōu)化和使用浮點(diǎn)模塊以及抽象以硬件為中心的設(shè)計(jì)挑戰(zhàn),例如轉(zhuǎn)換為定點(diǎn)和模塊拓?fù)洹⒘魉€和時(shí)間復(fù)用的知識。

固定

除了 ECC 和更好的存儲連接之外,Arria10 SoC 還受到引腳可用性的青睞,以創(chuàng)建提高安全性和降低功耗的設(shè)計(jì)。54 個(gè)可編程 I/O 可用于一般用途。要占用 PLL 或時(shí)鐘管腳,英特爾 Quartus Prime 軟件用于設(shè)置 I/O 分配。為數(shù)據(jù)輸出和輸入提供了特殊的高速引腳。其他多用途引腳既可用作單端 I/O,也可用作外部反饋引腳;此外,I/O 引腳可用作兩個(gè)單端時(shí)鐘輸出或差分時(shí)鐘輸出。因此,I/O 引腳的布局可能性提供了非常高的靈活性。

提高安全性和加密

對于更大和更關(guān)鍵的系統(tǒng)組件,保護(hù)設(shè)計(jì)免受未經(jīng)授權(quán)的復(fù)制、逆向工程和操縱非常重要。英特爾 FPGA 通過使用高級 POF 加密標(biāo)準(zhǔn) (AES) 加密其配置比特流并定義或限制可訪問區(qū)域來考慮這一點(diǎn)。基于橢圓曲線數(shù)字簽名認(rèn)證 (EC DSA) 和清晰的公鑰基礎(chǔ)設(shè)施支持安全啟動(dòng)。只接受來自已知和可靠來源的代碼。

20-nm FPGA 包括額外的安全特性,可以通過使用獨(dú)立的 Qcrypt 工具或 Intel Quartus Prime Convert Programming File 來激活。篡改保護(hù)和 JTAG 安全模式可以在 20-nm FPGA 中單獨(dú)激活,JTAG 可以禁用或防止重讀。ECC 進(jìn)入緩存的安全性確保了可靠的錯(cuò)誤檢測。實(shí)現(xiàn)了七個(gè)通用定時(shí)器和四個(gè)看門狗定時(shí)器。各種控制機(jī)制能夠防止過熱或欠壓。

通過優(yōu)化電源提高能源效率

SoC 包括一個(gè)電源排序選項(xiàng),以實(shí)現(xiàn)優(yōu)化的功耗。SmartVoltage ID 功能使 FPGA 能夠以相同的功率和更低的電壓運(yùn)行。因此,整個(gè)裝置的平均功耗也可以降低,并且由于低電感可以實(shí)現(xiàn)更高頻率的去耦。可編程電源技術(shù)可加快速度關(guān)鍵操作,同時(shí)減少非關(guān)鍵操作。

在最終實(shí)現(xiàn)的概念中,SoC FPGA,包括嵌入式 CPU,連接到應(yīng)用程序的控制板,并運(yùn)行嵌入式 Linux 操作系統(tǒng)。主板具有連接到 GUI PC 的 Gig-E 接口和連接到系統(tǒng)所有其他部分的數(shù)據(jù)接口。GUI PC 千兆以太網(wǎng)接口生成的樣本吞吐量包含本地路徑命令列表形式的控制信息,包括脈沖能量、脈沖速率、所需位置和應(yīng)用程序速度的設(shè)置。通過腳踏開關(guān)啟動(dòng)過程后,控制板完全自主執(zhí)行指令并同時(shí)監(jiān)控所有操作。此外,還會檢查連接設(shè)備的所有故障條件、溫度和電壓以及能量水平。后者是通過比較電源和頻率的設(shè)定值和實(shí)際值來完成的。如果出現(xiàn)故障信號,系統(tǒng)將關(guān)閉。

概括

開發(fā)具有強(qiáng)大架構(gòu)的產(chǎn)品是確保系統(tǒng)設(shè)計(jì)滿足現(xiàn)在和未來性能要求的關(guān)鍵。借助用于嵌入式系統(tǒng)的 SoC,設(shè)計(jì)立足于堅(jiān)實(shí)的基礎(chǔ)。用于中型應(yīng)用的 FPGA 可顯著節(jié)省空間并在功耗、成本和性能之間取得良好平衡。Arria 10 SoC就是這樣一個(gè)典型代表。

借助 Arria 10 SoC,您可以通過將 GHz 級處理器、FPGA 邏輯和數(shù)字信號處理 (DSP) 集成到單個(gè)可定制的片上系統(tǒng)中來減小電路板尺寸,同時(shí)提高性能。Arria 10 SoC 提供了廣泛的 FPGA 邏輯密度,并且硬化浮點(diǎn) DSP 實(shí)現(xiàn)為浮點(diǎn)設(shè)計(jì)提供了全新的可能性。這些器件提供最高的浮點(diǎn)性能、能效和精度,同時(shí)縮短了開發(fā)時(shí)間。

具有硬化浮點(diǎn) DSP 模塊的 FPGA 在中端 Arria 10 構(gòu)建模塊中提供 160 到 1,500 GFLOPS 的容量。這些峰值 GFLOPS 指標(biāo)的計(jì)算基于 CPU、GPU 和 DSP 上使用的相同透明方法。這種方法為設(shè)計(jì)人員提供了一種可靠的技術(shù),用于基本比較基于非常不同架構(gòu)的構(gòu)建塊的峰值浮點(diǎn)計(jì)算能力。通過強(qiáng)化浮點(diǎn) DSP 實(shí)施,F(xiàn)PGA 現(xiàn)在可用于越來越多的數(shù)據(jù)密集型應(yīng)用,例如高性能計(jì)算 (HPC)、雷達(dá)和醫(yī)學(xué)成像,從而以更低的總系統(tǒng)成本(總擁有成本)獲得更高的性能。 基于所獲得的經(jīng)驗(yàn),HEITEC 開發(fā)團(tuán)隊(duì)可以相應(yīng)地為幾乎任何應(yīng)用實(shí)現(xiàn)具有 FPGA 功能的 SoC。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19165瀏覽量

229131 -

dsp

+關(guān)注

關(guān)注

552文章

7962瀏覽量

348269 -

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601861

發(fā)布評論請先 登錄

相關(guān)推薦

soc設(shè)計(jì)中的熱管理技巧

晶閘管的觸發(fā)脈沖要滿足哪些要求

嵌入式系統(tǒng)的未來趨勢有哪些?

選擇導(dǎo)線截面有什么要求

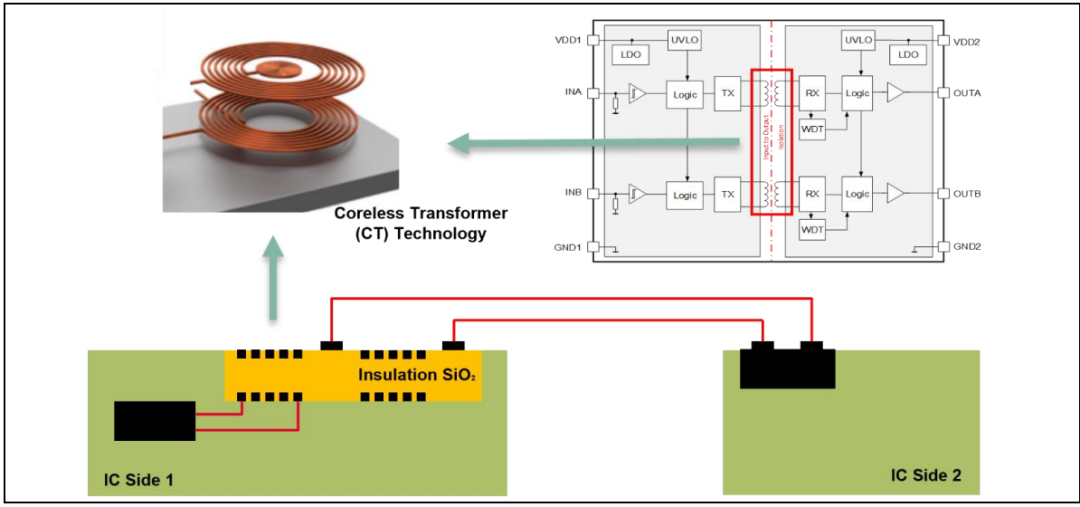

滿足汽車電氣隔離要求的數(shù)字隔離器

嚴(yán)格的性能測試確保連接器可滿足復(fù)雜環(huán)境的應(yīng)用需求

簡儀計(jì)數(shù)器/定時(shí)器模塊滿足嚴(yán)格的工業(yè)標(biāo)準(zhǔn)和安全要求

液壓伺服控制系統(tǒng)的控制要求

FCom富士差分振蕩器-高性能交換機(jī)中的應(yīng)用及性能要求

ADI大電流LDO產(chǎn)品陣容:滿足高性能處理器的電源要求

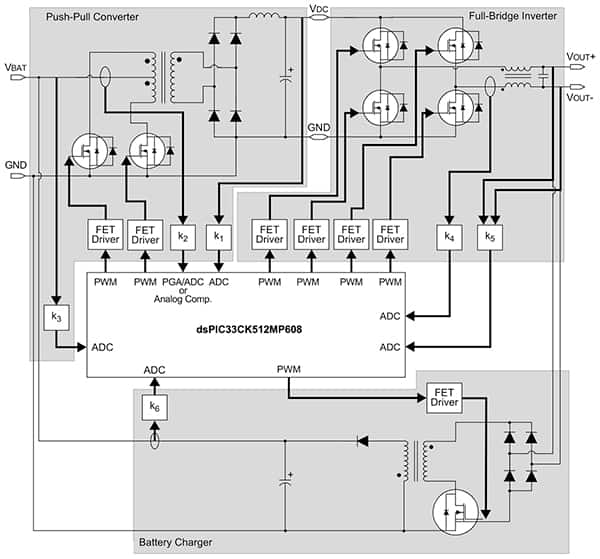

如何使用 DSC 和 MCU 確保嵌入式系統(tǒng)安全

汽車技術(shù)的未來:Netropy如何測試和確保汽車以太網(wǎng)的性能

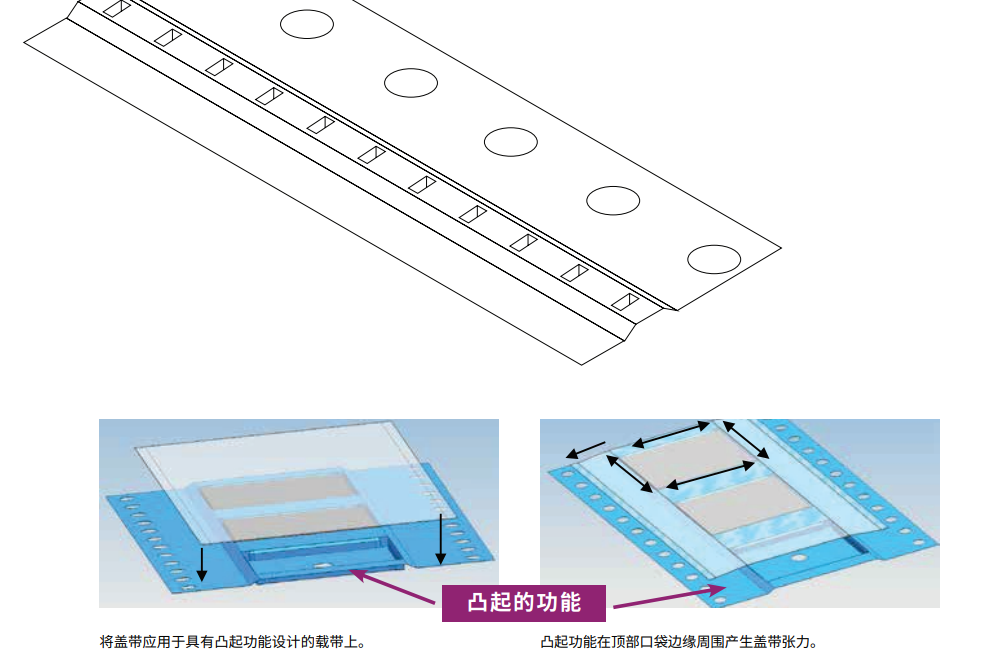

滿足特殊要求的定制化載帶設(shè)計(jì)

ADP5022滿足嚴(yán)苛的性能和電路板空間要求

Arria 10 SoC確保系統(tǒng)設(shè)計(jì)滿足現(xiàn)在和未來性能要求

Arria 10 SoC確保系統(tǒng)設(shè)計(jì)滿足現(xiàn)在和未來性能要求

評論