為解決SOC片上系統的設計瓶頸,SiP(system in Package)微系統技術已成為最普遍的應用手段。SiP能在同一個封裝基板上布局多個裸die,實現了系統間快速互聯互通。 SiP的實現有兩種形式,一種是傳統BGA形式,它利用封裝基板互連,可以通過ubump或wirebond進行die和基板連通;另一種是2.5D、3DIC先進封裝形式,利用interposer(硅中介層)及TSV(硅通孔)實現水平RDL布局及垂直方向通孔連接。 本文介紹的是利用芯和半導體Hermes 3D軟件,實現“倒裝焊-金線(FC-BW)BGA封裝的電磁場仿真”的應用。通過Hermes 3D快速的版圖導入、bump添加、版圖切割、端口添加等功能,便利地完成仿真工程的建立以及模型抽取。

Hermes 3D的FC-BW BGA仿真建模流程

1.軟件概述

Hermes 3D是一款針對各類封裝和PCB的電磁場仿真平臺。它支持主流版圖文件導入,例如mcm、sip、brd、dxf、dwg、gds、ODB++、PADs等文件格式;支持版圖在軟件內自動或手動隨意截取操作;采用3D FEM求解引擎,能對各類3D結構準確仿真建模;支持多種端口激勵添加,例如lumped port、wave port、coax port、annular port等;支持HFSS工程腳本導出,方便用戶橫向對比仿真精度。

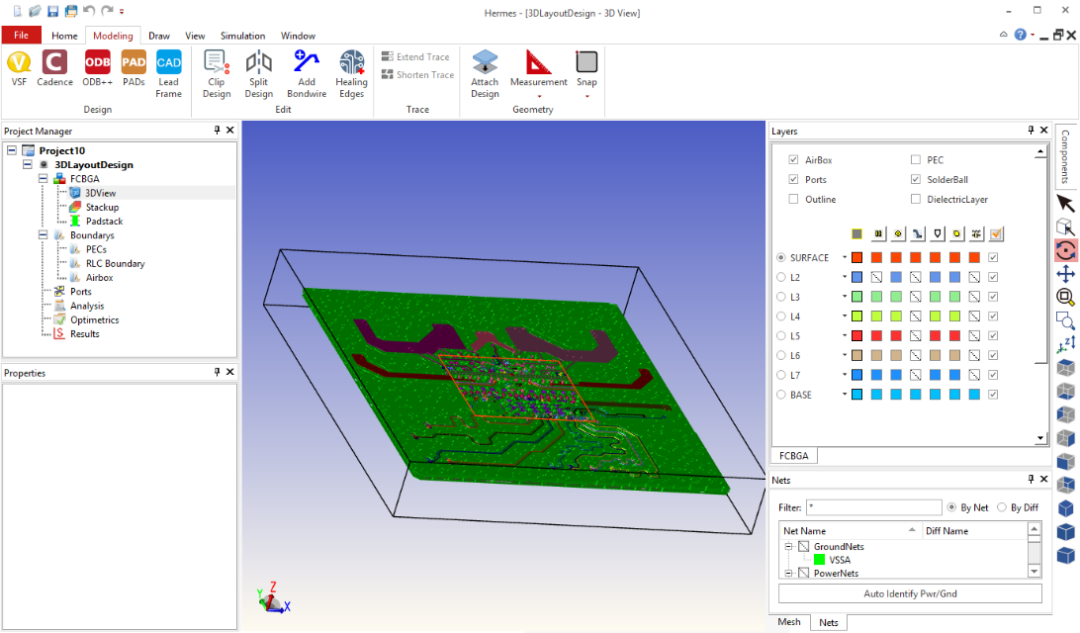

2.導入FC-BW BGA版圖文件

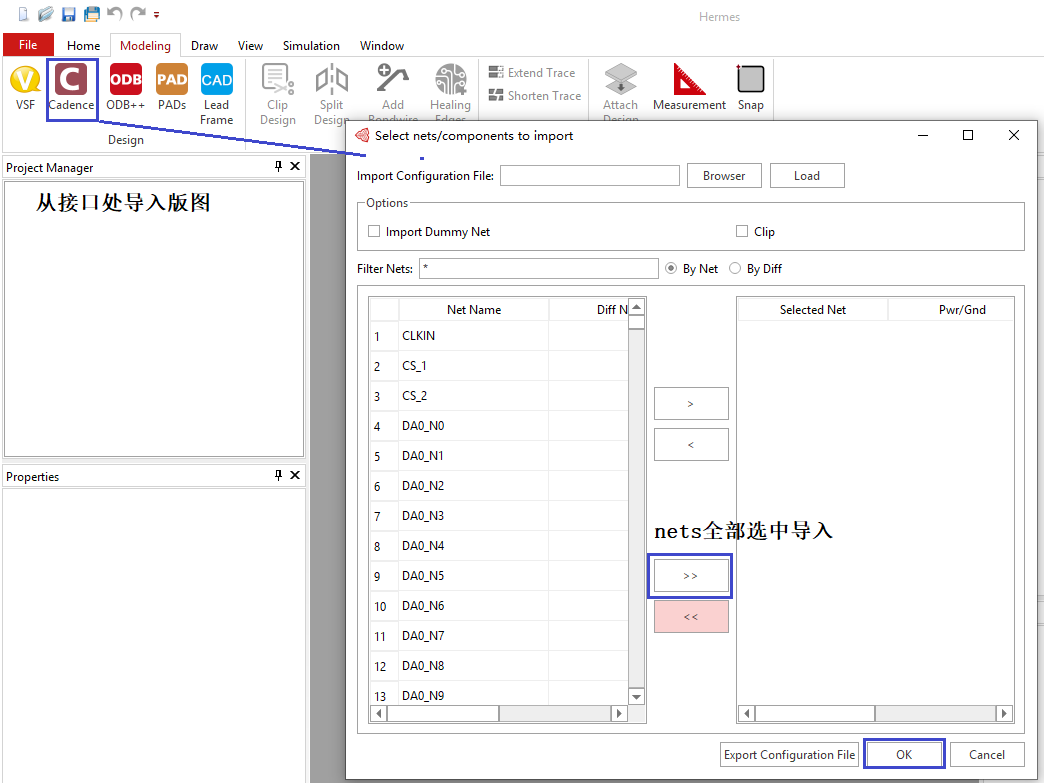

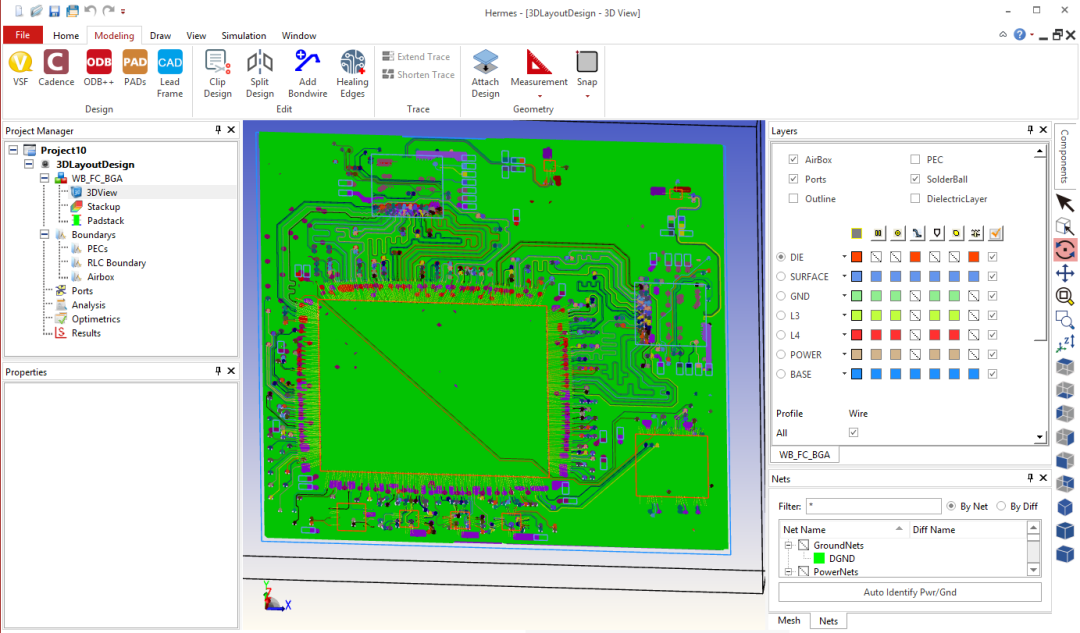

Hermes 3D能夠快速導入.sip版圖格式。其中,版圖中的nets可以全部導入,也可以根據需求選擇性導入。 當導入版圖文件時,所有相關金屬層、過孔、介質的材料信息也會一并導入,生成疊層文件,用于仿真求解。

本例中,有8個die通過金線和封裝基板連接,其中兩個die是flipchip形式,通過ubump和封裝基板連接,因此結構屬于FC-WB混合類型。

3. 仿真前設置

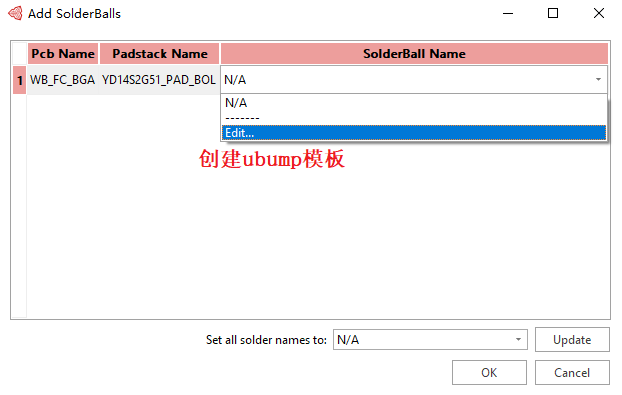

(1)添加FC結構的ubumpHermes 3D提供ubump自動添加功能,選中die結構,創建ubump模板,軟件會在封裝的finout位置添加對應的ubump結構。

首先找到FC連接的die名稱:

點擊Edit進入ubump創建窗口:

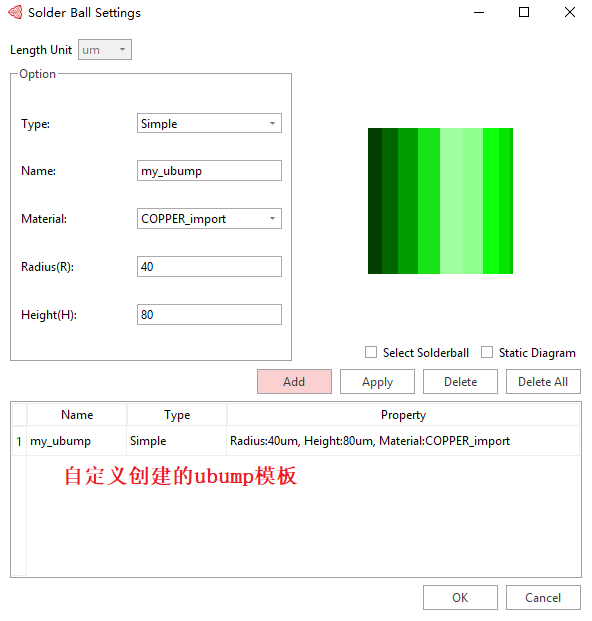

自定義ubump模板:

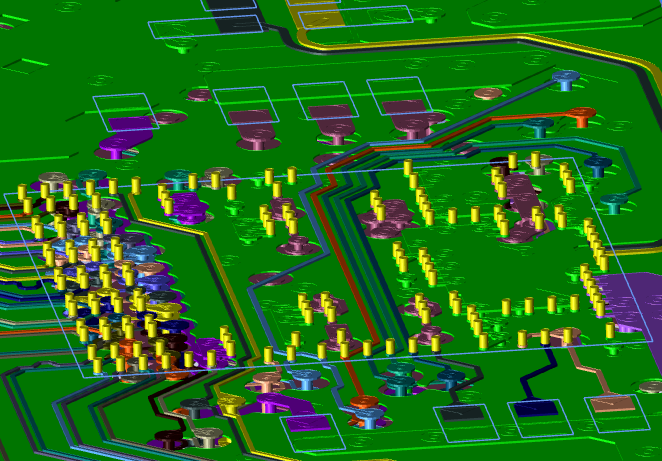

軟件自動在finout位置布滿ubump結構:

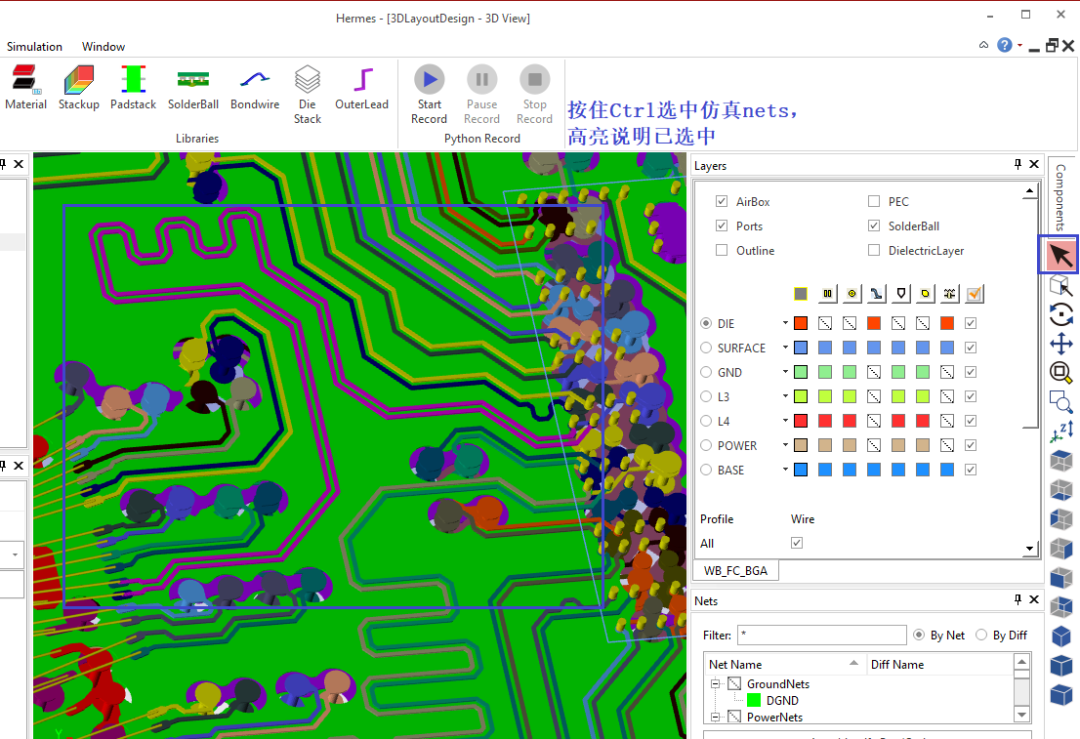

(2)按網絡nets進行版圖切割Hermes 3D支持信號網絡選擇,然后根據nets區域可自動進行版圖切割,操作如下。 連續選擇需要仿真的nets和參考地:

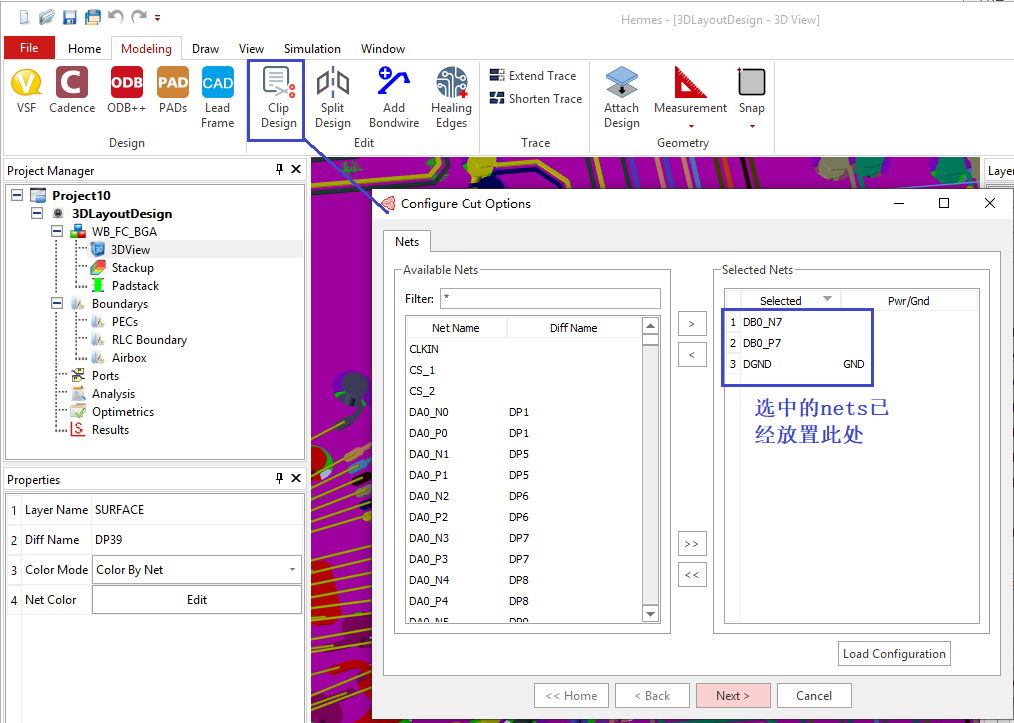

點擊Clip Design,開始切割版圖:

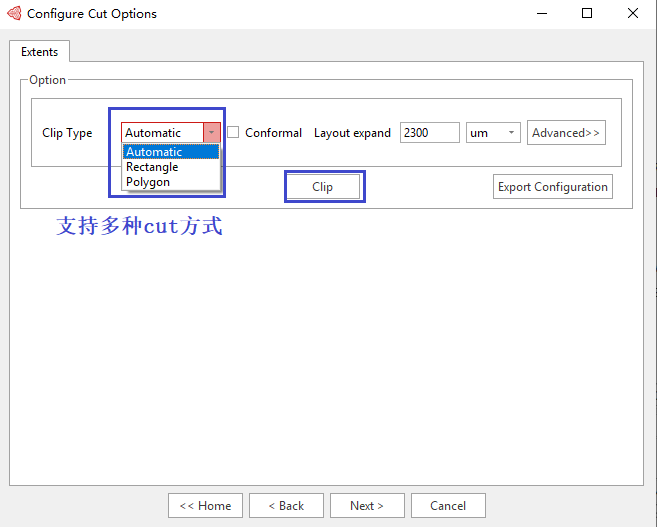

選擇切割方式,開始切割:

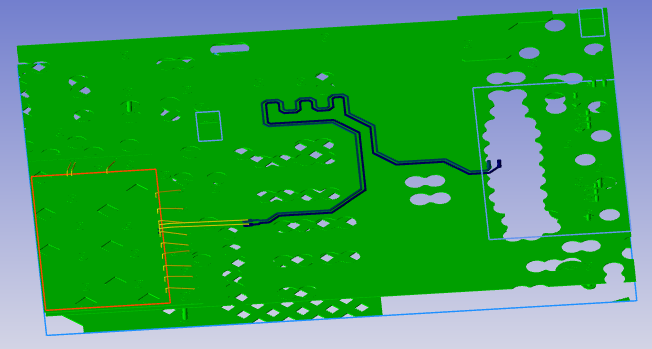

最終根據選擇nets,自動完成版圖切割:

(3)激勵端口添加

版圖切割完成后,用戶必須添加端口激勵才能仿真。本文以差分nets添加激勵端口為例,進行演示。

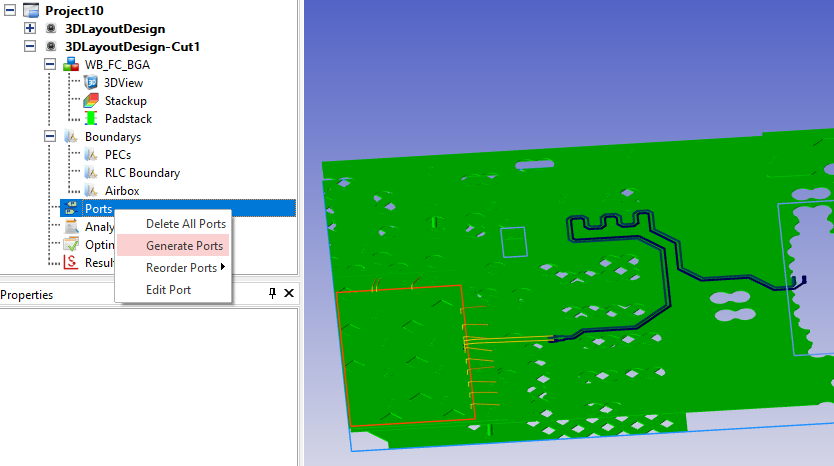

首先點擊Generate Ports:

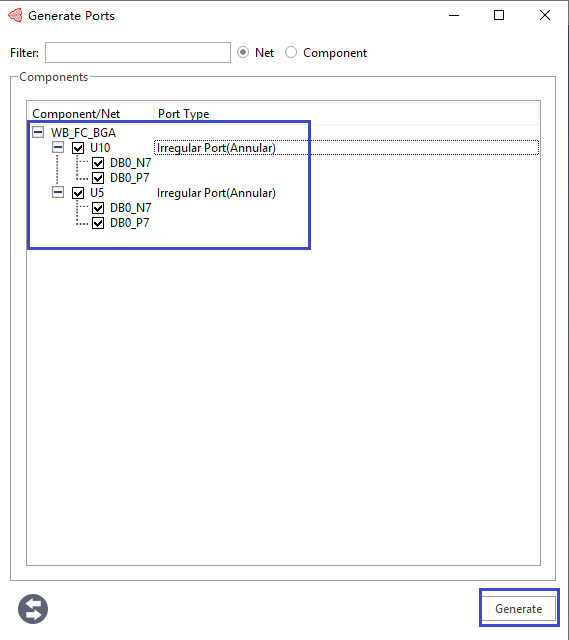

勾選nets相關的component,點擊Generate生成激勵ports:

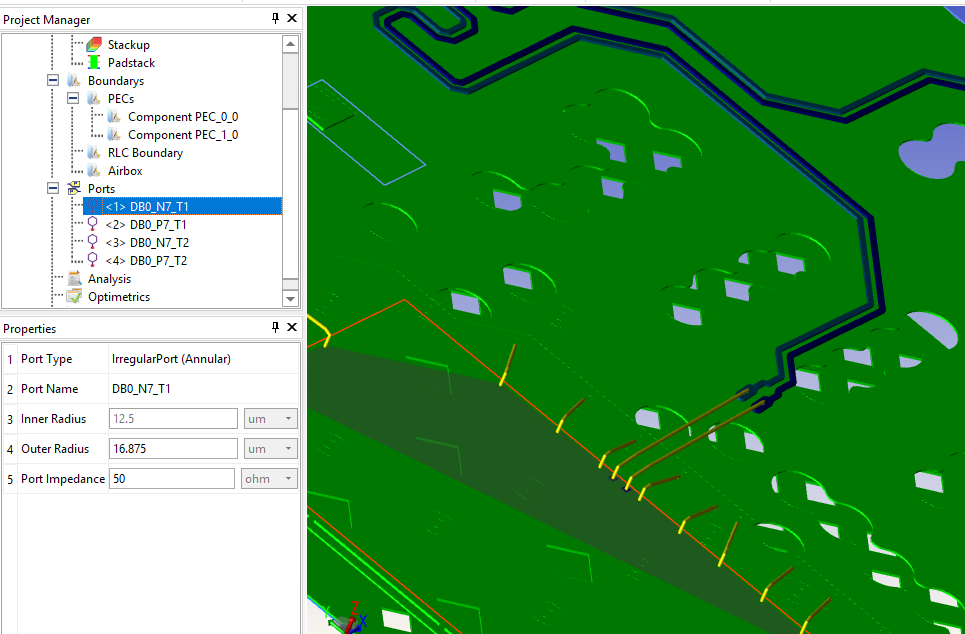

此時在ubump和wirebond端點處自動添加了環形激勵端口,如下圖所示:

(4)提交電磁場仿真

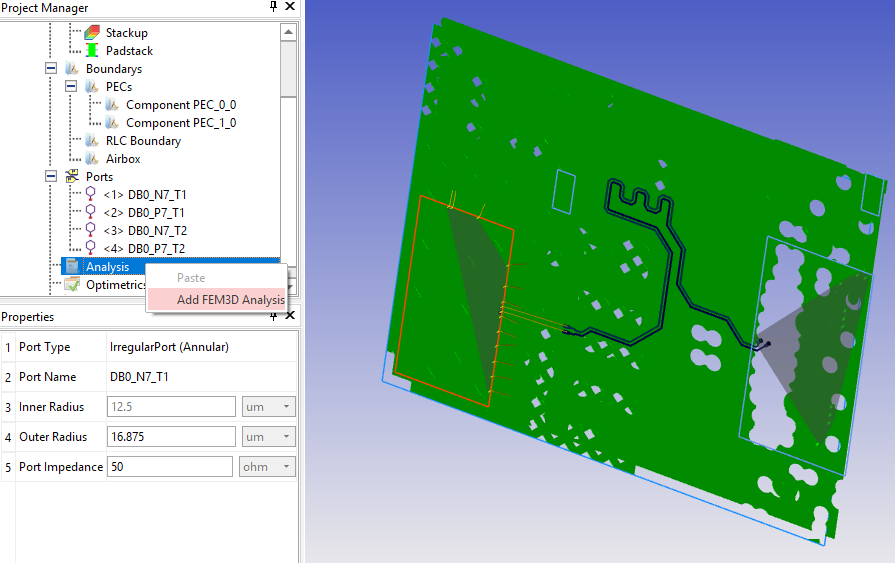

首先添加仿真分析類型:

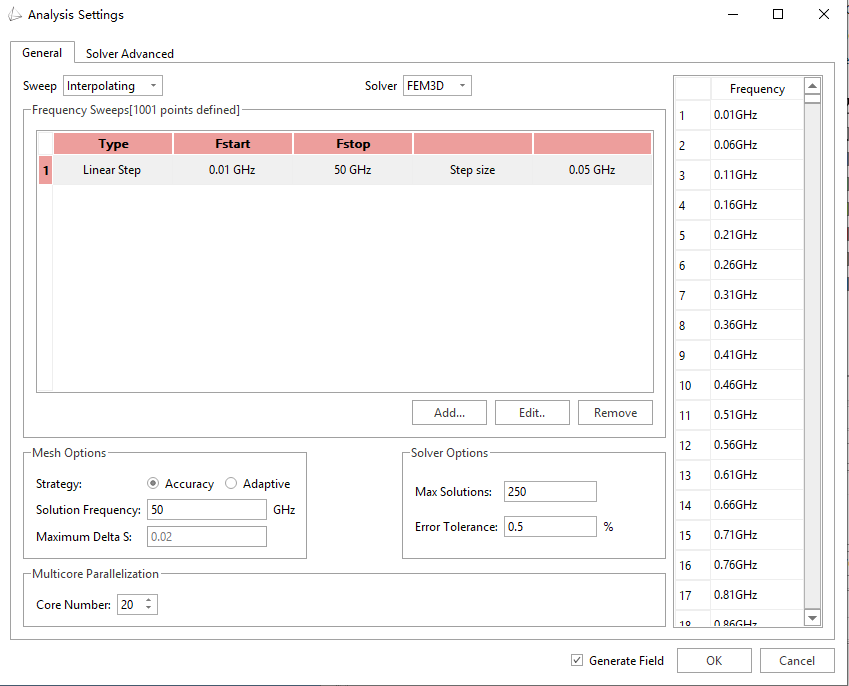

接著設置掃頻范圍:

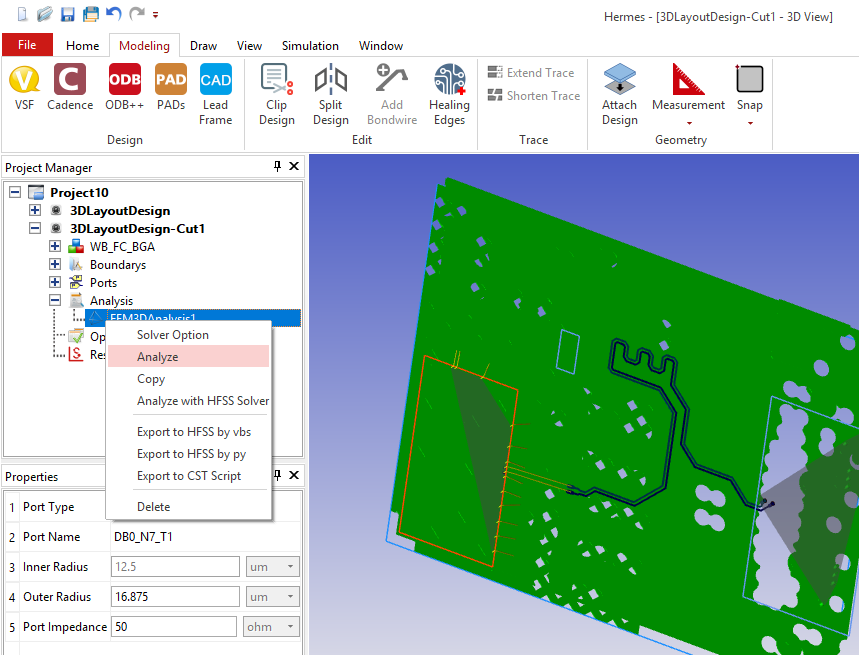

最后提交仿真任務:

4.仿真結果分析

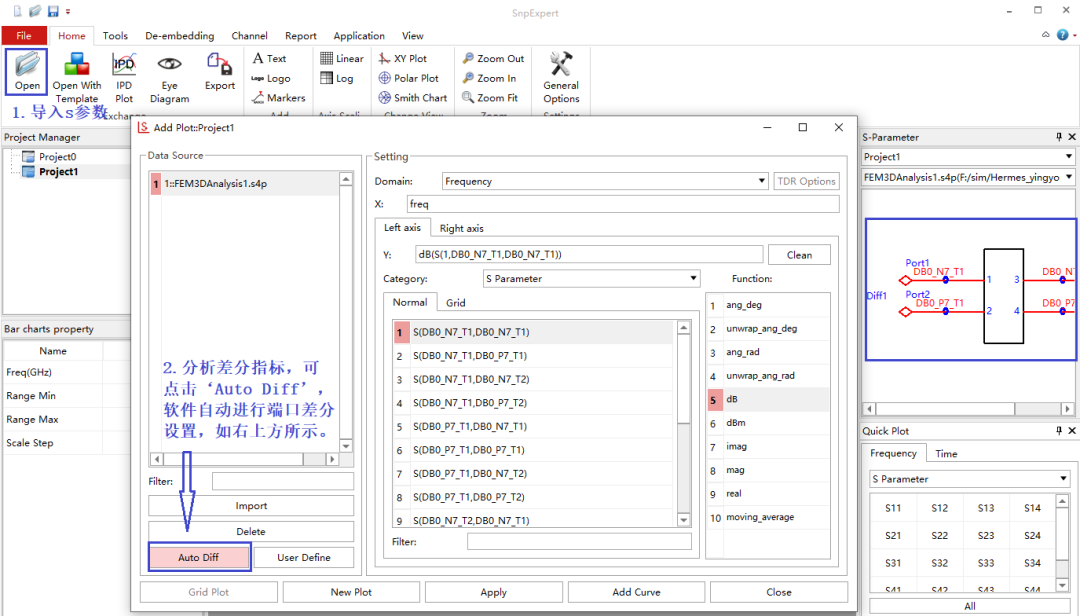

Hermes 3D完成BGA封裝仿真后,用戶可利用芯和半導體的s參數后處理工具SnpExpert進行結果查看和指標分析。 首先導入s參數,并完成差分端口配對:

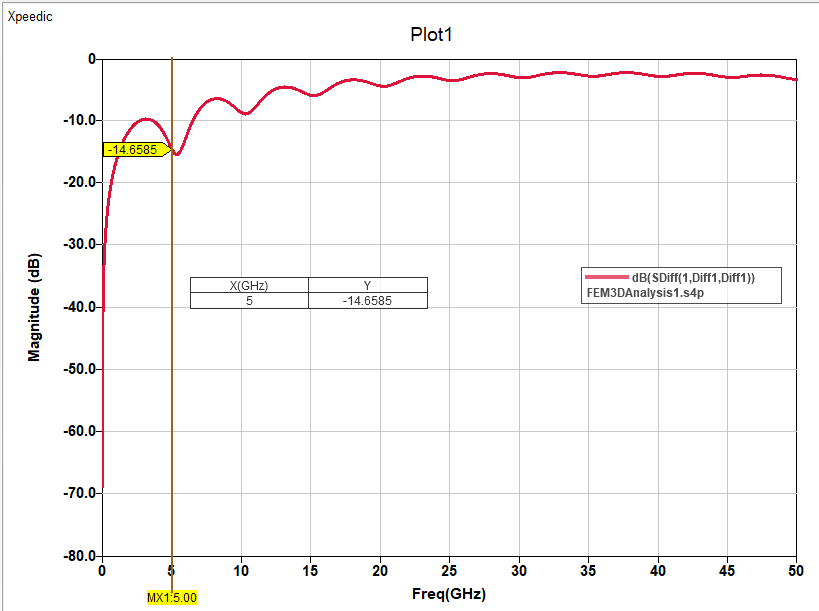

接著查看差分回波損耗:

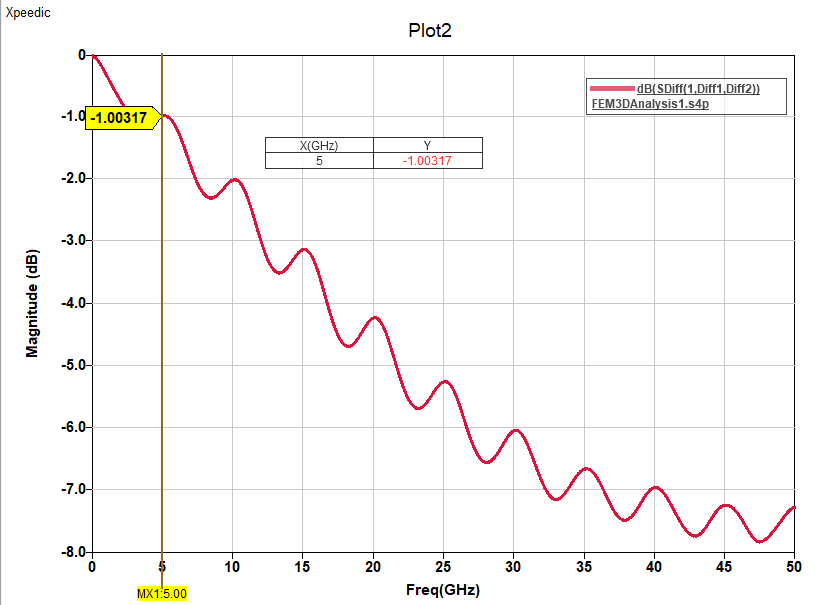

查看差分插入損耗:

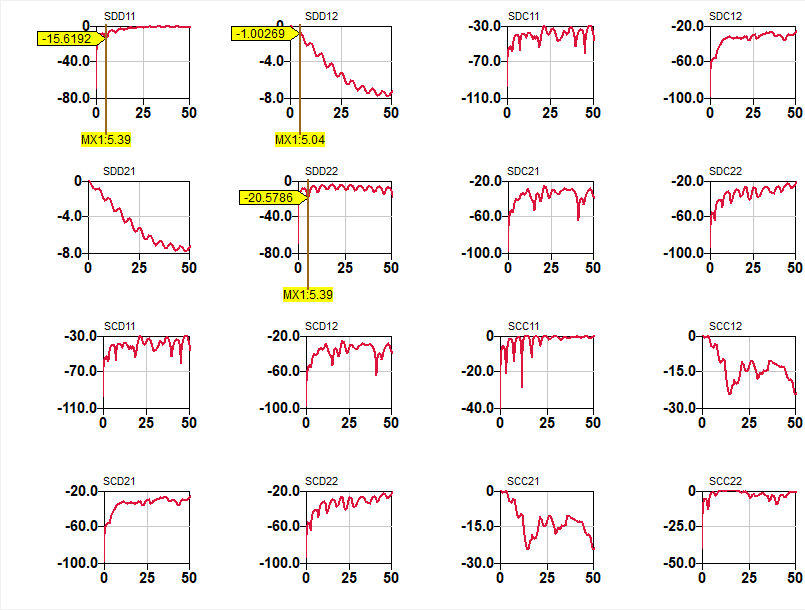

SnpExpert也支持Grid模式顯示所有指標曲線結果:

總結本文通過實際案例介紹了Hermes 3D進行倒裝焊-金線(FC-BW)BGA封裝的電磁場仿真流程,并利用SnpExpert軟件進行S參數分析。 Hermes 3D提供了向導式的建模流程,并簡化了疊層建立與設置。這種方案不需要用戶太過關注復雜的軟件設置,不需要特別了解電磁場仿真原理,使得用戶能夠快速上手,并正確生成仿真模型。

原文標題:【應用案例】如何快速實現倒裝焊-金線混合的BGA封裝建模仿真?

文章出處:【微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

審核編輯:劉清

-

片上系統

+關注

關注

0文章

185瀏覽量

26779 -

SoC芯片

+關注

關注

1文章

608瀏覽量

34874 -

BGA封裝

+關注

關注

4文章

118瀏覽量

17893 -

電磁仿真

+關注

關注

2文章

75瀏覽量

19781

原文標題:【應用案例】如何快速實現倒裝焊-金線混合的BGA封裝建模仿真?

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

BGA芯片的封裝類型 BGA芯片與其他封裝形式的比較

芯片倒裝與線鍵合相比有哪些優勢

如何進行BGA封裝的焊接工藝

【Moldex3D丨產品技巧】使用金線精靈與樣板快速建立金線組件

引腳封裝HotRod和FC-SOT上倒裝芯片的降額和壽命計算

電磁仿真軟件有哪些常用的方法

BGA焊盤設計有什么要求?PCB設計BGA焊盤設計的基本要求

深南電路FC-BGA封裝基板項目穩步推進

WELSIM發布2024R1版本,增強三維電磁場分析

Hermes3D進行倒裝焊-金線(FC-BW)BGA封裝的電磁場仿真流程簡析

Hermes3D進行倒裝焊-金線(FC-BW)BGA封裝的電磁場仿真流程簡析

評論