一,JESD204B應用的優缺點

接觸過FPGA高速數據采集設計的朋友,應該會聽過新術語“JESD204B”。這是一種新型的基于高速SERDES的ADC/DAC數據傳輸接口。隨著ADC/DAC的采樣速率變得越來越高,數據的吞吐量越來越大,對于500MSPS以上的ADC/DAC,動輒就是幾十個G的數據吞吐率,如果依舊采用傳統的CMOS和LVDS已經很難滿足設計要求,因此“JESD204B”應運而生。現在各大廠商的高速ADC/DAC上基本都采用了這種接口。

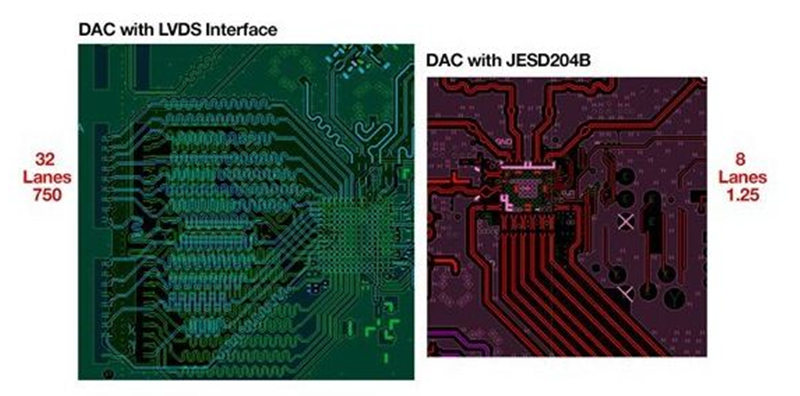

與LVDS及CMOS接口相比,JESD204B數據轉換器串行接口標準可提供一些顯著的優勢,比如更簡單的布局以及更少的引腳數。也因此它獲得了更多工程師的青睞和關注,它具備如下系統級優勢:

1、更小的封裝尺寸與更低的封裝成本:JESD204B不僅采用8b10b編碼技術串行打包數據,而且還有助于支持高達12.5Gbps的數據速率。顯著減少數據轉換器和FPGA上所需的引腳數,從而可幫助縮小封裝尺寸,降低封裝成本;

2、簡化的PCB布局與布線:更少的引腳數可顯著簡化PCB布局與布線,因為電路板上的路徑更少。由于對畸變管理的需求降低,因此布局和布線可進一步簡化。這是因為數據時鐘嵌入在數據流中,并在接收器中與彈性緩沖器結合,無需通過“波形曲線”來匹配長度。下方圖片是JESD204B接口對簡化PCB布局有多大幫助的實例;

3、高靈活布局:JESD204B對畸變要求低,可實現更遠的傳輸距離。這有助于將邏輯器件部署在距離數據轉換器更遠的位置,以避免對靈敏模擬器件產生影響;

4、更簡單的時序控制;

5、滿足未來需求:該接口能夠自適應不同數據轉換器分辨率。對于未來模數轉換器(ADC)及數模轉換器(DAC)而言,無需對TX/RX電路板進行物理上的重新設計。

圖:LVDSDAC的PCB布局(左);采用JESD204B的相同DAC的PCB布局(右)

下表是JESD204B、LVDS接口之間的對比:

既然JESD204B接口的優點如此多,這是不是意味著大家都要選取JESD204B接口了呢?

不一定。與LVDS接口相比,JESD204B的缺點是具有更長的絕對時延,這對于有些應用來說是不可接受的。

盡管JESD204B可提供很多優勢,但有些應用要求極短的時延,最好是無時延。一個很好的實例是電子戰中使用的信號屏蔽器。該設備不僅要求絕對時延,而且需要最大限度地降低任何可能的延遲。

對于這種應用,依舊應該考慮使用LVDS接口,因此它沒有在JESD204B上進行數據串行化的延遲。

二,JESD204B協議相關介紹

1、什么是JESD204B協議

該標準描述的是轉換器與其所連接的器件(一般為FPGA和ASIC)之間的數GB級串行數據鏈路,實質上,具有高速并串轉換的作用。

2、使用JESD204B接口的原因

a.不用再使用數據接口時鐘(時鐘嵌入在比特流中,利用恢復時鐘技術CDR)

b.不用擔心信道偏移(信道對齊可修復此問題,RX端FIFO緩沖器)

c.不用再使用大量IO口,布線方便(高速串行解串器實現高吞吐量)

d.多片IC同步方便

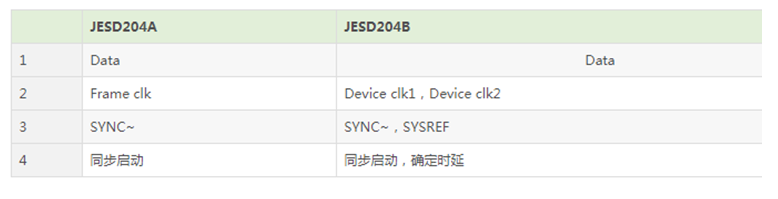

JESD204A和JESD204B參數對比如下圖所示:

3、關鍵變量

M:converters/device,轉換器(AD/DA)數量

L:lanes/device(link),通道數量

F:octets/frame(perlane),每幀的8位字節數

K:frames/multiframe,每個多幀的幀數

N:converterresolution,轉換器分辨率

N’:totalbits/sample,4的倍數,N’=N+控制和偽數據位。

S:samples/converter/framecycle,每個轉換器每幀發送的樣本數。當S=1時,幀時鐘=采樣時鐘

CS:controlbits/sample

CF:controlwords/framecycle/device(link),通常只在HD=1時使用。

4、subclass0~2確定延遲

subclass0:不支持確定延遲;

subclass1:SYSREF,(AD9370支持的是子類1,IP核默認也是子類1),利用確定延遲來對齊多片IC;

subclass2:SYNC~。

5、subclass1的三個階段

A、第一階段,代碼組同步(CGS)

a、RX將SYNC~引腳拉低,發出一個同步請求。

b、TX從下一個符號開始,發送未加擾的/K28.5/符號(每個符號10位)。

c、當RX接收到至少4個無錯誤的連續/K28.5/符號時,RX同步,然后將SYNC~引腳拉高。

d、RX必須接收到至少4個無錯誤8B/10B字符,否則同步將失敗,鏈路留在CGS階段。

e、CGS階段結束,ILAS階段開始。

注意:

a、串行數據傳輸沒有接口時鐘,因此RX必須將其數位及字邊界與TX串行輸出對齊。RX向TX發送~SYNC請求信號,讓其通過所有信道發送一個已知的重復比特序列K28.5。RX將移動每個信道上的比特數據,直到找到4個連續的K28.5字符為止。此時,它不僅將知道比特及字邊界,而且已經實現了CGS。

b、RX~SYNC的輸出必須與RX的幀時鐘同步,同時要求TX的幀時鐘與~SYNC同步(可通過~SYNC復位TX的幀時鐘計數器來實現)。

c、不能使用交流耦合。

B、第二階段,初始通道同步(ILAS):

a、在JESD204B中,發送模塊捕捉到SYNC~信號的變換,在下一個本地多幀(LMFC)邊界上啟動ILAS。

b、ILAS主要對齊鏈路的所有通道,驗證鏈路參數,以及確定幀和多幀邊界在接收器的輸入數據流中的位置。

c、ILAS由4個多幀組成。每個多幀最后一個字符是多幀對齊字符/A,第一,三,四個多幀以/R字符開始,以/A字符結束。接收器以各通道的最后一個字符/A對齊接收器內各通道內各多幀的末尾。

d、這些特定的控制字符只用于初始通路對齊序列中,而不用在數據傳輸的任何其他階段。CGS和ILAS階段不加擾。

e、RX模塊中的FIFO吸收信道偏移。

C、第三階段,數據傳輸階段:

沒有控制字符,獲取鏈路全帶寬。利用字符替換來監視數據同步,多幀計數器LMFC。

6.Deviceclk

系統基準時鐘,提供采樣時鐘,JESD204B時鐘,幀串行器時鐘。產生幀時鐘和多幀時鐘。器件時鐘用來捕捉SYSREF,并完成幀和多幀時鐘的前沿相位對齊。子類1中,多幀時鐘周期必須是器件時鐘的整數倍。ADC/DAC/FPGA可運行于不同速率,但必須同源且頻率相關。

7、同步對齊過程

發送器和接收器各維護一個多幀計數器(LMFC),所有發送器和接收器連接到一個公共(源)SYSREF,這些器件利用SYSREF復位其LMFC,這樣所有LMFC應互相同步(在一個時鐘周期內)。

SYSREFsignal(DeviceSubclass1):

a、確定時延(小于1個多幀時鐘周期)。

b、對齊和器件時鐘同源,LMFC周期的整數倍,在DeviceClk沿變化時采樣SYSREF信號,確定時延,對齊多幀和幀時鐘。SYSREF用于對齊所有收發器件LMFC相位。

SYNC~signal:

同步請求信號。接收端:與接收器幀時鐘同步。CGS后在接收端LMFC邊沿拉高。釋放SYNC(所有器件都會看到)后,發送器在下一次(TX)LMFC繞回0時開始ILAS。如果F*K設置適當,大于(發送器編碼時間)+(線路傳播時間)+(接收器解碼時間),則接收數據將在下一個LMFC之前從接收器的SERDES傳播出去。接收器將把數據送入FIFO,然后在下一個(RX)LMFC邊界開始輸出數據。發送器SERDES輸入與接收器FIFO輸出之間的已知關系稱為確定性延遲。

三,JESD204B具體應用實例

1、相控陣雷達下行同步采集技術應用

多通道數據的同步采集是數字相控陣雷達下行數據接收和處理要解決的關鍵問題。提出了支持JESD204B協議的模數轉換器和支持JESD204B協議的FPGA軟核相結合的設計方案。利用JESD204B協議的確定性延遲特性,只要保證通道間下行數據的相互延遲不超過一個多幀時鐘周期,通過關鍵控制信號的設計和處理,通道間可以實現數據的同步,有效控制板內多片ADC之間進行同步采樣,從而解決數字相控陣雷達下行數據因采集帶來的相位一致性問題。

2、雷達多通道同步采集實現

該設計是一種軟硬件結合的簡化方案,通過合理設計硬件、設計SYSREF信號的扇出控制邏輯,在一定采樣率范圍內滿足JESD204B協議ADC多片多通道之間采樣點相對時延固定,從而確保各通道采集信號相位一致。JESD204B協議支持的確定性延遲特性保證了設計實現。驗證方案的測試電路采用Xilinx K7系列FPGA控制兩片AD9694(采樣率320Msps)同步采集,證實設計方案滿足應用需求。

3、雷達視頻信號同步傳輸設計與實現

以寬帶測向接收機中多波束比幅測向為背景,設計了基于JESD204B協議的高速背板視頻信號同步傳輸方案。時鐘、JESD204B協議參數的設計合理,實現了2塊多通道視頻幅度采集板與1塊數據處理板之間線速率為6.25Gbps的高速同步傳輸,解決了多波束比幅測向前多通道視頻信號傳輸同步問題。

4、高速ADC應用與研究

在成像設備、通信、雷達、工業儀器儀表等需要實時傳輸大量數據的行業中,要求其數模轉換器的采樣率越來越高、數據位越來越大、帶寬越來越寬、傳輸速率越來越快。這對高速數據采集傳輸系統提出了更高的要求。傳統的ADC大多使用并行總線進行數據傳輸,隨著采樣率的提高,捕獲數據量的激增,并行總線的吞吐率需大大提升,這就要增加輸出數據線的位數,而位數的增加需要占用大量的芯片管腳,使芯片和PCB的小型化難以實現并且在大量高速數據信號走線的同時控制電壓噪聲也是難以做到的。

與傳統的并行總線傳輸ADC相比,使用高速串行總線傳輸的ADC具有非常明顯的優勢,其中所需的信號傳輸線大大減少,總線傳輸速率也明顯提升,并且在提高數據傳輸速率的同時節省了布線空間,同時也降低了芯片功耗。使用高速串行總線傳輸的ADC不僅在體積、功耗和數據傳輸速率都比并行總線傳輸的ADC更具優勢。在高速數據采集傳輸系統中,串行總線傳輸的ADC已成為今后的發展趨勢。在研究了高速串行傳輸技術后,設計了基于JESD204B協議的串行總線技術的ADC,并設計了基于此協議的高速ADC采樣電路,該模數轉換芯片支持JESD204BSubclass1工作模式,通過FMC接口與高性能FPGA的GTH接口相連接收ADC采樣后的數據,最終通過PCIE金手指與PC端進行傳輸。

5、JESD204B協議中自同步加解擾電路設計與實現

作為JEDEC最新修訂的AD/DA串行傳輸協議,JESD204B采用自同步擾碼對數據鏈路層原始信號進行隨機化轉換,有效地避免了雜散頻譜產生,減少了物理層誤碼概率.基于經典狀態機結構對JESD204B協議中自同步加擾及解擾電路進行設計實現,根據協議中自同步擾碼的原理細節,提出了一種加擾與解擾狀態電路的設計方案,最終對該方案進行實現、仿真與綜合.仿真與綜合結果表明該方案充分兼容協議控制信號,功能完全符合協議要求,增強了加解擾電路的穩定性與容錯性,同時提高了電路的處理效率,可應用于JESD204B高速串行接口電路設計中。

以上就是關于JESD204B的應用場景的介紹,明德揚可承接基于JESD204B的高速數據傳輸項目,若想了解更多,可聯系。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602006 -

adc

+關注

關注

98文章

6452瀏覽量

544145 -

JESD204B

+關注

關注

5文章

74瀏覽量

19112

發布評論請先 登錄

相關推薦

調試ADS52J90板卡JESD204B接口遇到的問題求解

ADS54J60與JESD204B建立鏈路成功,但有效數據全為0,為什么?

使用JESD204B接口,線速率怎么計算?

如何配置LMK04828時鐘芯片生成JESD204b需要的時鐘?

ADC16DX370 JESD204B串行鏈路的均衡優化

從JESD204B升級到JESD204C時的系統設計注意事項

抓住JESD204B接口功能的關鍵問題

JESD204B協議相關介紹與具體應用實例

JESD204B協議相關介紹與具體應用實例

評論