隨著仿真方法在各種不同大小的 SoC/ASIC 項目中變得越來越流行和負擔得起,問題就出現了,為什么應該在高速原型設計仍然是執行的主要硬件驗證技術的領域中使用仿真。首先要考慮的是速度。

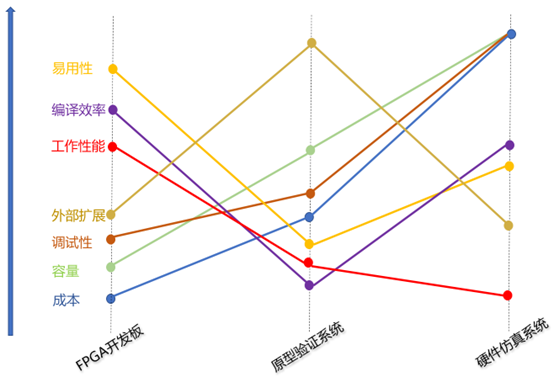

熟悉該主題的人都知道,FPGA 原型設計可以提供最快的設計驗證。當然,由于較長的設計設置時間和較大的工程工作量,存在成本問題。隨著設置工具的改進和變得更易于使用,這種情況正在發生變化。但是,達到最高速度仍然需要更多時間。一些公司甚至根據設計規范在內部設計他們的 FPGA 板,以實現最高的原型制作速度。這使得該過程變得更長,但是,結合軟件分區工具,它肯定會提供最佳的速度結果。

事務級接口

另一個問題是驗證過程的接口級別。要切換到仿真,您必須從位級接口轉到事務級接口。這涉及開發事務級測試平臺和事務到稱為事務器的位級橋接器,需要新的工程技能(以及學習它們的時間)。

幸運的是,仿真供應商為最流行的接口提供了一個現成的事務處理程序庫,并在需要時開發自定義事務處理程序。測試臺問題自然解決了。由于 UVM 方法已在許多 SoC 項目中使用,因此向仿真的轉變是無縫的。UVM 測試平臺本質上也是基于事務的。如果有可用的交易器將其與硬件仿真的設計連接起來,那么遷移到仿真幾乎是無痛的。也許更重要的是,設計本身可以以相同的方式進行測試,使用與仿真相同的一組測試。

除了明顯的好處之外,雖然使用仿真顯著減少了驗證過程的時間,但仿真和仿真中的測試也很容易追蹤。這有助于硬件驗證團隊與設計團隊合作,到目前為止,這一過程在原型設計中被證明是困難的。

失去控制

設計設置的可控性是另一個有爭議的主題。原型設置要求用戶控制分區和時間約束過程,這兩者都是時間密集型的,但用戶保留對過程的控制。相反,仿真提供了自動化所有或大部分過程的設置工具,使原型用戶失去控制和感覺。

解決方案在于為用戶提供調整設置過程的能力,即使是在仿真模式下,至少在影響測試執行速度的領域。對設計的了解可能會在仿真速度方面產生出色的結果。當然,這是工程師習慣的東西和仿真設置過程中可能控制的東西之間的折衷。

JTAG 調試

SoC 設計由處理器驅動,這些處理器通過基于 JTAG 的調試器進行調試和控制,使 JTAG 接口成為原型設計的主要驗證中心。JTAG 電纜將原型開發板與主機 PC 和處理器調試器連接起來。這需要物理布線連接,在需要時速度較慢且難以復制,但可以手動控制接口。

這種傳統方法也可用于仿真,但可以進一步擴展。一旦虛擬 JTAG 事務器可用,電路板和主機 PC 調試器之間就不需要電纜。通過這種處理器類型,可以擁有多個調試接口,所有這些都基于仿真基礎設施,比 JTAG 接口快很多。這種解決方案比傳統的 JTAG 接口調試靈活得多。

何時選擇仿真

只有當 SoC 開發完成并準備好 RTL 代碼后,才能實現原型驗證。這意味著 SoC 的硬件部分必須是完整的。不幸的是,這已經很晚了,特別是對于等待開發平臺的軟件團隊或已經在模擬中驗證了項目并需要通過基于硬件的測試快速反饋的設計團隊。顯然,在可用和需要時之間存在差距。

通過仿真,軟件開發人員和硬件設計人員無需等待完成的設計。可以使用不同類型的測試平臺驗證和測試單獨的模塊和子系統,例如 SystemC 測試平臺、虛擬平臺或流行的 UVM 事務??級測試平臺。仿真不僅使開發團隊能夠在流程的早期開始他們的工作,它還允許在 SoC 級驗證開始之前在塊級驗證 SoC,從而使最后一個階段更容易和更短。通過更進一步并將軟件團隊經常使用的虛擬平臺與硬件模擬器集成,可以在流程的早期開始整個 SoC 驗證,同時逐步增加在模擬器中實現的子系統的數量。

驗證的未來

對速度、接口和調試要求的需求正在慢慢地將原型設計和仿真方法合二為一。在速度方面,沒有必要以最高速度運行整個 SoC;某些部分需要在最快的時鐘域中,而其他部分(例如需要大量調試的部分)可能會運行得更慢。這種快速域是處理器內置子系統和/或高速外部接口,例如以太網或 USB。這些使空間能夠將原型設計和仿真的兩個世界連接成一個,并具有各自的優勢。

隨著原型設計和仿真方法開始相互滲透,它們之間的界限(以及一種方法優于另一種方法的論點)開始消失。現代 SoC 項目的理想驗證解決方案實際上是一種混合硬件-軟件驗證環境,可在需要時提供最高速度、軟件接口靈活性以及在需要時提供調試功能。

審核編輯:郭婷

-

以太網

+關注

關注

40文章

5385瀏覽量

171162 -

usb

+關注

關注

60文章

7903瀏覽量

264053 -

soc

+關注

關注

38文章

4124瀏覽量

217966

發布評論請先 登錄

相關推薦

我們需要怎樣的硬件驗證產品

芯華章生態戰略亮相DAC,發布全流程敏捷驗證管理器FusionFlex,并聯合華大九天推出數模混合仿真解決方案

工廠倉儲環境監測解決方案

西門子數字化工業軟件推出Veloce CS硬件輔助驗證和確認系統

光學雨量計:高精度測量降水量的理想解決方案

新思科技硬件加速解決方案技術日在成都和西安站成功舉辦

虹科新品 | E-Val Pro Plus有線驗證解決方案

E-Val Pro Plus有線驗證解決方案,功能升級,優化制藥流程,確保安全性和合規性!

聯想攜手英偉達,推出混合人工智能方案

康謀方案 | 基于場景的端到端硬件在環(HiL)測試智能解決方案

濕熱滅菌工藝驗證解決方案

混合硬件加軟件驗證環境的理想解決方案

混合硬件加軟件驗證環境的理想解決方案

評論