仿真技術(shù)已經(jīng)存在了很長時間——據(jù)我統(tǒng)計,超過了四十年——行業(yè)觀察家比以往任何時候都更加相信它是 IC 驗證策略中的關(guān)鍵要素,盡管它正在重生。問題是,這個新的仿真時代是什么?為什么硬件仿真多年來一直處于 IC 設(shè)計生態(tài)系統(tǒng)的邊緣,客戶群很少,現(xiàn)在成為片上系統(tǒng)的主流設(shè)計工具( SoC)驗證?答案可以在更大、更復(fù)雜的芯片的出現(xiàn)中找到,這些芯片通常包含多個處理器內(nèi)核并超過 1 億個門。

簡而言之,一種寄存器傳輸級 (RTL) 模擬器,一種首選驗證工具正在受到挑戰(zhàn),因為設(shè)計容量超過了 1 億個門。由于處理器的擴(kuò)展路線圖,更大的門數(shù)是可能的。畢竟,多線程只能做這么多。其次,即使是在 PC 群上并行運行的硬件描述語言(HDL) 軟件模擬器也無法創(chuàng)建可行的選擇,因為被測設(shè)計 (DUT) 環(huán)境本質(zhì)上是連續(xù)的。

另一方面,硬件仿真曾經(jīng)是處理器和圖形芯片等大型 IC 設(shè)計的主要部分,現(xiàn)在正成為一種流行的驗證工具,正是因為它在全芯片驗證方面比 HDL 模擬器運行得更快。硬件仿真工具可以對大型 SoC 設(shè)計進(jìn)行 10 倍以上的驗證,有時比軟件仿真快 10 倍以上。

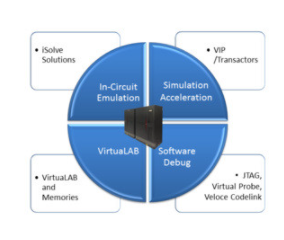

1. Mentor Graphics 的 Veloce2 仿真器平臺支持的密鑰驗證模式視圖。

在過去十年左右的時間里,硬件仿真一直在穩(wěn)步發(fā)展,因為擁有成本正在下降,而仿真工具變得更易于安裝和操作。并且隨著仿真器 ROI 和 SoC 設(shè)計要求的變化,越來越多的 IC 設(shè)計人員傾向于使用仿真工具來調(diào)試硬件和測試軟硬件集成。此外,仿真工具變得更加通用,從將物理設(shè)備連接到仿真器的在線仿真 (ICE) 到更具創(chuàng)新性的協(xié)同仿真解決方案,例如Mentor Graphics 的 VirtuaLab,它可以在當(dāng)今日益增長的功能中虛擬化接口SoC 設(shè)計。

軟件仿真或硬件仿真

模擬器嘗試對 SoC 或系統(tǒng)級設(shè)計的行為進(jìn)行建模,而模擬器則創(chuàng)建設(shè)計的實際實現(xiàn)。在這里,重要的是要注意軟件模擬器和硬件模擬器都用于設(shè)計驗證——這一階段也稱為被測設(shè)計或 DUT——在此階段,編譯器將設(shè)計模型轉(zhuǎn)換為存儲在內(nèi)存中的數(shù)據(jù)結(jié)構(gòu)。

然而,在仿真的情況下,軟件算法使用設(shè)計語言處理表示設(shè)計模型的數(shù)據(jù),而仿真器使用處理器陣列啟用的計算引擎處理數(shù)據(jù)結(jié)構(gòu)。盡管硬件仿真的市場規(guī)模已超過 3 億美元,但這并不意味著它將成為 HDL 仿真工具的終點。

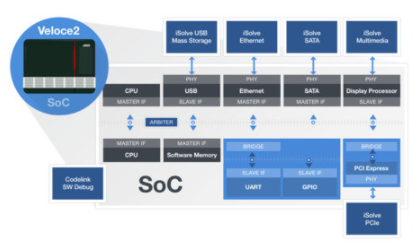

2. Veloce2仿真器同時支持傳統(tǒng)的ICE和基于事務(wù)的驗證,運行多協(xié)議接口的SoC驗證。

基于 HDL 的軟件仿真很可能仍然是首選的驗證引擎,尤其是在驗證過程的早期階段(例如,在 IP 和子系統(tǒng)級別),因為它代表了一種經(jīng)濟(jì)、易于使用且快速上手的方法- 設(shè)置 EDA 工具。另一方面,仿真將在更大的 SoC 設(shè)計中獲得牽引力,這些設(shè)計包含數(shù)百萬個驗證周期并且很難找到硬件錯誤。換言之,在可預(yù)見的未來,SoC 和系統(tǒng)級設(shè)計驗證的兩個 EDA 工具市場將共存。

審核編輯:郭婷

-

soc

+關(guān)注

關(guān)注

38文章

4122瀏覽量

217948 -

仿真器

+關(guān)注

關(guān)注

14文章

1016瀏覽量

83644 -

eda

+關(guān)注

關(guān)注

71文章

2709瀏覽量

172899

發(fā)布評論請先 登錄

相關(guān)推薦

【「數(shù)字IC設(shè)計入門」閱讀體驗】+ 概觀

無人機(jī)飛行仿真模擬訓(xùn)練系統(tǒng)

教學(xué)驗證丨BUCK電路仿真驗證

Lint靜態(tài)驗證工具如何助力IC設(shè)計

仿真器的使用方法有哪些

電磁仿真軟件有哪些常用的方法

模擬電路仿真軟件中電阻咋找

北京清微智能科技有限公司發(fā)布IC驗證新方法,實現(xiàn)雙DUT驗證

仿真和模擬用于IC驗證的方法

仿真和模擬用于IC驗證的方法

評論