任何學科的設計——電子、機械、航空航天等——都始于一個規范,該規范捕捉最終產品應該做什么,并從根本上推動整個開發周期。在開發的早期階段,第一個任務使用規范來驗證正在開發的設計是否正常工作并且沒有錯誤。然后,當設計的所有部分都組裝成一個完整的系統時,第二個任務使用規范來確定系統是否也按照預期的方式運行。

廣告:

航空航天、機械

這兩個任務稱為設計驗證(任務 1)和設計驗證(任務 2)。有時,錯誤地,這兩個術語可以互換使用。雖然相似,但這兩項任務的目標卻截然不同。

驗證:我們構建的系統正確嗎?

驗證:我們是否在構建正確的系統?

在片上系統 (SoC) 設計過程中,使用基于軟件的硬件描述語言 (HDL) 仿真方法進行設計驗證。相反,設計驗證是在實際使用環境中測試的整個系統的原型上進行的。

不幸的是,HDL 仿真執行速度并沒有跟上設備的復雜性,盡管它具有所有優點:易用性、靈活性和快速的設計迭代時間。當今的許多設計,例如具有 1,024 個端口的互聯網路由器或高清視頻處理器,都需要大量的驗證序列,即使在最快的 PC 上模擬也需要很多年。這些序列源于運行長的、連續的串行協議流或處理復雜的嵌入式軟件以全面驗證 SoC 或系統設計的需要。

此外,近年來,在硅可用之前開始軟件驗證已變得很重要。為了實現這一目標,引入了一種稱為虛擬原型的新型方法。雖然其中一些工具已經實現了啟動軟件開發的目標,但它們只處理不需要準確表示底層硬件的應用程序。在測試嵌入式軟件(例如固件、設備驅動程序、操作系統和診斷程序)的交互時,它們會出現不足。對于此測試,嵌入式軟件開發人員依靠準確的硬件模型來驗證他們的代碼。

相比之下,硬件設計人員需要一套相當完整的軟件來在系統驗證期間全面測試他們的 SoC。古老的基于 FPGA 電路板的系統原型設計方法提供了設計的準確表示,但不太適合硬件調試。因此,只要設計適合少數 FPGA,FPGA 原型對軟件開發團隊的吸引力就更大。

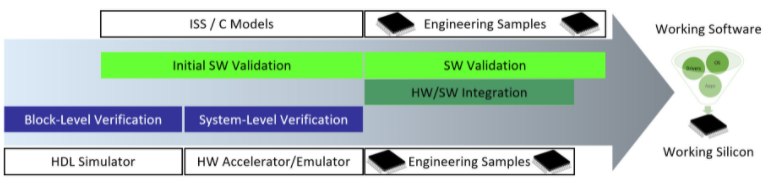

最終,軟件和硬件組需要在一個通用模型上走到一起,以驗證完整的硬件和嵌入式軟件。對于大多數使用傳統開發周期的人來說,第一個完整的模型是實際的硅片(圖 1)。

【圖1 | 在傳統的開發周期中,第一個完整的模型是硅。]

等待實際硅片的問題在于它在設計周期中為時已晚。由于嵌入式軟件無法在完整、準確的系統模型的上下文中得到充分驗證,直到硅片,所以在硅片中發現問題的可能性增加。它們可以在軟件或軟件和硬件中找到,通常會迫使額外的芯片重新設計和代碼修訂。重新設計和代碼修訂都具有成本和上市時間的影響。避免這些影響所需要的是一種提供統一解決方案的方法,以在第一塊芯片之前實現硬件/軟件驗證和確認。

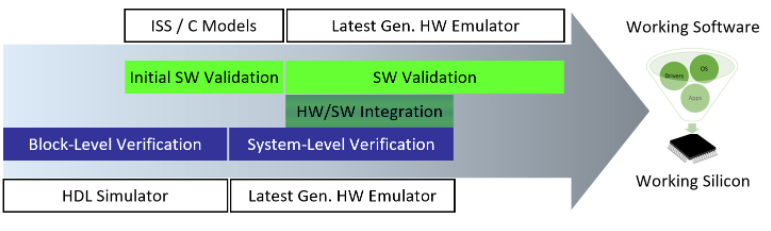

最新一代的硬件仿真器實現了這一點。它們提供幾乎無限的容量,多達數十億個門,并以 1 兆赫或更多兆赫的速度驗證被測設計 (DUT),提供比 FPGA 原型系統更好的硬件調試。它們易于使用,可以更快地編譯 DUT,并允許從世界任何地方進行 24/7 遠程訪問。在仿真器上運行的新軟件應用程序使其能夠支持多種類型的驗證,從低功耗分析和驗證到測試設計 (DFT) 邏輯驗證。仿真器還為從網絡到處理器/圖形、存儲等各種細分市場帶來了獨特的技術。

在設計周期的早期,仿真器用于與仿真器和 SystemVerilog 進行協同仿真,以在組裝完整的 SoC 設計之前驗證知識產權 (IP) 模塊和子系統。在設計周期的后期,仿真器用于驗證整個系統并執行嵌入式軟件驗證。

它們在相同的設計表示上為硬件和軟件工程師提供完整的硬件和軟件調試功能。這讓硬件和軟件開發團隊能夠以前所未有的方式協作并修復集成問題(圖 2)。

【圖2 | 最新一代的硬件仿真器顯著加快了開發周期。]

硬件仿真以前僅限于驗證超大型設計,如今已成為所有設計驗證和確認流程的基礎。這種新發現的流行是日益增長的硅復雜性和嵌入式軟件的廣泛使用的結果。在設計中心,硬件仿真被使用,并且在未來它將在從硬件驗證、硬件/軟件集成到嵌入式軟件和系統驗證的整個開發周期中使用得更多。

審核編輯:郭婷

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602004 -

嵌入式

+關注

關注

5071文章

19026瀏覽量

303494 -

仿真器

+關注

關注

14文章

1016瀏覽量

83647

發布評論請先 登錄

相關推薦

硬件仿真在嵌入式軟件和系統驗證中的應用

硬件仿真在嵌入式軟件和系統驗證中的應用

評論