系統(tǒng)變得越來越小,越來越復(fù)雜,許多不同的功能組合在一個芯片上。多個芯片之間有更多的通信。即使是什么構(gòu)成了錯誤,定義也變得更加復(fù)雜。

更大、更復(fù)雜的系統(tǒng)意味著調(diào)試、故障排除或微調(diào)設(shè)備的過程更長、更艱巨。如果一個組織需要幾個月的時間來調(diào)試,那可能會導(dǎo)致幾個月的收入損失。

很少有人愿意為調(diào)試支付額外費(fèi)用。這是一種必要的邪惡。任何可以最大限度減少調(diào)試影響的措施都是有價值的。MIPI 聯(lián)盟廣泛的標(biāo)準(zhǔn)化調(diào)試和跟蹤規(guī)范組合旨在簡化物聯(lián)網(wǎng) (IoT)、汽車、5G 和其他應(yīng)用領(lǐng)域的移動系統(tǒng)開發(fā)。

分層的、系統(tǒng)的方法

MIPI 采用分層方法進(jìn)行調(diào)試和跟蹤,從硬件的最低層一直到軟件層。這個想法是讓組織能夠挑選和選擇它需要的規(guī)范,戰(zhàn)略性地將它們放入其開發(fā)環(huán)境中,然后圍繞標(biāo)準(zhǔn)分層的接口和協(xié)議集添加自己的附加值。九個 MIPI 調(diào)試和跟蹤規(guī)范的組合最近公開可供下載:

MIPI Gigabit Debug for IP Sockets (MIPI GbD IPS) v1.0 — MIPI GbD IPS 是一種適配器,用于促進(jìn)從智能手機(jī)到物聯(lián)網(wǎng)端點的所有類型連接設(shè)備的遠(yuǎn)程調(diào)試。

MIPI Gigabit Debug for USB (MIPI GbD USB) v1.1 — MIPI GbD USB 最大限度地減少了調(diào)試對系統(tǒng)功能的影響,并使工程師能夠在連接傳輸其他流量時使用 USB 連接來調(diào)試設(shè)備。

MIPI 高速跟蹤接口 (MIPI HTI) v1.0 — MIPI HTI 是數(shù)據(jù)端口的串行實現(xiàn),通過在裸露中重用這些接口的低級物理高速部分來利用可用的高速串行接口技術(shù)-金屬環(huán)境。通過這種方式,與并行實現(xiàn)相比,MIPI HTI 以更少的 I/O 引腳提供了更高的傳輸帶寬。

MIPI Narrow Interface for Debug and Test (MIPI NIDnT) v1.2 — MIPI NIDnT 標(biāo)準(zhǔn)化了設(shè)備上功能端口的使用,以進(jìn)行調(diào)試和測試過程。該規(guī)范旨在通過最大限度地減少對昂貴的專有測試工具的依賴,使開發(fā)人員更容易識別復(fù)雜設(shè)計中的問題并降低開發(fā)成本。設(shè)計人員可以在移動設(shè)備和受移動設(shè)備影響的設(shè)計中廣泛使用的其他接口上執(zhí)行調(diào)試和測試的多功能性。

MIPI Parallel Trace Interface (MIPI PTI) v2.0 — MIPI PTI 是具有多個數(shù)據(jù)信號和時鐘的并行接口,用于將有關(guān)系統(tǒng)功能和行為的跟蹤數(shù)據(jù)導(dǎo)出到主機(jī)系統(tǒng)進(jìn)行分析和顯示。

MIPI SneakPeek 協(xié)議 (MIPI SPP) v2.0 — MIPI SPP 允許在調(diào)試測試系統(tǒng) (DTS) 和移動終端目標(biāo)系統(tǒng) (TS) 之間進(jìn)行通信,便于 DTS 內(nèi)的軟件調(diào)試 TS 操作。用戶減少對專用調(diào)試通信接口的依賴,并利用熟悉的地址映射讀寫事務(wù)機(jī)制來觀察、詢問和調(diào)整 TS。

MIPI System Trace Protocol (MIPI STP) v2.2 — MIPI STP作為通用基礎(chǔ)協(xié)議開發(fā),可由多個特定于應(yīng)用程序的跟蹤協(xié)議共享,允許其數(shù)據(jù)流與用于傳送有關(guān)處理器程序的數(shù)據(jù)的高度優(yōu)化的協(xié)議共存流、定時或低級總線事務(wù)。

MIPI System Software-Trace (MIPI SyS-T),v1.0 — MIPI SyS -T 是一種通用數(shù)據(jù)格式,用于在測試系統(tǒng)和片上系統(tǒng) (SoC) 等設(shè)備之間傳輸軟件跟蹤和調(diào)試信息) 或平臺。它提供了一種方便的方法——與供應(yīng)商或操作系統(tǒng) (OS) 無關(guān)——在軟件、固件或硬件實現(xiàn)之間交換調(diào)試信息。

MIPI Trace Wrapper Protocol (MIPI TWP) v1.1 — MIPI TWP 允許將多個源跟蹤流折疊成單個跟蹤流。源字節(jié)流被分配了系統(tǒng)唯一標(biāo)識,并且包裝協(xié)議封裝了系統(tǒng)中的所有流。

MIPI 調(diào)試工作組遵循了許多不同的策略,以盡量減少調(diào)試和跟蹤過程的影響。例如,減少專用接口對于物聯(lián)網(wǎng)和其他移動應(yīng)用程序空間尤其重要,因為在這些空間中,用戶無法將主要空間用于額外的引腳和額外的尺寸。具有重用接口和利用功能接口的能力解決了有效使用不動產(chǎn)的需求,因此這一要求通知了工作組對 MIPI 調(diào)試和跟蹤規(guī)范的開發(fā)和改進(jìn)。

此外,在開發(fā)調(diào)試和跟蹤規(guī)范時,MIPI 力求:

最大限度地降低引腳成本并提高基本調(diào)試接口的性能

提高高性能接口的帶寬、功能和可靠性,以便將高帶寬、單向處理器跟蹤數(shù)據(jù)導(dǎo)出到調(diào)試工具

部署具有高帶寬需求所需性能的物理穩(wěn)健調(diào)試連接器

開發(fā)通用跟蹤協(xié)議,允許將許多不同的片上跟蹤源封裝到單個跟蹤數(shù)據(jù)流中

最大限度地提高現(xiàn)場系統(tǒng)中的調(diào)試可見性

利用移動系統(tǒng)的新高帶寬功能接口進(jìn)行調(diào)試傳輸

騰出時間專注于增值

通過專注于限制用于移動數(shù)據(jù)的框架和協(xié)議的影響以及為調(diào)試和跟蹤過程提供控制,MIPI 讓芯片供應(yīng)商和原始設(shè)備制造商 (OEM) 能夠最大限度地利用這些標(biāo)準(zhǔn)化管道,然后投資于更高價值的產(chǎn)品有助于提高吞吐量的活動。

比如圍繞trace的規(guī)范;MIPI PTI、MIPI HTI、MIPI STP、MIPI TWP 和 MIPI SysS-T 對于為系統(tǒng)設(shè)計人員和開發(fā)人員提供嵌入式系統(tǒng)行為的可見性而言尤為重要。

嵌入式 SoC 上的流接口可用于將有關(guān)系統(tǒng)功能和行為的數(shù)據(jù)導(dǎo)出到主機(jī)系統(tǒng)進(jìn)行分析和顯示。監(jiān)視處理器指令和數(shù)據(jù)流的組件、在處理器上運(yùn)行的軟件中的檢測或監(jiān)視處理器外部活動的組件可以提供允許開發(fā)人員重建或“跟蹤”系統(tǒng)活動的某些方面的數(shù)據(jù)。一個或多個嵌入式處理器的指令執(zhí)行序列、嵌入式處理器內(nèi)核進(jìn)行的數(shù)據(jù)總線事務(wù)、系統(tǒng)互連上的事務(wù)快照或來自檢測應(yīng)用程序代碼的流式輸出都是此類跟蹤數(shù)據(jù)的示例。這種可見性的重要性隨著物聯(lián)網(wǎng)、汽車、5G、

通過公開規(guī)范,MIPI 使開發(fā)人員、工具供應(yīng)商和其他人能夠圍繞調(diào)試通信和跟蹤數(shù)據(jù)建立價值。通過這種方式,它可以讓強(qiáng)大的生態(tài)系統(tǒng)生根發(fā)芽,進(jìn)一步拓寬規(guī)范的互操作性并豐富圍繞它們的開發(fā)環(huán)境。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19170瀏覽量

229178 -

物聯(lián)網(wǎng)

+關(guān)注

關(guān)注

2903文章

44293瀏覽量

371367 -

MIPI

+關(guān)注

關(guān)注

11文章

308瀏覽量

48565

發(fā)布評論請先 登錄

相關(guān)推薦

C2000 ePWM開發(fā)人員指南

嵌入式系統(tǒng)怎么學(xué)?

鴻蒙開發(fā)系統(tǒng)基礎(chǔ)能力:ohos.hiTraceChain 分布式跟蹤

嵌入式開發(fā)就業(yè)前景怎么樣?

芯海 32 位 MCU 開發(fā)調(diào)試 ,基于 VS Code 插件實現(xiàn)芯海 32 位 MCU 開發(fā)調(diào)試

三星停止自動駕駛研究,開發(fā)人員轉(zhuǎn)到機(jī)器人領(lǐng)域

MWC2024亮點 愛立信旗下Vonage攜手AWS加速向數(shù)百萬開發(fā)人員提供新的解決方案

adb是什么軟件 adb調(diào)試干什么用的

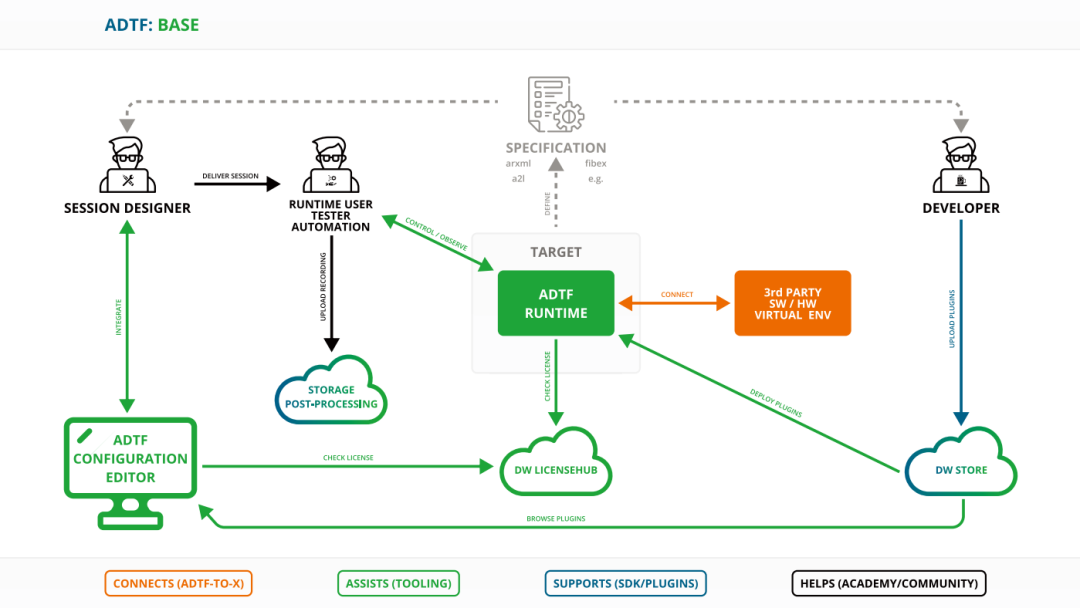

康謀方案 | 加速自動駕駛系統(tǒng)開發(fā)的技術(shù)解決方案

介紹6種常見的反調(diào)試方法

SEGGER調(diào)試低功耗模式

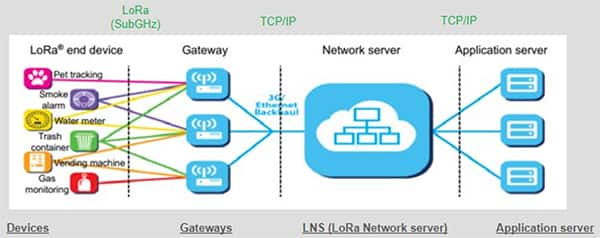

利用經(jīng)過認(rèn)證的 LoRaWAN 模塊加速遠(yuǎn)距離連接的開發(fā)

EEPROM為什么會成為嵌入式系統(tǒng)開發(fā)理想選擇

USB調(diào)試模式是什么意思?USB調(diào)試模式有什么用?

如何通過Tracealyzer實現(xiàn)Linux系統(tǒng)的跟蹤?

增強(qiáng)系統(tǒng)開發(fā)人員的調(diào)試和跟蹤能力

增強(qiáng)系統(tǒng)開發(fā)人員的調(diào)試和跟蹤能力

評論