在Versal新一代ACAP器件上,除了延續之前Ultrascale/Ultrascale+系列器件上已有的DDR4 IP之外,還配置了最新的DDR4/LPDDR4 硬核控制器 (NOC IP)。它的性能更高,并且不額外占用其他的可編程邏輯資源 (PL)。使用它的時候,在硬件設計方面和設計流程上,和之前的軟核控制器(DDR4 IP)也有著很大的不同。今天我們來介紹一下I/O planning方面的設計考慮和實現流程。

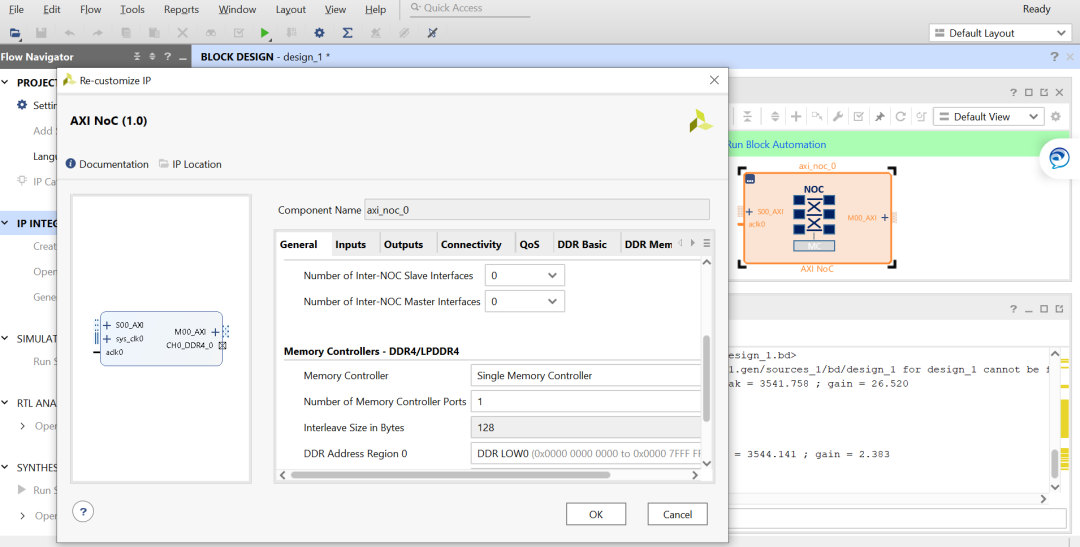

在原理圖設計之前,需要先新建一個測試小工程,在block design中添加NOC IP。

在IP wizard中,根據 memory 容量,位寬,帶寬等要求完成相關配置。

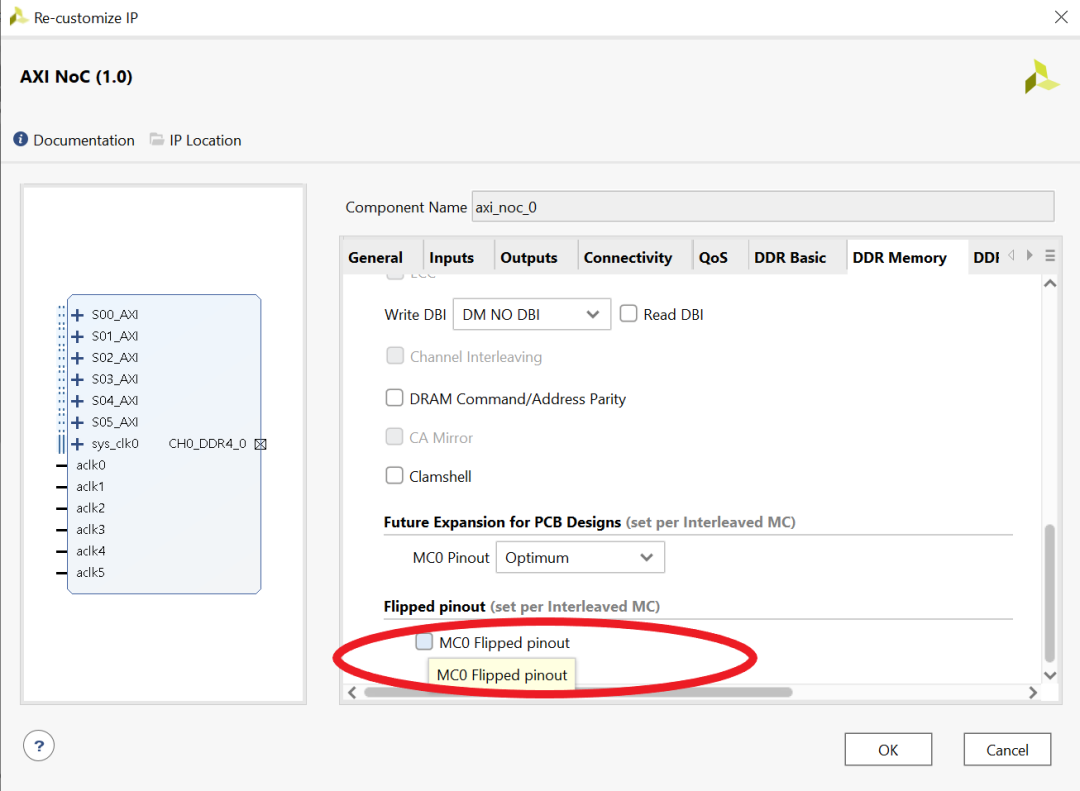

總體上來講,DDR4/LPDDR4的管腳有2種分配模式:Flipped和Non-flipped,模式的選擇可以通過使能或者關閉 NOC IP 中 “Flipped pinout”的選項來實現。

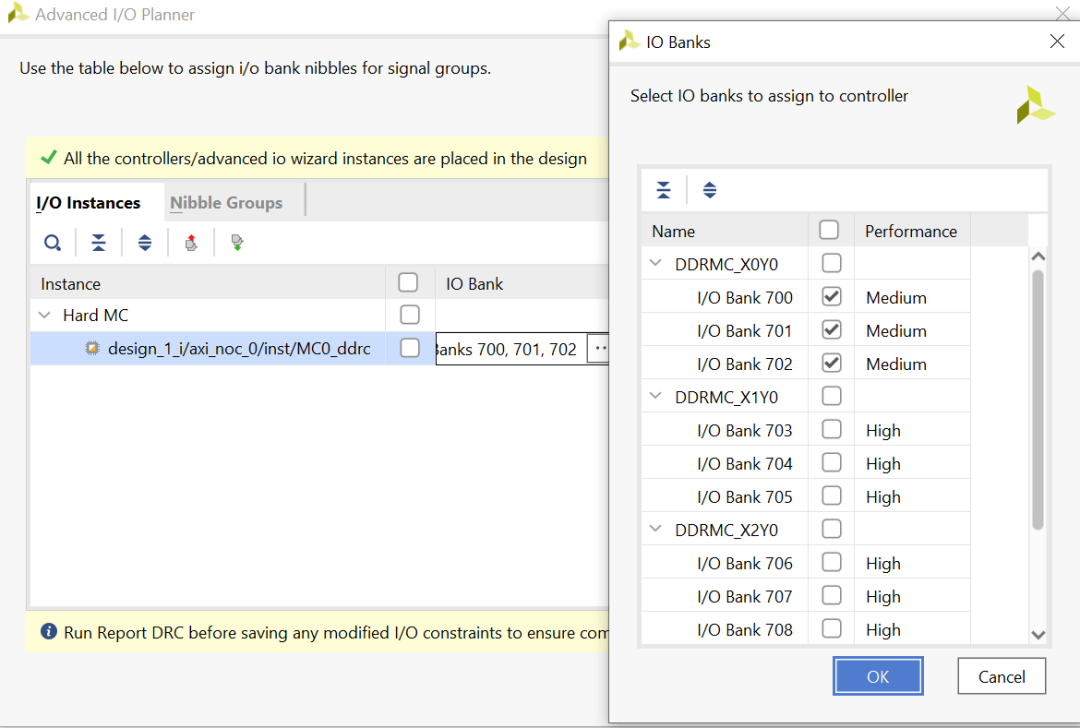

Versal 器件上每個NOC IP對應3個IO bank的管腳,它們都位于同一個triplet之中。一個NOC IP對應的所有DDR4/LPDDR4接口管腳都必須放置在這3個IO bank之中。在對 block design進行綜合之后,打開synthesized design,在I/O ports窗口中點擊 “Open advanced I/O planner” ,按照bank或者nibble為單位指定所有管腳的位置。

在此之后,地址、控制和時鐘管腳的位置就被固定了下來。數據管腳在Byte以內和Byte之間可以進行微調,具體的調整規則可以參考pg313中Pinout Rules相關章節。

PG313:

https://docs.xilinx.com/r/en-US/pg313-network-on-chip

審核編輯:湯梓紅

-

控制器

+關注

關注

112文章

15896瀏覽量

175417 -

DDR4

+關注

關注

12文章

317瀏覽量

40560 -

LPDDR4

+關注

關注

1文章

36瀏覽量

23349 -

Versal

+關注

關注

1文章

151瀏覽量

7598

原文標題:開發者分享|Versal DDR4/LPDDR4 硬核控制器 (NOC IP) I/O planning快速指南

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

淺析DDR,DDR2,DDR3,DDR4,LPDDR區別

MT53E256M32替換LPDDR4,是否需要重新運行DDR工具以生成要在LPDDR4控制器中編程的新bin文件?

i.MX 8M Nano UltraLite Quad LPDDR4校準失敗的原因?

lpddr4頻率無法修改怎么解決?

DDR4,什么是DDR4

使用用戶為 LPDDR4 和 x8 或 x16 DDR4 組件接口指定的 DQS 字節交換生成管腳分配時,其中可能包含錯誤且需更改

Versal ACAP DDRMC-DDR4、LPDDR4和LPDDR4X外部參考時鐘設計指南

LPDDR4是什么意思?LPDDR4X內存是什么意思?

DDR4、LPDDR4和LPDDR4x的區別

具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內存電源解決方案數據表

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據表

DDR4/LPDDR4硬核控制器I/O plannin的設計和實現

DDR4/LPDDR4硬核控制器I/O plannin的設計和實現

評論