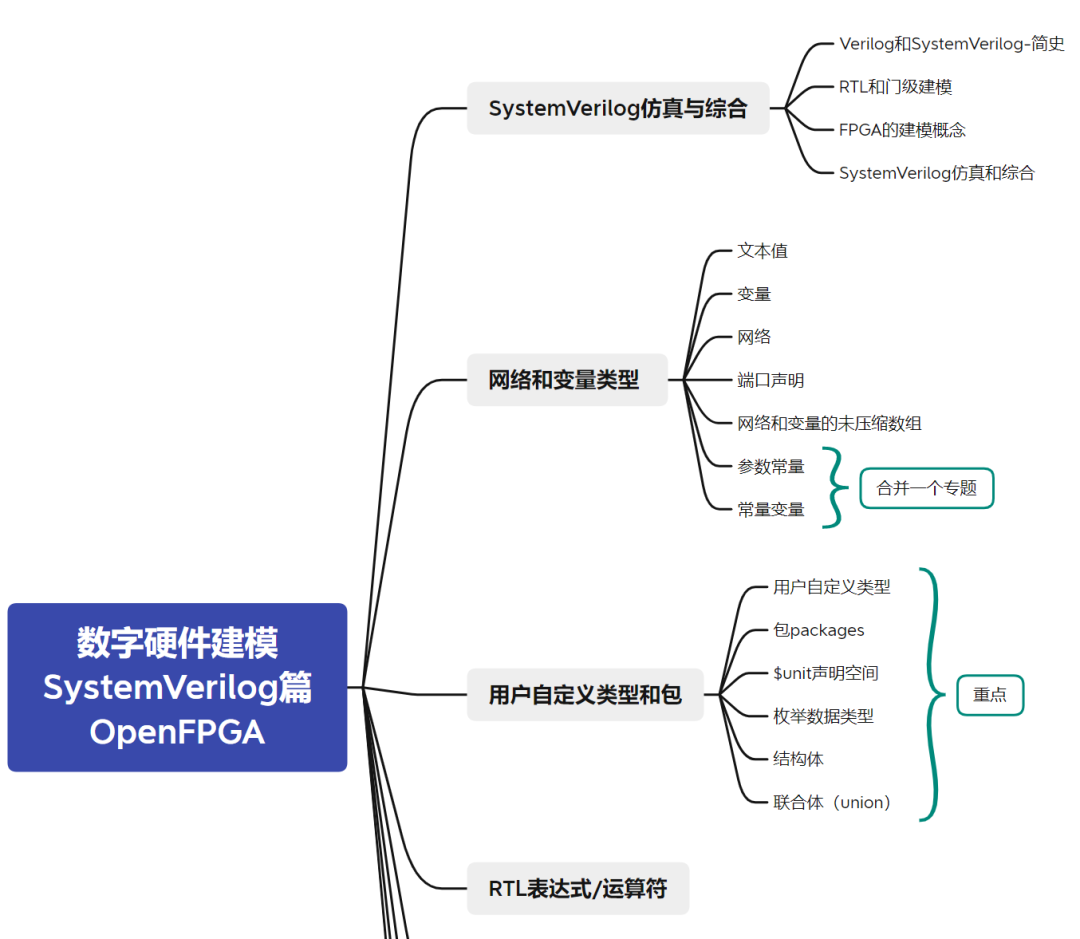

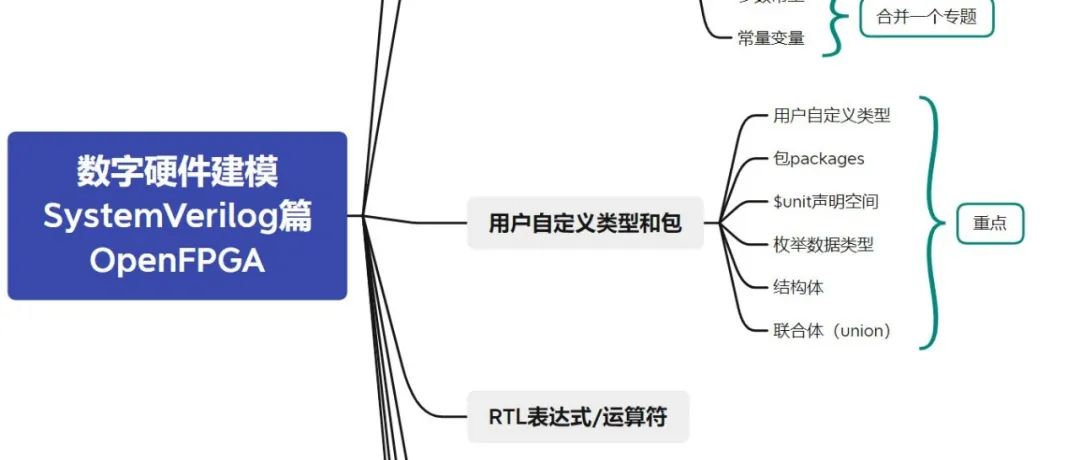

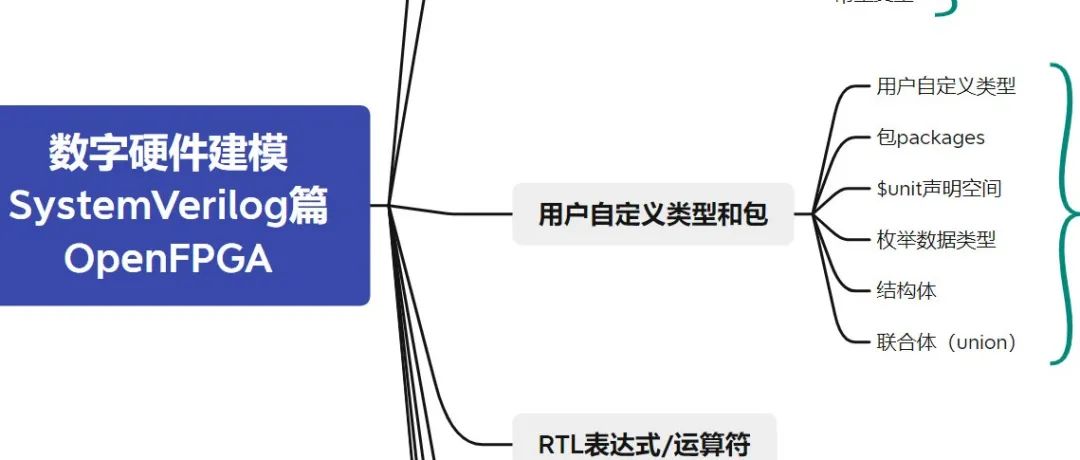

數字硬件建模SystemVerilog-聯合體(union)

聯合體(union)

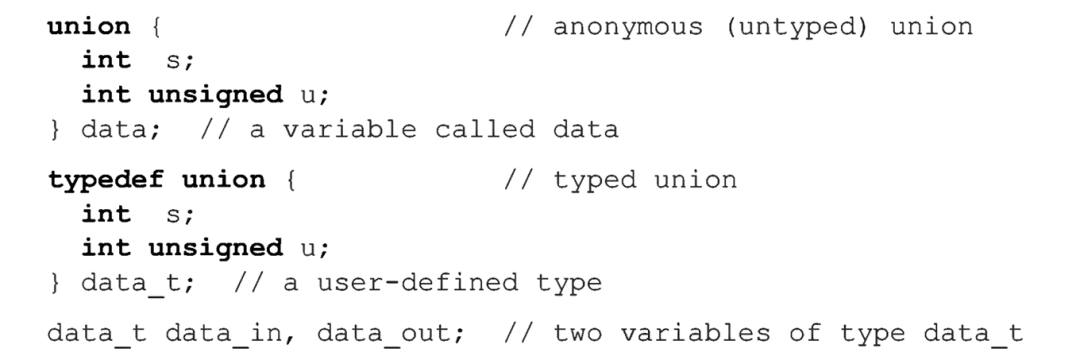

聯合體是一個可以有多個數據類型表示的單個存儲元素,聯合體的聲明類似結構體,但推斷出的硬件非常不同。結構體是幾個變量的集合。union是單個變量,可以在不同的時間使用不同的數據類型。union可以存儲的變量類型列在大括號({})之間,每個變量類型都有一個名稱:

在本例中,變量是data。data變量有兩種可能的數據類型:名為s的有符號整數類型,或名為u的無符號整數值。

在RTL建模中,聯合體的一個典型應用是,一個值可以表示為幾種不同的類型,但在任何特定的時鐘周期中只能表示為一種類型。例如,數據總線有時可能使用用戶網絡接口(UNI,User NetworkInterface)電信協議發送數據包,而在其他時間,同一數據總線可能使用網絡到網絡接口(NNI,Network to Network Interface)電信協議發送數據包。SystemVerilog聯合體可以代表同一總線的這種雙重用途。聯合體的另一個用途是表示共享硬件資源,例如可以在不同時間存儲不同類型數據的硬件寄存器。

自定義和匿名聯合體

同結構體一樣, 聯合體可以使用 typedef 來定義, 按這種方式定義的是自定義聯合體。如果沒有使用 typedef,就是匿名聯合體.

匿名聯合體和自定義聯合體都是可綜合的,但自定義聯合體在RTL建模方面有優勢。自定義聯合體可以是:

用于聲明多個變量,如上例中的數據輸入和數據輸出。

用作模塊端口類型。

在一個包中定義,然后在多個模塊中使用。

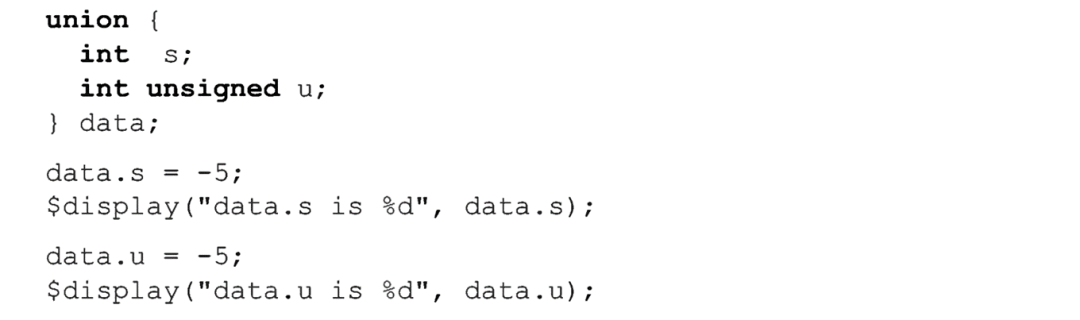

分配和讀取聯合體變量

引用聯合體的數據類型時,使用聯合體的名稱,后跟表示數據類型的名稱,并用句點(.)分隔(同結構體一樣)。

在本例中,變量數據有兩種可能的數據類型,每個表示中都存儲了-5。data.s數據類型將打印為-5,一個有符號整數值。data.u數據類型將打印為4294967291,一個無符號整數值。

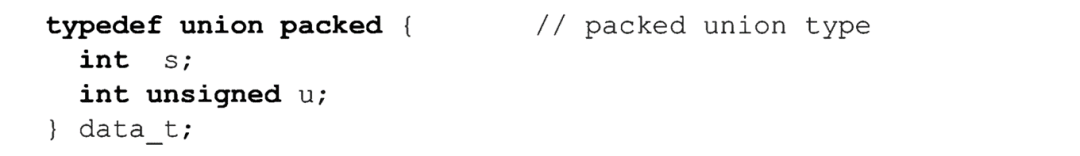

非壓縮聯合體和標記的聯合體

最佳做法準則4-4

在RTL建模中僅使用壓縮聯合體。

SystemVerilog有三種類型的聯合體:非壓縮聯合體、壓縮聯合體和標簽聯合體,大多數綜合編譯器只支持壓縮聯合體。

大多數綜合編譯器不支持非壓縮和標簽聯合體。這些聯合體類型可以代表任何數據類型的存儲,包括不可綜合的數據類型。非壓縮的聯合體體和標簽聯合體體可用于建模測試臺和高級抽象模型,但不應用于RTL建模。

通過在union關鍵字后添加關鍵字Packed來定義壓縮聯合體:

壓縮聯合體是可綜合的。壓縮聯合體對聯合體可以表示的數據類型有很多限制。這些限制與硬件行為密切相關。在壓縮聯合體中,它只能表示向量類型,并且聯合體可以存儲的每個數據類型的向量寬度必須相同。這確保了無論存儲值的數據類型如何,壓縮聯合體都將以相同的位數表示其存儲。

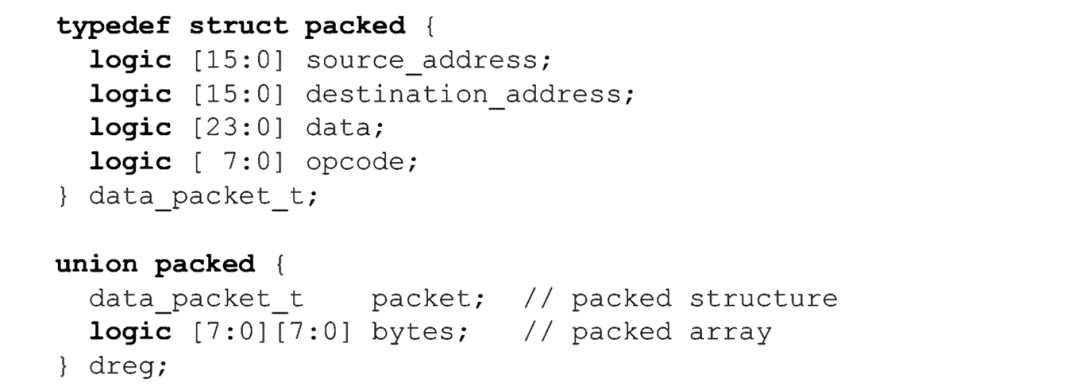

壓縮聯合體允許使用一種格式寫入數據,并使用另一種格式讀回數據。設計模型不需要進行任何特殊處理來跟蹤數據的存儲方式,這是因為壓縮聯合體中的數據總是使用相同的位數存儲。下面的示例定義了一個壓縮聯合體,其中一個值可以用兩種方式表示:數據包(使用壓縮結構體)或連續字節數組,

圖4-3說明了dreg的兩種數據類型是如何表示的。

圖4-3:具有相同存儲的兩種表示形式的壓縮聯合體

因為聯合體是壓縮的,所以無論使用哪種聯合體表示,信息都將使用相同的位對齊來存儲。這意味著可以使用bytes格式(可能來自字節的串行輸入流)加載一個值,然后使用data_packet格式讀取相同的值,

通過端口將壓縮聯合體傳遞給任務和函數

自定義聯合體(使用typedef定義的聯合體)可以用作模塊端口和任務/函數參數的數據類型。非壓縮的聯合體要求將相同的聯合體類型用于端口的外部連接,或用于傳遞給任務或函數參數的外部信號。壓縮聯合體只能表示壓縮數據類型,這允許任何向量類型用于外部連接或外部值。

示例4-6顯示了一個包含結構體和聯合體定義的包。示例4-7在一個簡單算術邏輯單元(ALU)模型中使用了這個包,ALU可以對有符號或無符號的值進行操作,但不能同時對兩者進行操作,一個標志用于指示操作數據是有符號的還是無符號的。ALU操作碼、兩個操作數和一個有符號標志作為單個指令字傳遞到ALU中,用結構體表示。ALU輸出是單個值,可以表示有符號或無符號值,建模為這兩種類型的并集。這允許相同的輸出端口用于不同的數據類型:

示例4-6:包含結構體和聯合體定義的包

// //Packagewithunionandstructuredefinitions // //`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords `define_4bit//use4-bitdatafortestingsynthesis //`define_32bit//use32-bitdatawordsize //`define_64bit//use64-bitdatawordsize packagedefinitions_pkg; `ifdef_4bit typedeflogic[3:0]uword_t; typedeflogicsigned[3:0]sword_t; `elsif_64bit typedeflogic[63:0]uword_t; typedeflogicsigned[63:0]sword_t; `else//defaultis32-bitvectors typedeflogic[31:0]uword_t; typedeflogicsigned[31:0]sword_t; `endif typedefenumlogic[2:0]{ADD,SUB,MULT,DIV}op_t; typedefenumlogic{UNSIGNED,SIGNED}operand_type_t; //Packedunionrepresentsavariablethatcanstore //differenttypes typedefunionpacked{ uword_tu_data; sword_ts_data; }data_t; //Packedstructurerepresentsacollectionofvariables //thatcanreferencedandpassedthroughportsasagroup typedefstructpacked{ op_topcode; operand_type_top_type; data_top_a; data_top_b; }instruction_t; endpackage:definitions_pkg //`end_keywords示例4-7:帶結構體和聯合體端口的算術邏輯單元(ALU)

// //Modulewithstructureinputportandunionoutputport // //`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords modulealu importdefinitions_pkg::*;//wildcardimportthepackage (inputlogicclk,rstN, inputinstruction_tiw,//inputisastructure outputdata_talu_out//outputisaunion ); timeunit1ns;timeprecision1ns; always_ff@(posedgeclkornegedgerstN)//asyncreset if(!rstN)//active-low alu_out<=?'0; ???else?begin:?alu_operations? ?????if?(iw.op_type?==?SIGNED)?begin:?signed_ops? ???????case?(iw.opcode) ?????????ADD?:?alu_out.s_data?<=?iw.op_a.s_data ?????????????????????????????????+?iw.op_b.s_data; ?????????SUB?:?alu_out.s_data?<=?iw.op_a.s_data ?????????????????????????????????-?iw.op_b.s_data; ?????????MULT:?alu_out.s_data?<=?iw.op_a.s_data ?????????????????????????????????*?iw.op_b.s_data; ?????????DIV?:?alu_out.s_data?<=?iw.op_a.s_data ?????????????????????????????????/?iw.op_b.s_data; ???????endcase? ?????end:?signed_ops? ?????else?begin:?unsigned_ops? ???????case?(iw.opcode) ?????????ADD?:?alu_out.u_data?<=?iw.op_a.u_data ?????????????????????????????????+?iw.op_b.u_data; ?????????SUB?:?alu_out.u_data?<=?iw.op_a.u_data ?????????????????????????????????-?iw.op_b.u_data; ?????????MULT:?alu_out.u_data?<=?iw.op_a.u_data ?????????????????????????????????*?iw.op_b.u_data; ?????????DIV?:?alu_out.u_data?<=?iw.op_a.u_data ?????????????????????????????????/?iw.op_b.u_data; ???????endcase? ?????end:?unsigned_ops? ???end:?alu_operations? endmodule:?alu `end_keywords?

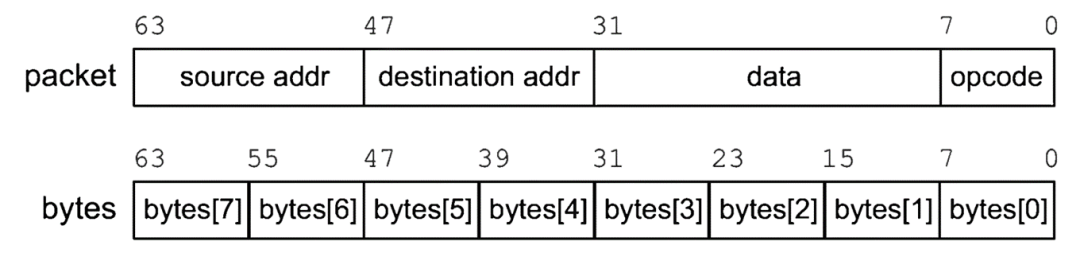

圖4-4顯示了綜合該示例的結果。說明了在RTL模型中使用結構體和聯合體的兩個重要特征:

結構體和聯合體可以簡潔地仿真大量功能。用更少的代碼行仿真更多功能的能力是在原始Verilog中添加結構體和聯合體等功能的原因之一,

當與本節所述的RTL編碼準則一起使用時,聯合體可以表示多路復用功能,允許多個資源(本例中的有符號和無符號加法器、減法器、乘法器和除法器)共享相同的硬件寄存器。圖4-4中的圓圈代表通用算法 操作,梯形符號代表多路復用器:

圖4-4:示例4-7的綜合結果:具有結構體和聯合體端口的ALU

SystemVerilog-結構體(一)

SystemVerilog-結構體(二)

原文標題:SystemVerilog-聯合體(union)

文章出處:【微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

-

存儲

+關注

關注

13文章

4266瀏覽量

85686 -

硬件

+關注

關注

11文章

3260瀏覽量

66131 -

數據輸出

+關注

關注

0文章

14瀏覽量

9198

原文標題:SystemVerilog-聯合體(union)

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

華為亮相2024年5G創新聯合體“融創行動”論壇

蘇州市人工智能語言計算創新聯合體活動圓滿舉辦

澎峰科技受聘為“主權級大模型”創新聯合體學術委員會委員

長沙角逐算力江湖,長沙市新一代智算產業生態聯合體成立

摩爾線程加入商飛智能“工業元宇宙創新聯合體”

智芯公司入選MEMS器件可靠性試驗創新聯合體首批成員單位

芯原科技牽頭的RISC-V創新聯合體獲正式認定授牌

天津車聯網技術創新聯合體,正式成立!

華為聯合24家企事業單位發起“大模型應用產業聯合體”

北京24家企事業單位組建"大模型應用產業聯合體"?

思必馳入選“2023年度江蘇省創新聯合體建設試點”名單

經典 C 語言編程,結構體和聯合體如何共用?

優必選科技參與成立“人形機器人創新發展聯合體”

【喜訊】芯盾時代當選“北京市高級別自動駕駛示范區智能網聯汽車市域產教聯合體”理事單位

關于數字硬件建模SystemVerilog聯合體

關于數字硬件建模SystemVerilog聯合體

評論