前言:

很久之前的自己在調試電路遇到的一個問題,歡迎留言區分享自己調試電路時的小插曲。

功能介紹:

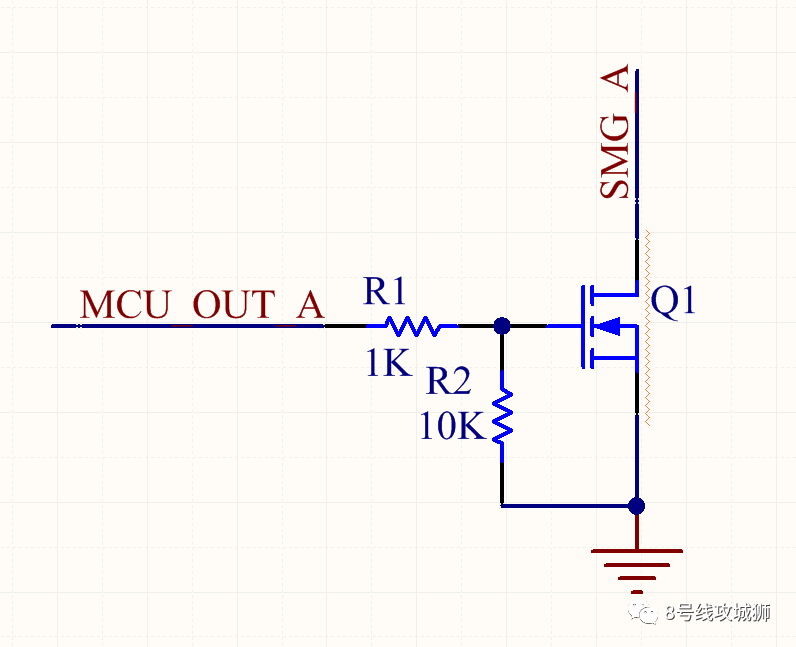

如下電路圖 1 是某開關控制電路,所用關鍵元器件是NMOS,我們知道對于:

NMOS:Ug》Us時導通,(簡單認為)Ug=Us時截止;

PMOS:Ug《Us時導通,(簡單認為)Ug=Us時截止;

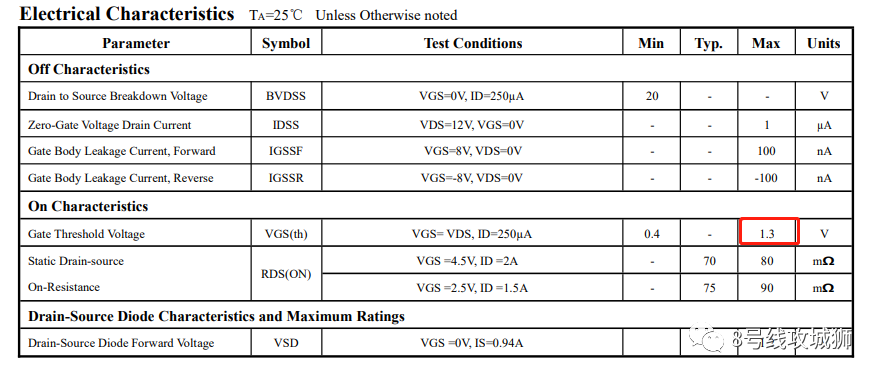

但是Ug比Us大(或小)多少伏時MOS管才會飽和導通呢?

圖 1

問題點:

單片機軟件輸出高電平(5V系統)時,無法控制Q1閉合。

分析解決過程:

按照我們設計的預期:對于NMOS來講,當單片機輸出高電平的時候,

柵源之間電壓:

Ugs=5*10/11≈4.5V,

查看Q1數據手冊如下圖 2,MOS管正常的開啟電壓在1.3V就導通了,在4.5V時候導通電阻Rds就只有75mΩ(Typ)了。

圖 2

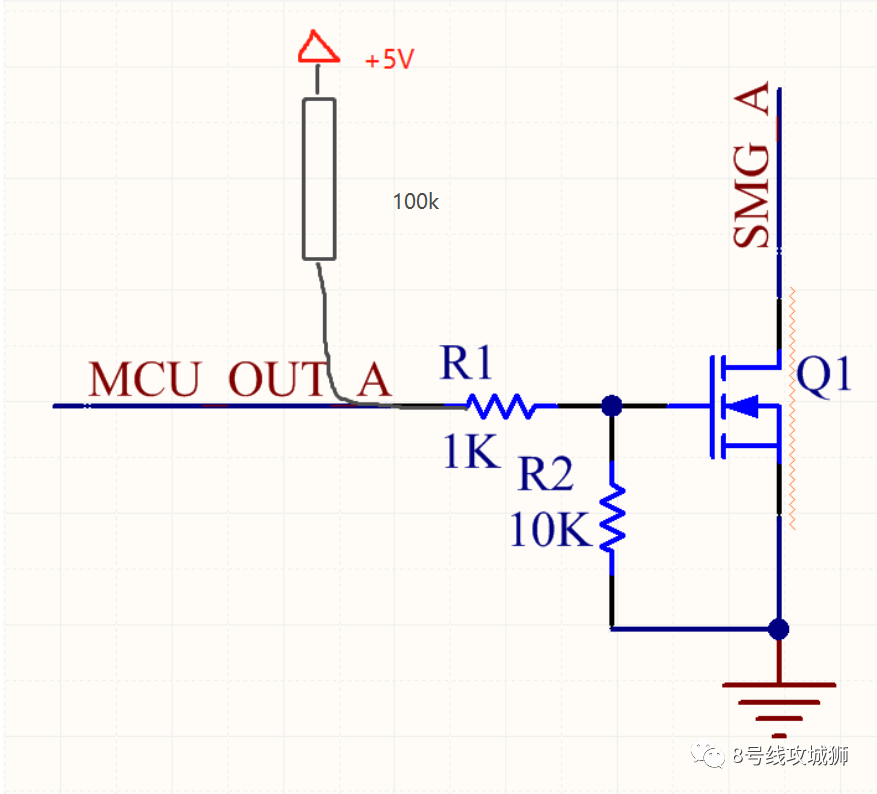

按道理應該可靠閉合的才對。實測測量Q1柵源之間的電壓發現實際電壓只有0.38V左右,還不到最小開啟電壓。這個值顯然是單片機輸出被電阻分壓了,后來和軟件同事一起討論時問了單片機輸出口是怎樣設置的,帶著疑惑去程序中查看,發現控制Q1的IO口被設置成了弱上拉模式,此款芯片的弱上拉相當于是通過100K電阻接到+5V電源上,如下示意圖 3:

圖 3

經分壓計算出Ugs=10/(100+1+10)≈0.45V,跟理論0.39V基本吻合,查到問題關鍵之后將此IO口改為推挽輸出電路就能實現正常功能了。

原文標題:單片機IO口設置錯誤引起的“電路故障”

文章出處:【微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

-

元器件

+關注

關注

112文章

4692瀏覽量

92017 -

NMOS

+關注

關注

3文章

290瀏覽量

34296 -

控制電路

+關注

關注

82文章

1704瀏覽量

135793 -

調試電路

+關注

關注

0文章

3瀏覽量

2136

原文標題:單片機IO口設置錯誤引起的“電路故障”

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

555電路調試技巧和注意事項

做一個差分和偽差分輸出轉換的電路遇到的疑問求解

上海 10月25日-26日《硬件電路設計、調試與工程案例分析》公開課即將開始!

調試電路遇到的問題

調試電路遇到的問題

評論