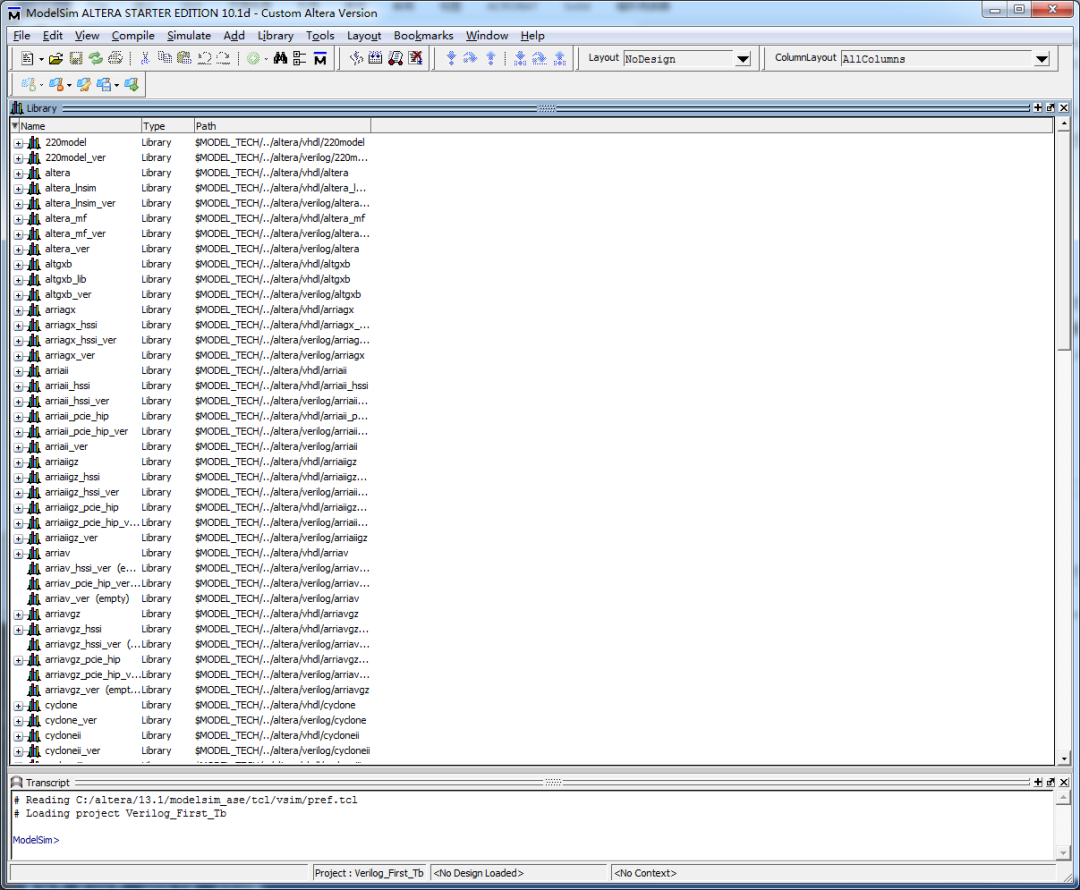

4.1 新建仿真工程在開始動手仿真之前,首先,我們需要創建一個文件夾用來放置我們的 ModelSim 仿真工程文件,這里我們就在之前創建的 Quartus 工程目錄下的 simulation 文件夾中創建一個manual_modelsim 文件夾。manual_modelsim 文件夾創建好以后,我們還需要將已經編寫好的Verilog 仿真文件和 Testbench 仿真文件添加至我們的 manual_modelsim 文件夾中,這里我們就將自動仿真時用到的 Verilog_First.v 文件和 Verilog_First.vt 文件復制到 manual_modelsim文件夾。(Verilog_First.v 文件在我們的 Quartus II 工程目錄下,Verilog_First.vt 文件在我們的Quartus II 工程目錄下 simulation 文件夾下的 modelsim 文件夾中。)完成以上準備工作之后,我們就可以打開 ModelSim-Altera 10.1d (Quartus II 13.1)軟件了,這里我們需要注意的是,我們打開的 ModelSim 軟件版本是 ModelSim-Altera Starter Edition 免費版本,如圖

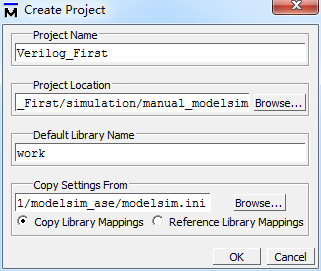

打開軟件之后,我們在 ModelSim 軟件界面的菜單欄中找到【File】→【New】→【Project】菜單并點擊打開,彈出的對話框如圖

我們從對話框中可以看到,Project Name(工程名)就是用來設置我們的工程名,這里我們將它命名為 Verilog_First,這里的命名方式,我們建議大家最好根據我們仿真的文件來進行命名,時間久了,當我們記不得這個仿真工程是用來仿真什么的時候,我們看到這個工程名,就能夠知道它是用來做什么的了。Project Location(工程路徑),可以設置工程保存的文件夾,使用者可以根據需要把工程保存到不同的位置。這 里 我 們 將 路 徑 設 置 在 了E:/A4_Plus_Verilog/Verilog_First/simulation/manual_modelsim 文件夾中。下面這兩部分是用來設置仿真庫名稱和路徑的,這里我們使用默認即可。設置好工程名、工程位置,我們點擊【OK】按鈕,彈出如圖

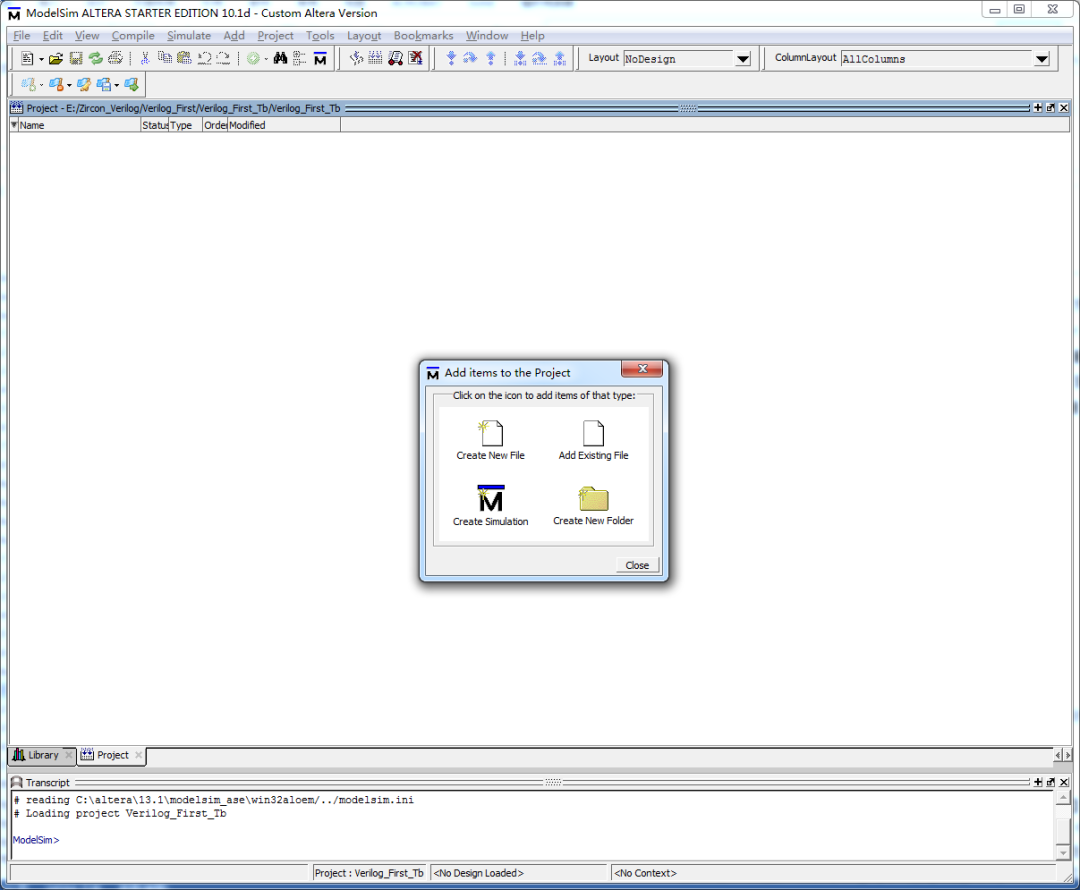

我們可以從該圖中的選擇窗口中看出,它共有四種操作:Create New File(創建新文件)、Add Existing File(添加已有文件)、Create Simulation(創建仿真)和 Create New Folder(創建新文件夾)。這里我們選擇 Add Existing File(添加已有文件),如圖

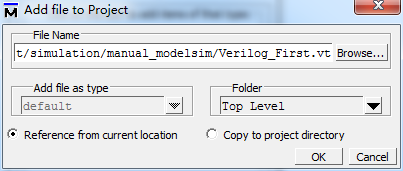

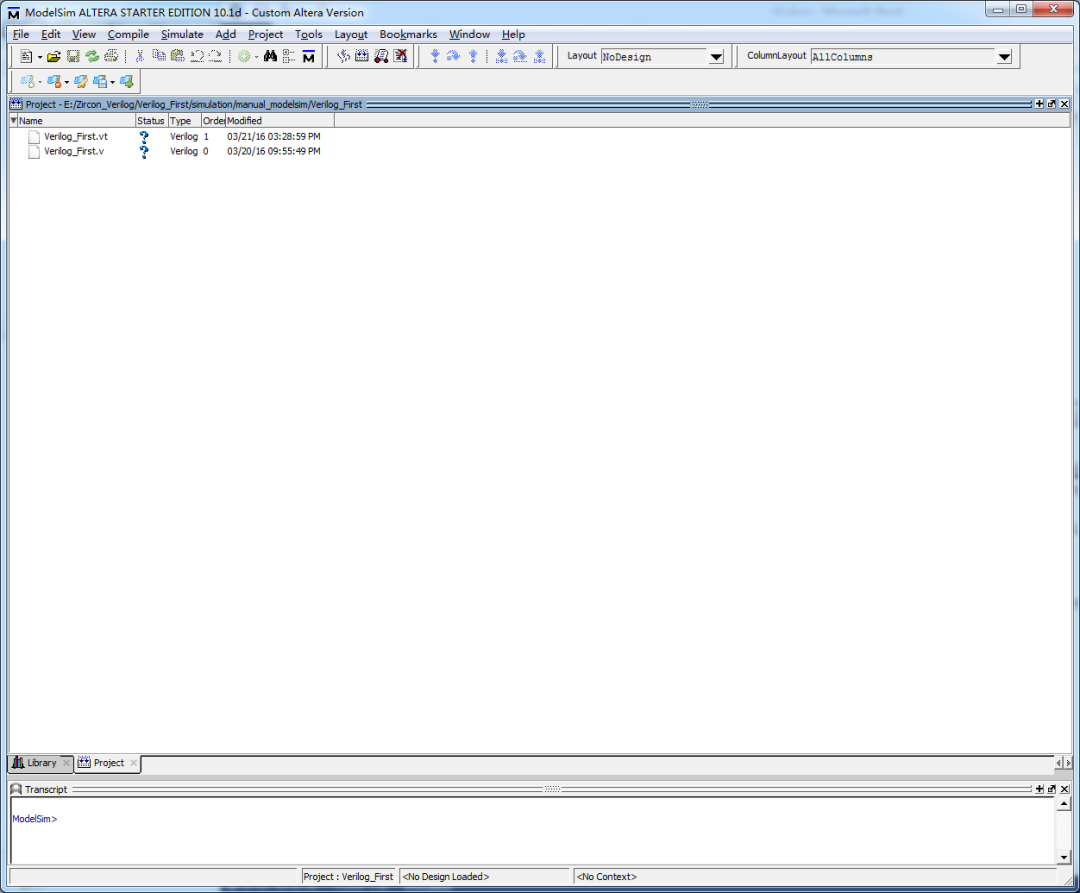

在 該 頁 面 中 我 們 可 以 看 到 , 我 們 將 我 們 之 前 準 備 的 好 兩 個 文 件 Verilog_First.v 和Verilog_First.vt 添加至我們的 ModelSim 仿真工程中。添加好以后,我們點擊【OK】按鈕,然后我們再關閉【Add items to the Project】對話框,如圖

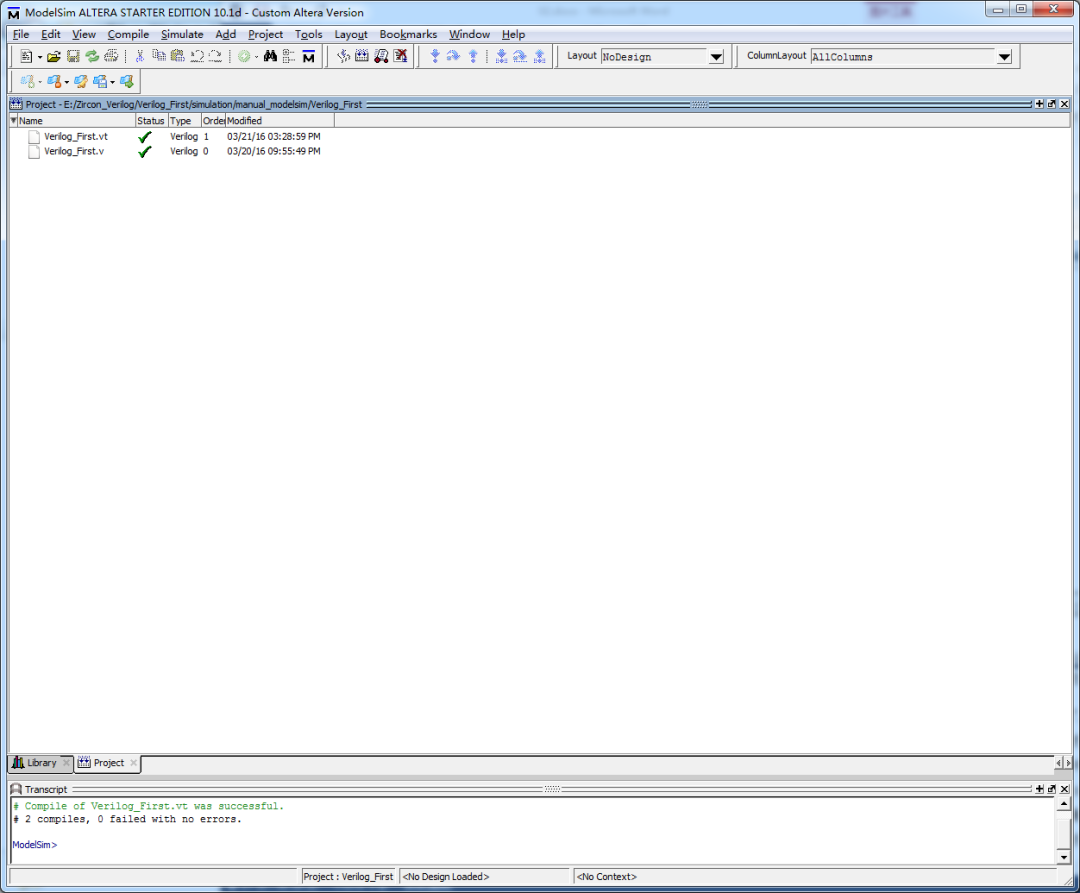

4.2 編譯仿真文件添加完文件以后,接下來我們就需要編譯我們的仿真文件。編譯的方有兩種:Compile Selected(編譯所選)和 Compile All(編譯全部)。編譯所選功能需要先選中一個或幾個文件,執行該命令可以完成對選中文件的編譯;編譯全部功能不需要選中文件,該命令是按編譯順序對工程中的所有文件進行編譯。我們可以在菜單欄【Compile】中找到這兩個命令,也可以在快捷工具欄或者在工作區中的右鍵彈出的菜單中找到這兩個命令。下面我們單擊 Compile All(編譯全部),將會出現如圖

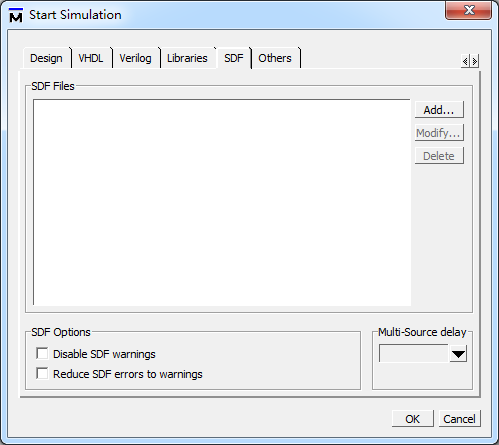

文件編譯后 Status 列可能會有三個不同狀態。除了上述的用“√”顯示的通過狀態,還有兩個在設計中不希望出現的狀態:編譯錯誤和包含警告的編譯通過。編譯錯誤即 Modelsim 無法完成文件的編譯工作。通常這種情況是因為被編譯文件中包含明顯的語法錯誤,這是 Modelsim會識別出這些語法錯誤并提示使用者,使用者可根據 Modelsim 的提示信息進行修改。編譯錯誤時會在 Status 列中顯示紅色的“×”。包含警告的編譯通過是一種比較特殊的狀態,表示被編譯的文件沒有明顯的語法錯誤,但是可能包含一些影響最終輸出結果的因素。這種狀態在實際使用中也較少會出現,該狀態在 Status 欄中也會顯示“√”,但是在對號的后面會出現一個黃色的三角符號,這類信息一般在功能仿真的時候不會帶來明顯的影響,不過可能會在后續的綜合和時序仿真中造成無法估計的錯誤,所以出現這種狀態時推薦讀者也要根據警告信息修改代碼,確保后續使用的安全性。4.3 配置仿真環境我們編譯完成后,接下來我們就開始配置仿真環境,我們在 ModelSim 菜單欄中找到【Simulate】→【Start Simulation.。。】菜單并點擊,彈出如圖

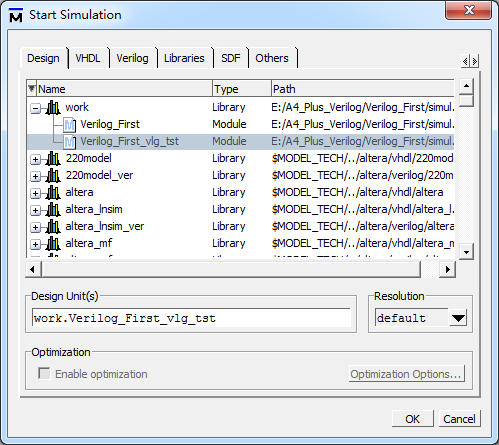

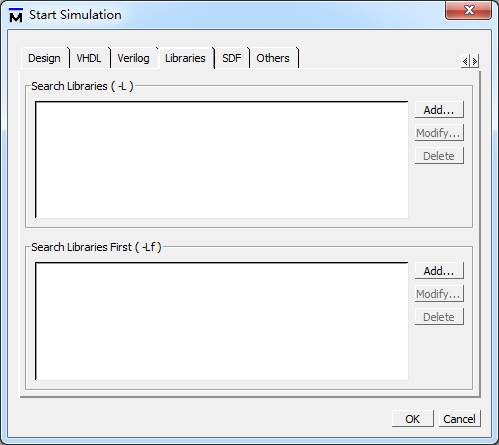

從配置仿真功能頁面中我們可以看出,該頁面中含有 6 個標簽,它們分別是:Design、VHDL、Verilog、Libraries、SDF 和 Others。對于這 6 個標簽,我們用的最多的就屬 Design、Libraries和 SDF,這三個標簽了,下面我們就來簡單的介紹一下這 3 個標簽,其余的標簽我們一般用不到,這里我們就不再進行介紹了。首先介紹 Design 標簽,該標簽內居中的部分是 Modelsim 中包含的全部庫,可展開看到庫中包含的設計單元,這些庫和單元是為了仿真提供選擇的,使用者可以選擇需要進行仿真的設計單元開始仿真,被選中的仿真單元的名字就會出現在下方的 Design Unit(s)位置。Modelsim支持同時對多個文件進行仿真,可以利用 Ctrl 和 Shift 鍵來選擇多個文件,被選中的全部文件名都會出現在 Design Unit(s)區域。在 Design Unit(s)區域的右側是 Resolution 選項,這里可以選擇仿真的時間刻度。時間刻度的概念類似于長度度量單位的米,在 Modelsim 進行仿真的時候,有一個最小的時間單位,這個單位是使用者可以指定的。如最小單位是 10ns,在仿真器工作的時候都是按 10ns 為單位進行仿真,對 10ns 單位一下發生的信號變化不予考慮或不予顯示,當測試文檔有類似于#1 a=1‘b1;的句子時,Modelsim 就不會考慮句中延遲。這個選項一般都是設置在默認的狀態,這時會根據仿真器中指定的最小時間刻度來進行仿真,如果設計文件中沒有指定,則按 1ns 來進行仿真。最下方的區域是 Optimization 區域,可以再仿真開始的時候激活優化,由于我們是免費版本,很多功能都受限制,所以我們可以看到這里我們不能使用。第二個介紹的標簽是 Libraries 標簽,如圖

在該頁面中,我們可以設置搜索庫,可以指定一個庫來搜索實例化的 VHDL 設計單元。Search Libraries 和 Search Libraries First 的功能基本一致,唯一不同的是 Search Libraries First 中指定的庫會被指定在用戶庫之前被搜索。第三個介紹的標簽是 SDF,其內容如圖

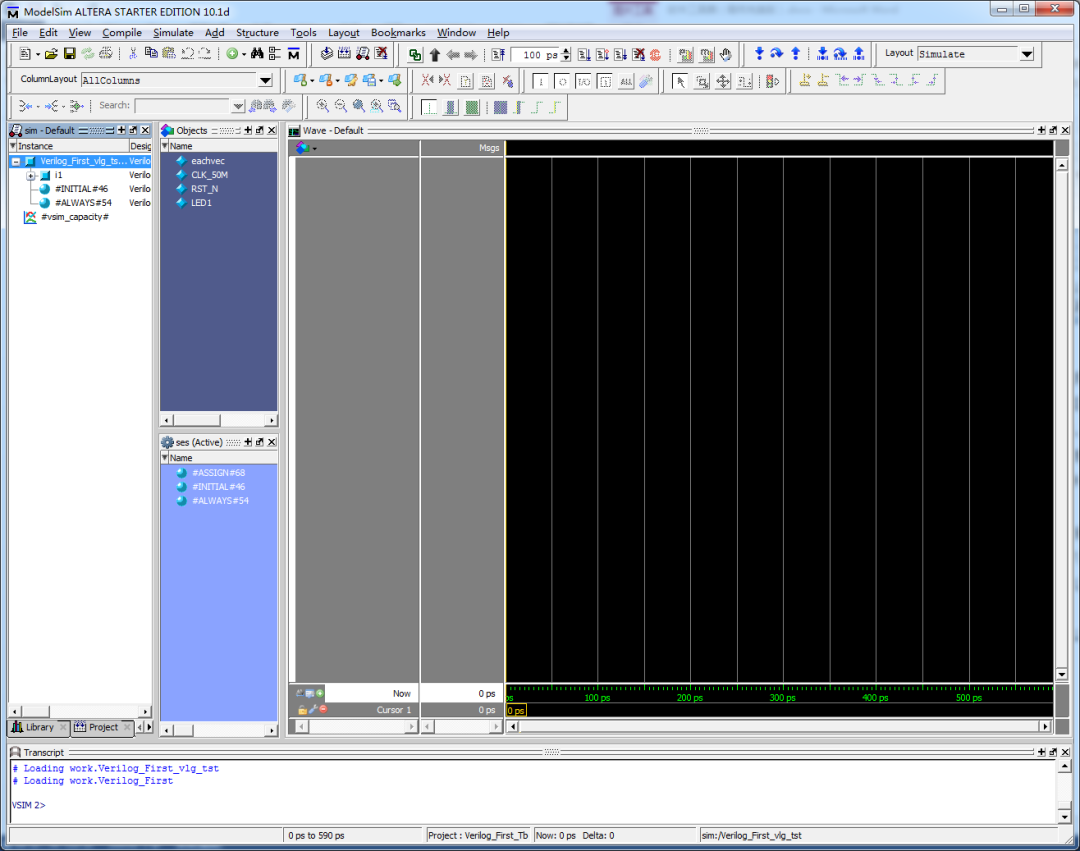

SDF 是 Standard Delay Format(標準延遲格式)的縮寫,內部包含了各種延遲信息,也是用于時序仿真的重要文件。SDF Files 區域用來添加 SDF 文件,選擇 Add 進行添加,選擇 Modify進行修改,選擇 Delete 刪除添加的文件。SDF Options 設置 SDF 文件的 warning 和 error 信息。第一個 Disable SDF warning 是禁用 SDF 警告,第二個 Reduce SDF errors to warnings 是把所有的 SDF 錯誤信息編程警告信息。Multi-Source delay 可以控制多個目標對同一端口的驅動,如果有多個控制信號同時控制同一個端口或互連,且每個信號的延遲值不同,可以在此選項統一延遲。下拉菜單中可供選擇的有三個選項:latest、min 和 max。max 即選擇所有信號中延遲最大的值作為統一值,min 即選擇所有信號中延遲最小的值作為統一值,latest 則是選擇最后的延遲作為統一值。至此,這三個標簽我們就介紹完了,接下來我們在 Design 標簽頁面中選擇 work 庫中的Verilog_First_vlg_tst 模塊,然后點擊【OK】就可以開始進行功能仿真了,其余標簽頁面中的配置我們使用默認就可以了。4.4 開始功能仿真在仿真前,Workspace 區域一般只有 Project 和 Library 兩個標簽。開始仿真后,在Workspace 區域一般會增加 sim 標簽、Files 標簽和 Memory List 標簽。除了 Workspace 區域會增加標簽,在 MDI 窗口也會新出現一個 Object 窗口等,在 Workspace 區域中的 sim 標簽選中一個設計單元,在 Object 窗口就會出現該單元包含的輸入/輸出端口,如圖

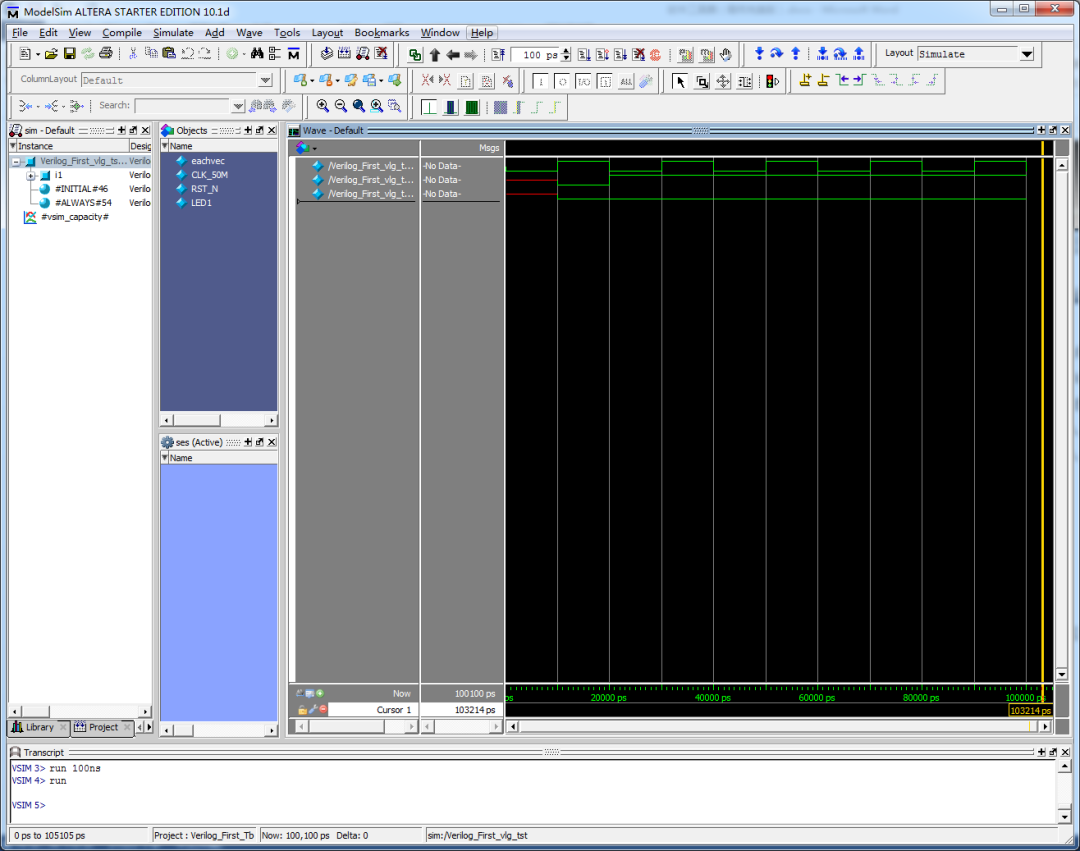

接下來我們在 Object 窗口中選中我們需要仿真的信號,然后點擊右鍵,在彈出的菜單欄中找到【Add Wave】并單擊,我們會發現,我們的信號添加到了 Wave 窗口中。這時,我們可以按快捷鍵 F9,也可以在 ModelSim 的菜單欄中找到【Run】按鈕,點擊運行就會出現我們想要的波形,這里我們需要注意的是,默認的運行時間一次運行的是 100ps,我們可以在菜單欄中進行修改,也可以直接在控制臺中輸入命令 run 100ns,直接運行 100ns,如圖

到了這里,我們就完成了手動的功能仿真,后面的工作就是分析我們仿真出的波形,由于這部分內容和我們在自動仿真中所講的內容完全是一樣的,所以我們這里就不再進一步重復講解了。

原文標題:ModelSim 使用【四】ModelSim手動仿真

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

仿真

+關注

關注

50文章

4044瀏覽量

133420 -

軟件

+關注

關注

69文章

4781瀏覽量

87163 -

編譯

+關注

關注

0文章

654瀏覽量

32809

原文標題:ModelSim 使用【四】ModelSim手動仿真

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【產品介紹】Simcenter Amesim系統仿真軟件

Simcenter Flomaster熱流體仿真軟件

仿真器的使用方法有哪些

電路仿真和PCB設計軟件

新建仿真工程如何開始仿真

新建仿真工程如何開始仿真

評論