隨著 3D-IC 的制造工藝的不斷發(fā)展,3D-IC 的堆疊方式愈發(fā)靈活,從需要基板作為兩個(gè)芯片互聯(lián)的橋梁,發(fā)展到如今可以做到多顆芯片靈活堆疊,芯片設(shè)計(jì)團(tuán)隊(duì)要實(shí)現(xiàn)質(zhì)量最佳、滿足工期要求、具有成本效益的設(shè)計(jì),面臨著如何建立正確的 3D-IC 設(shè)計(jì)實(shí)現(xiàn)流程和如何實(shí)現(xiàn)設(shè)計(jì)數(shù)據(jù)&項(xiàng)目的高效管理的挑戰(zhàn)。

解決這個(gè)挑戰(zhàn),就要求設(shè)計(jì)環(huán)境可以預(yù)先掌握設(shè)計(jì)意圖、支持設(shè)計(jì)模型簡(jiǎn)化,進(jìn)而達(dá)成系統(tǒng)的整體規(guī)劃,獲得系統(tǒng)級(jí)效應(yīng)(如熱和功耗)所提供的早期反饋,并透過實(shí)現(xiàn)和分析的無縫迭代達(dá)到同時(shí)兼顧芯片和封裝效應(yīng)的最佳系統(tǒng)設(shè)計(jì)效果。

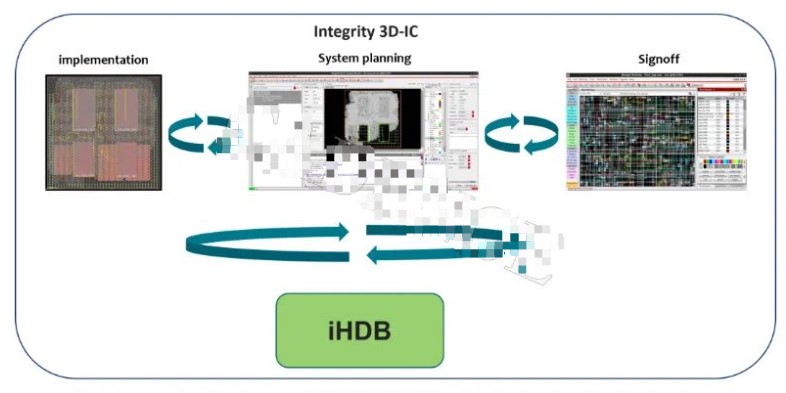

Integrity 3D-IC 平臺(tái)具有強(qiáng)大的數(shù)據(jù)管理功能,能夠?qū)崿F(xiàn)跨團(tuán)隊(duì)的一鍵數(shù)據(jù)同步與更新。同時(shí),Integrity 3D-IC 支持靈活的 3D-IC 實(shí)現(xiàn)流程,配合其高效的數(shù)據(jù)管理機(jī)制,可以讓用戶在流程中的多個(gè)關(guān)鍵階段接入內(nèi)嵌的分析平臺(tái),進(jìn)而實(shí)現(xiàn)整個(gè)系統(tǒng)的快速迭代和 ECO。

通過系統(tǒng)規(guī)劃器為 3D 系統(tǒng)提供獨(dú)特的層次化設(shè)計(jì)和優(yōu)化功能

通過與 Innovus Implementation System 基于 Tcl 的實(shí)時(shí)直接集成,提供完整的堆疊管理、芯片到封裝的信號(hào)映射以及先進(jìn)的 Bump 和 TSV 規(guī)劃功能

高效的數(shù)據(jù)庫,可對(duì)每一層堆疊結(jié)構(gòu)進(jìn)行層次化的多級(jí)表示

Integrity 3D-IC 自底向上的實(shí)現(xiàn)流程

頂層規(guī)劃

物理與邏輯連接的設(shè)計(jì)和優(yōu)化

物理實(shí)現(xiàn)的自動(dòng)化流程

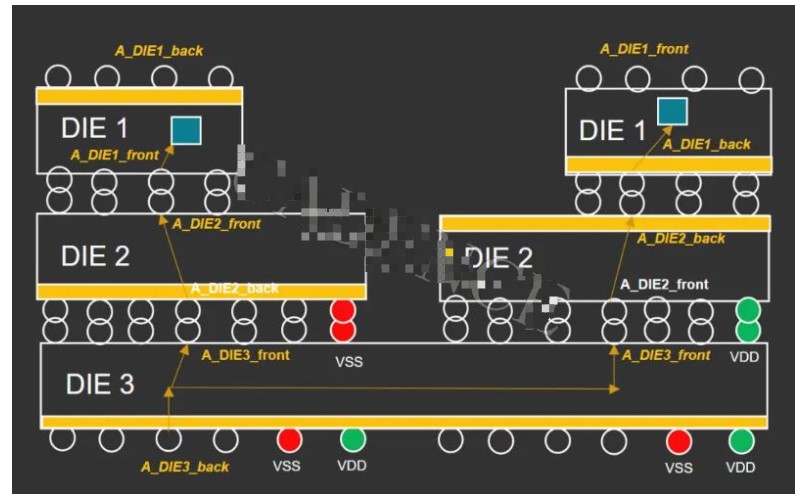

與傳統(tǒng)的芯片層次化設(shè)計(jì)一樣,3D-IC 的實(shí)現(xiàn)流程也有自底向上與自頂向下之分,但無論哪種方法,其目標(biāo)都是將設(shè)計(jì)劃分成若干個(gè)芯片的數(shù)據(jù)包分別做物理實(shí)現(xiàn)。Integrity 3D-IC 可以輕松將兩個(gè)芯片的數(shù)據(jù)包組合,并且在此基礎(chǔ)上完成 3D 系統(tǒng)的布局規(guī)劃和片間互聯(lián)優(yōu)化。與此同時(shí),Integrity 3D-IC 平臺(tái)擁有多種針對(duì) Bump 規(guī)劃以及優(yōu)化的新特性,幫助用戶達(dá)成更高性能的設(shè)計(jì)。

頂層規(guī)劃

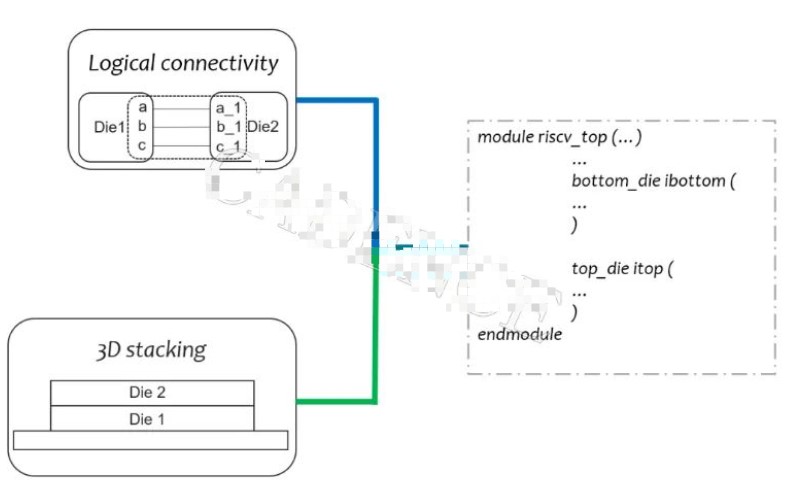

當(dāng)用戶已經(jīng)有芯片的數(shù)據(jù)包,無論該數(shù)據(jù)包處于原型階段還是已部分物理實(shí)現(xiàn),Integrity 3D-IC 均可以利用其建立 3D-IC 系統(tǒng)頂層的堆疊與連接。并且 Integrity 3D-IC 可以支持靈活的頂層邏輯描述格式:用戶可以使用常規(guī)的 verilog 網(wǎng)表或 Integrity 3D-IC 標(biāo)準(zhǔn)的連接描述文件格式,從而可以幫助用戶快速將前端頂層系統(tǒng)設(shè)計(jì)轉(zhuǎn)化為真實(shí)的頂層邏輯連接。

物理與邏輯連接的設(shè)計(jì)和優(yōu)化

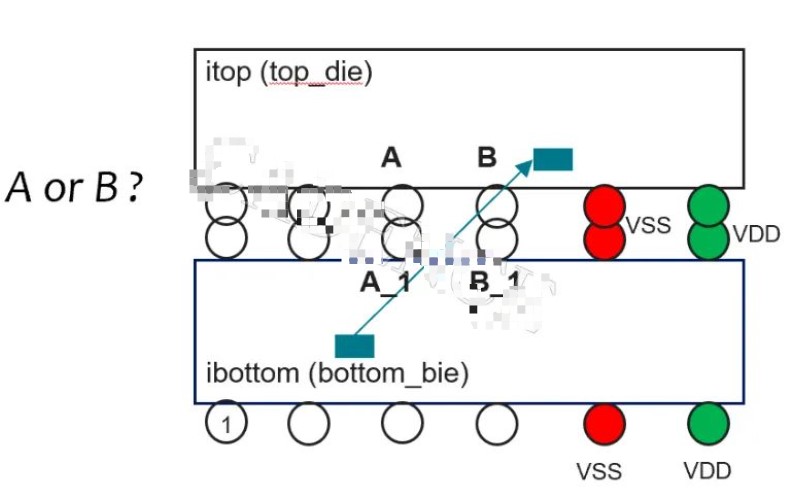

完成頂層設(shè)計(jì)后,我們需要對(duì)片間互聯(lián)的 Bump 模式進(jìn)行設(shè)計(jì),并將信號(hào)與 Bump 關(guān)聯(lián)以實(shí)現(xiàn)邏輯和物理的數(shù)據(jù)通路。通常這個(gè)過程需要跨團(tuán)隊(duì)多次迭代從而實(shí)現(xiàn) Bump 數(shù)量和上下芯片間信號(hào)線長(zhǎng)的平衡,這個(gè)迭代常常為了保留余量而過度設(shè)計(jì),導(dǎo)致?lián)p失部分系統(tǒng)性能,如下圖:

用戶需要多次嘗試以評(píng)估數(shù)據(jù)從 A 通道還是 B 通道傳輸才能得到最短的線長(zhǎng)。當(dāng)設(shè)計(jì)中存在數(shù)萬乃至數(shù)十萬個(gè) Bump 的時(shí)候,這就變成一個(gè)難以完成的任務(wù)。

Integrity 3D-IC 可以根據(jù)設(shè)計(jì)的物理信息自動(dòng)獲得最優(yōu)的信號(hào)與 Bump 關(guān)聯(lián)方案,幫助用戶用最短的時(shí)間得到最佳的 Bump pattern 設(shè)計(jì)。與此同時(shí),對(duì)于一些需要用戶定制的數(shù)據(jù)通路,工具可以根據(jù)用戶提供的映射關(guān)系將所需的信號(hào)與 Bump 準(zhǔn)確的關(guān)聯(lián)。這個(gè)特性可以讓用戶如同堆樂高積木一般實(shí)現(xiàn)多芯片堆疊和信號(hào)通路設(shè)計(jì)。

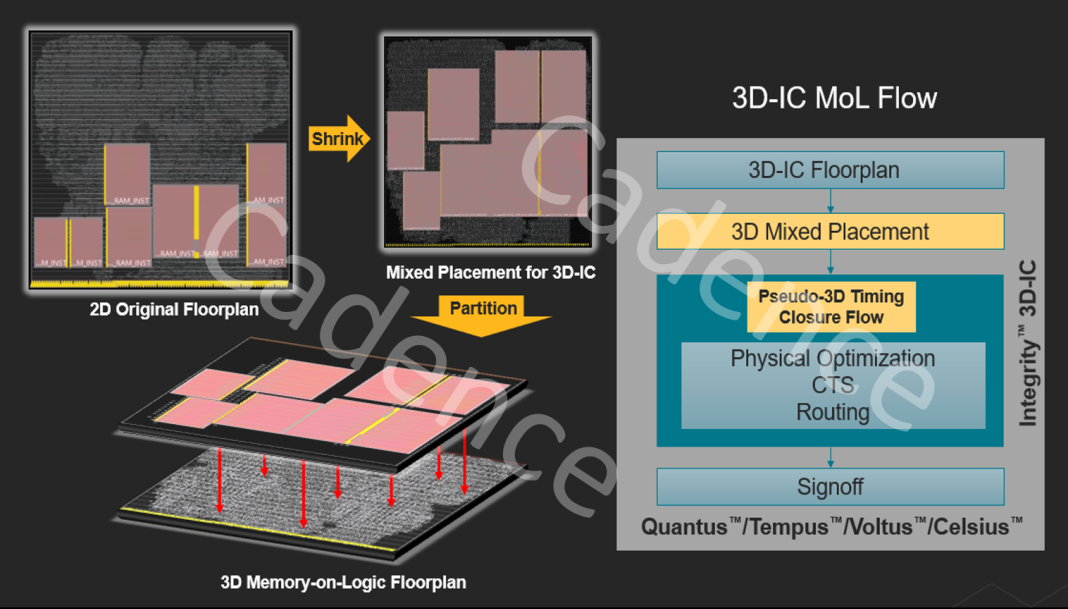

物理實(shí)現(xiàn)的自動(dòng)化流程

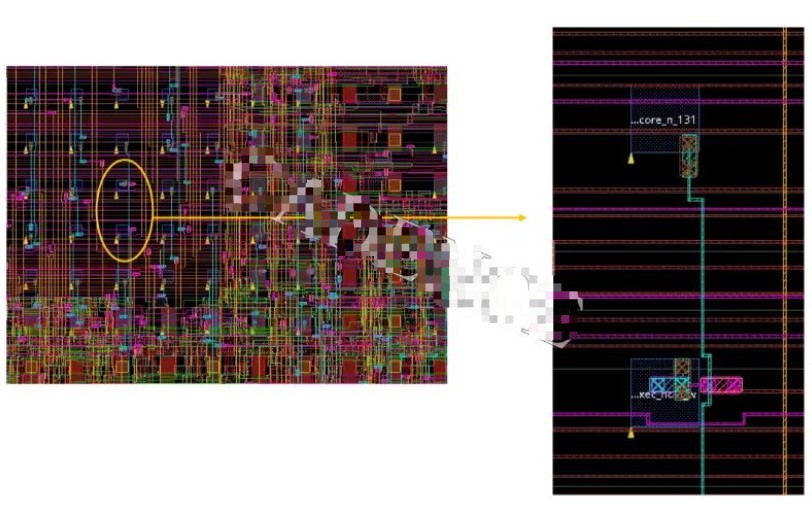

Integrity 3D-IC 支持完整的 3D-IC 物理實(shí)現(xiàn)流程。工具已經(jīng)將 3D-IC 設(shè)計(jì)中所需要的特殊處理整合簡(jiǎn)化,如下圖所示,對(duì)于用戶而言,只需要在 floorplan 階段針對(duì) Bump 做標(biāo)準(zhǔn)流程處理,即可繼續(xù)往下進(jìn)行。而到了繞線的環(huán)節(jié),工具的繞線引擎對(duì)于 Bump 的連接已經(jīng)有著良好的支持,用戶可以通過工具輕松的實(shí)現(xiàn) Bump 繞線自動(dòng)化。如圖所示,工具可識(shí)別出 Bump 的位置并正確的連線打孔。

Integrity 3D-IC 的高效數(shù)據(jù)管理

iHDB (Integrity Hierarchical Database)

數(shù)據(jù)的同步

在 3D-IC 設(shè)計(jì)中,用戶需要管理的不再是一顆芯片的數(shù)據(jù),而是若干個(gè)芯片,跨越架構(gòu)設(shè)計(jì),后端實(shí)現(xiàn),封裝設(shè)計(jì),設(shè)計(jì)簽核的多團(tuán)隊(duì),不同類型的數(shù)據(jù)管理。在項(xiàng)目進(jìn)展過程中如果發(fā)生 ECO,通常需要經(jīng)過層層溝通,耗時(shí)費(fèi)力易出錯(cuò)。Integrity 3D-IC 提供了一套高效的數(shù)據(jù)管理架構(gòu)(iHDB),并且可以通過工具將某一個(gè)步驟發(fā)生的 ECO 正確的傳播到各個(gè)團(tuán)隊(duì)所需要的數(shù)據(jù)包中,從而避免了人為溝通檢查的時(shí)間損耗。

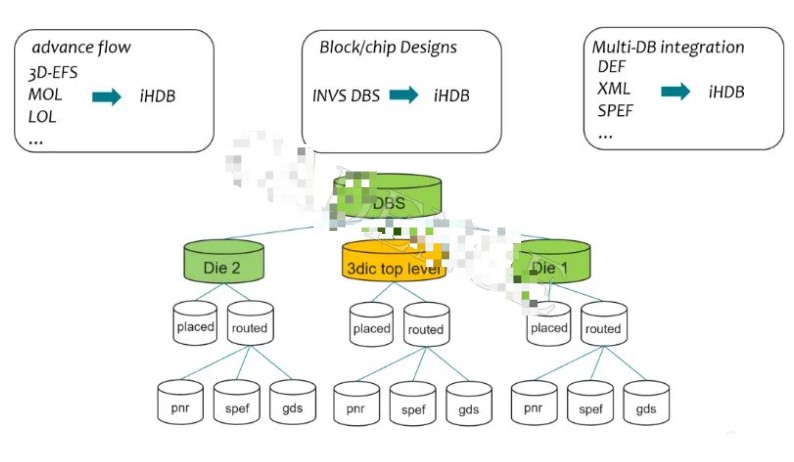

iHDB(Integrity Hierarchical Database)

iHDB 的層次化框架如下圖所示,它可以讓用戶將業(yè)界多種形式的標(biāo)準(zhǔn)數(shù)據(jù)轉(zhuǎn)化成 iHDB 的層次化結(jié)構(gòu)進(jìn)行存儲(chǔ)。并且其提供 Tcl 接口讓用戶可以輕松讀寫芯片不同階段不同類型的數(shù)據(jù)。用戶可以通過這個(gè)框架管理不同項(xiàng)目節(jié)點(diǎn)的存檔,確保不同設(shè)計(jì)者之間交付的數(shù)據(jù)版本一致性,并可以實(shí)現(xiàn)快速的交叉檢查。

數(shù)據(jù)的同步

在 3D-IC 設(shè)計(jì)過程中,用戶可能在任意階段做 ECO 或分析,Integrity 3D-IC 提供極為強(qiáng)大的數(shù)據(jù)同步功能,用戶只需要用一條命令就可以完成數(shù)據(jù)的更新和同步,并可以直接在 Integrity 3D-IC 中啟用分析簽核工具讀取更新過后的數(shù)據(jù)做分析。這可以大大提高不同團(tuán)隊(duì)之間互相交付輸入件的效率,進(jìn)而加快項(xiàng)目收斂。

憑借 Cadence 在模擬和數(shù)字 IC 設(shè)計(jì),封裝設(shè)計(jì)以及 PCB 設(shè)計(jì)領(lǐng)域提供的全方面 EDA 工具產(chǎn)品的集成,Cadence Integrity 3D-IC 通過統(tǒng)一的層次化數(shù)據(jù)庫結(jié)構(gòu),利用 Cadence 業(yè)界領(lǐng)先的數(shù)字 / 模擬 / 封裝以及簽核技術(shù),實(shí)現(xiàn)了讓用戶可以在系統(tǒng)規(guī)劃和實(shí)現(xiàn)流程的早期就進(jìn)行系統(tǒng)分析和設(shè)計(jì)迭代,達(dá)到系統(tǒng) PPA 驅(qū)動(dòng)的高性能 3D-IC 設(shè)計(jì)效果,同時(shí)可以避免高昂的過度設(shè)計(jì)成本。

審核編輯:劉清

-

IC設(shè)計(jì)

+關(guān)注

關(guān)注

37文章

1291瀏覽量

103761 -

TCL

+關(guān)注

關(guān)注

10文章

1715瀏覽量

88460

原文標(biāo)題:3D-IC 設(shè)計(jì)之自底向上實(shí)現(xiàn)流程與高效數(shù)據(jù)管理

文章出處:【微信號(hào):gh_fca7f1c2678a,微信公眾號(hào):Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Cadence分析 3D IC設(shè)計(jì)如何實(shí)現(xiàn)高效的系統(tǒng)級(jí)規(guī)劃

Cadence 憑借突破性的 Integrity 3D-IC 平臺(tái)加速系統(tǒng)創(chuàng)新

TSMC 和 Cadence 合作開發(fā)3D-IC參考流程以實(shí)現(xiàn)真正的3D堆疊

Cadence Integrity 3D-IC平臺(tái)?支持TSMC 3DFabric技術(shù),推進(jìn)多Chiplet設(shè)計(jì)

Cadence Integrity 3D-IC平臺(tái)進(jìn)行工藝認(rèn)證

Integrity?3D-IC平臺(tái)助力設(shè)計(jì)者實(shí)現(xiàn)驅(qū)動(dòng)PPA目標(biāo)

Cadence Integrity 3D-IC自動(dòng)布線解決方案

Cadence Integrity 3D-IC Platform榮膺“年度EDA/IP/軟件產(chǎn)品”

3D-IC未來已來

產(chǎn)品資訊 | 3D-IC 設(shè)計(jì)之自底向上實(shí)現(xiàn)流程與高效數(shù)據(jù)管理

Cadence 擴(kuò)大了與 Samsung Foundry 的合作,依托 Integrity 3D-IC平臺(tái)提供獨(dú)具優(yōu)勢(shì)的參考流程

3D-IC 設(shè)計(jì)之 Memory-on-Logic 堆疊實(shí)現(xiàn)流程

3D-IC 以及傳熱模型的重要性

如何建立正確的3D-IC設(shè)計(jì)實(shí)現(xiàn)流程和實(shí)現(xiàn)項(xiàng)目高效管理的挑戰(zhàn)

如何建立正確的3D-IC設(shè)計(jì)實(shí)現(xiàn)流程和實(shí)現(xiàn)項(xiàng)目高效管理的挑戰(zhàn)

評(píng)論