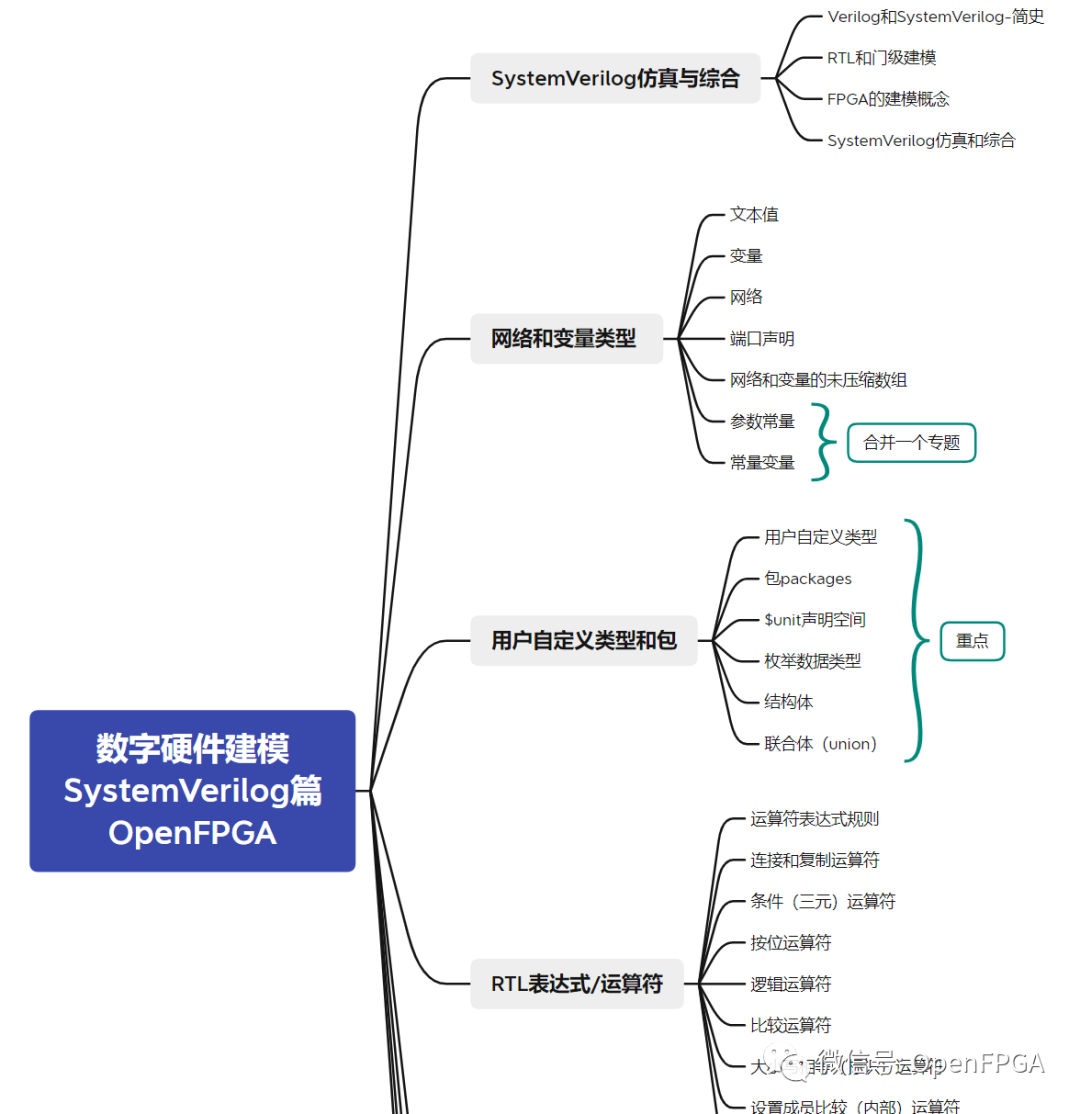

數字硬件建模SystemVerilog-運算符/表達式規則

經過幾周的更新,SV核心部分用戶自定義類型和包內容已更新完畢,接下來就是RTL表達式和運算符。

馬上HDLBits-SystemVerilog版本也開始準備了,基本這一部分完成后就開始更新~

介紹

運算符對操作數執行操作。大多數運算符都有兩個操作數。例如,在運算a+b中,+(加法)運算的操作數是a和b。每個操作數都被稱為表達式,表達式可以是文字值、變量、網絡;函數調用的返回,或另一個操作的結果。表達式有許多影響操作執行方式的特征。這些特征在后面章節中討論。

4-state(4態)和2-state(2態)操作

表達式可以是2態或4態。2態表達式的每個位只能有0或1的值。2態表達式不能具有高阻抗值(由字母Z表示)、未知值(由字母X表示)或不關心值(也由X表示)。4態表達式可以在表達式的任何位中包含0、l、Z或X的值。

對2態和4態表達式進行運算的規則很簡單——當任何操作數都是4態表達式時,運算的結果將是4態表達式。所有操作數都必須是2態表達式才能得到2態結果。如果結果被用作另一個操作的操作數,或在編程語句(如if-else)中求值,則此規則可能會影響其他操作。

該章中建議的編碼準則是,RTL建模只使用4態類型。一個主要原因是,運算結果中任何一位的X都可以很好地表明其中一個操作數有問題。當使用2態類型時,設計問題可能會被隱藏,因為操作結果中沒有X值指示潛在的錯誤(之前的文章有詳細討論這部分)。

大多數SystemVerilog運算符都是X-optimism,這意味著即使操作數中有X或Z值,該操作也可能產生已知結果。一些SystemVerilog運算符,如算術運算符和關系運算符,是X-pessimism,這意味著,如果任何操作數的任何位具有X或Z值,則結果的所有位將自動為X。

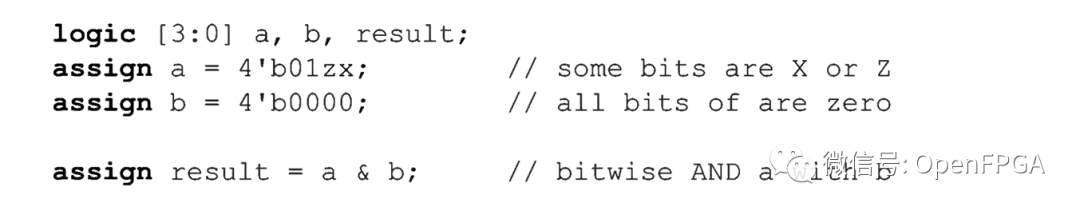

X-OPTIMISM。即使一個或兩個操作數的位具有X或Z值,X-optimism也可以產生有效的結果。考慮下面的示例和所示的邏輯值:

該運算的結果是值4’b0000。這是因為&運算符為其操作數的每一位建模一個數字and邏輯門。在數字邏輯中,0與任何值的AND運算將產生0,操作數a中的高阻抗位(由Z表示)和未知位(由X表示)在result中變為0,因為這些位與b中對應的位進行AND運算,b的值為0。這種行為被稱為X-OPTIMISM。仿真將有一個已知的結果,即使操作數的位具有X或Z值。

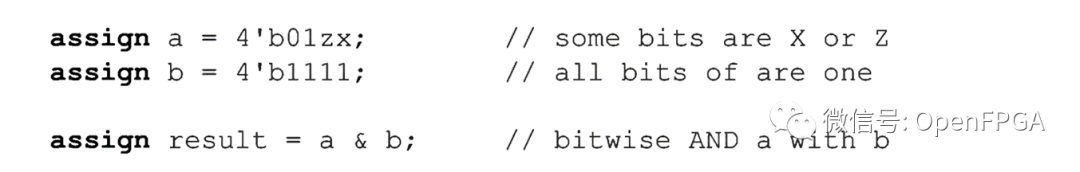

X-OPTIMISM僅適用于仿真可以準確預測實際邏輯門行為的值。在下面的示例中,b操作數是全1而不是全0。

運算的結果是值4’b01xx。對于這些操作數值,X-optimism不適用于最右邊的兩個位。在實際邏輯門中,高阻抗AND (與)X,可能會產生0或1,其值取決于一系列條件,例如用于構建與門的晶體管類型、晶體管電路的阻抗和電容、工作電壓,甚至環境溫度。抽象RTL和運算符沒有此詳細信息。如果沒有這些細節,數字仿真無法預測0或1是否會由1與Z相加產生。類似地,X代表未知值,這意味著實際邏輯門值可能是0、1或Z,如果存在這種模糊性,數字仿真無法預測0或1是否會由1與X相加產生。

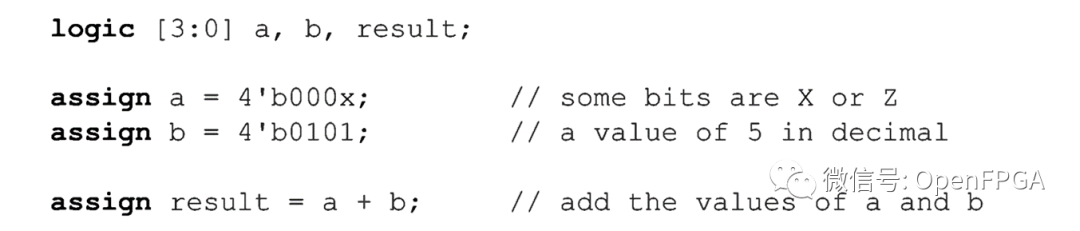

**X-pessimistic。少數SystemVerilog運算符更"悲觀"**。如果任何操作數的任何位具有X或Z值,則該操作會自動返回一個值,其中所有位都為X。X-pessimistic如算術運算符(如加法運算符)和關系運算符(如小于運算符)。

運算的結果是4’bxxxx。出現這種X是因為算術加法運算符執行基于數字的加法,而不是按位加法。操作數a的值為4’b000x,這不是一個數字,因此運算結果是一個未知值。

后面會更詳細地研究SystemVerilog RTL運算符,以及每個運算符是X-optimistic or X-pessimistic。為了編寫能夠正確表示的RTL模型,理解這些影響硬件行為至關重要。

運算向量大小和自動向量擴展

運算符的每個操作數可以是任意大小的向量;包括標量(1位)。操作數的向量大小可能會影響操作的執行方式。一個重要的考慮因素是當運算符的操作數是不同的向量大小時。

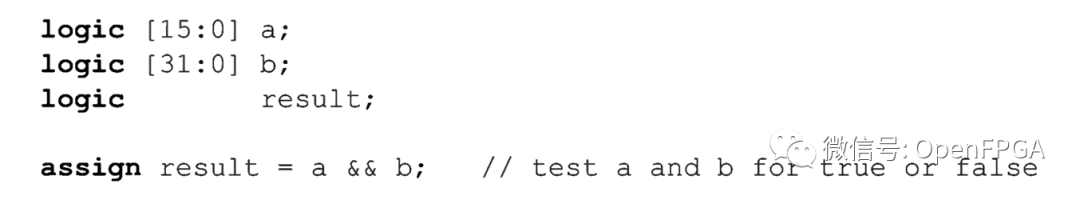

自定義操作數Self-determined operands。有些運算符獨立處理每個操作數。操作數是否為不同的向量大小并不重要。這些運算符的操作數稱為自定數self-determined。在下面的示例中,運算符執行邏輯“&&”運算,測試兩個操作數是否都為真。如果是,則該操作返回的結果為true,否則,該操作返回的結果為false:

操作數a和b是自定數。每個操作數的計算結果可以是真或假,與另一個操作數的向量大小無關。

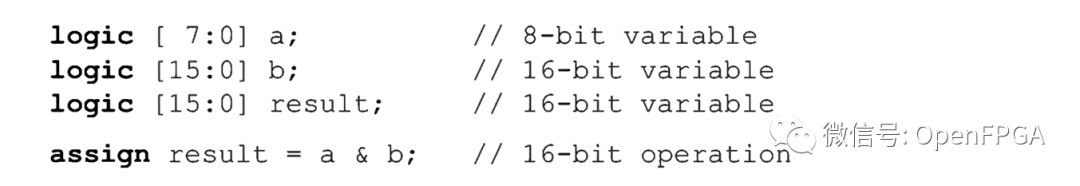

上下文確定的操作數。許多運算符需要將操作數展開為相同的向量大小,然后才能執行操作。這些運算符的操作數被稱為上下文確定的操作數(context-determined)。該操作將使最短的操作數向左擴展,使其與最大的操作數的向量大小相同。在下面的示例中,&運算符執行按位AND運算,將每個操作數的每一位相加,并返回布爾結果。

為了將a的每一位與b的每一位進行AND,該操作將兩個操作數調整為相同的向量寬度。該操作將檢查操作的上下文以確定最大的操作數,然后左擴展較短的操作數以匹配最大操作數的大小。擴展規則如下:

如果最左邊的位為0或l,且操作數為無符號類型,則操作數為零擴展(每個附加位的值為0)。

如果最左邊的位是0或l,并且操作數是有符號類型,則操作數是符號擴展的(每個額外的位被賦予最左邊位的值或原始值。最左邊的位被稱為符號位)。

如果最左邊的位是Z,則操作數是Z擴展的(每個額外的位都有Z的值)。

如果最左邊的位是X,則操作數是X擴展的(每個附加位的值為X)。

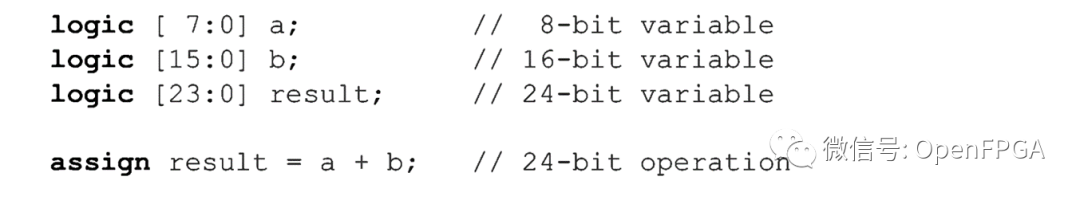

算術運算的上下文推斷大小比其他運算符的上下文推斷大小更復雜,上下文推斷大小不僅考慮運算符的操作數,還考慮賦值語句右側和左側所有表達式的向量大小,如以下代碼所示:

有符號和無符號表達式

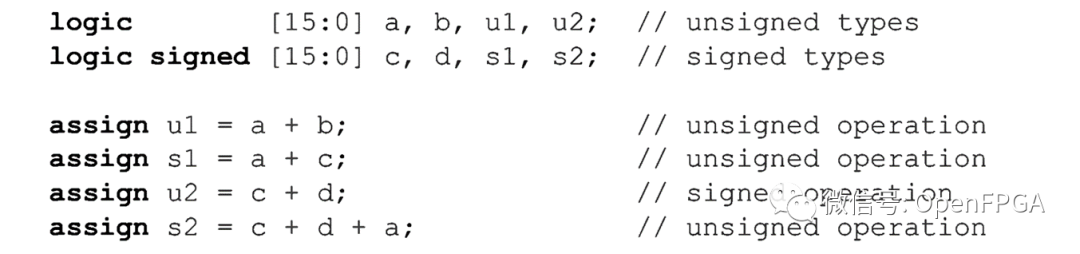

算術、比較和移位運算符可以執行有符號或無符號運算。規則很簡單——如果執行運算的所有操作數都是有符號的,則執行有符號運算。如果任何受影響的操作數是無符號的,則執行無符號操作——以下代碼段說明了這些規則。注釋中注明了操作類型。

運算符的符號性完全由操作運算符的操作數決定。它不受賦值語句左側的符號性影響。

整數(向量)和實數(浮點)表達式

所有SystemVerilog運算符都可以對整數值執行操作。IEEE SystemVerilog標準將整數值稱為整數表達式——由一個或多個連續位組成的值。工程師通常將這些整數或整數值稱為向量。

SystemVerilog將定點和浮點表達式稱為實數表達式。大多數類型的運算都可以在實數表達式上執行,包括:賦值運算、算術運算、邏輯(真/假)運算、比較運算和遞增/遞減運算。有一些操作無法在實數表達式上執行。這些操作主要包括向量的位處理,例如位和部分選擇操作、按位操作、移位操作、連接操作和流操作。

可以對整數和實數表達式的混合執行操作。混合類型運算的規則是,如果任何操作數是實數表達式,則另一個操作數將轉換為實數表達式,并執行浮點運算。

| 筆記 |

|---|

| RTL綜合編譯器通常不支持實數(浮點)表達式。高級綜合(HLS)工具可用于復雜的算法設計。浮點和定點設計不在本系列文章的范圍之內。 |

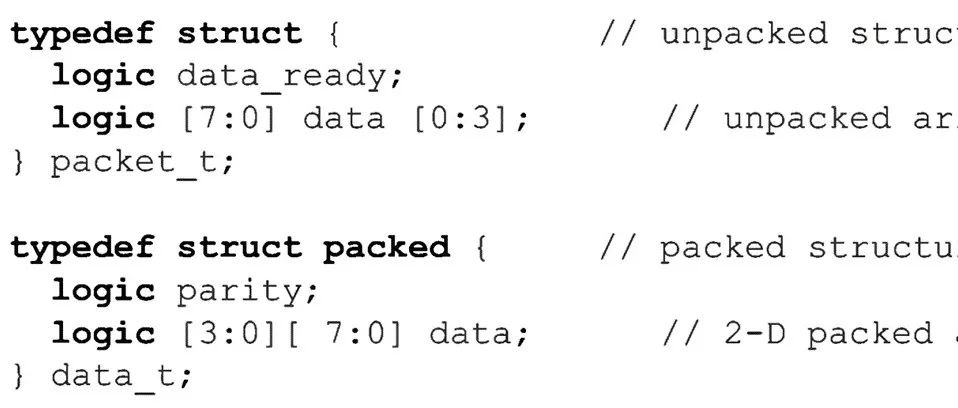

SystemVerilog-使用結構體和聯合體的例子

原文標題:SystemVerilog-運算符/表達式規則

文章出處:【微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

-

硬件

+關注

關注

11文章

3252瀏覽量

66113 -

編碼

+關注

關注

6文章

935瀏覽量

54761 -

RTL

+關注

關注

1文章

385瀏覽量

59701 -

運算符

+關注

關注

0文章

172瀏覽量

11064

原文標題:SystemVerilog-運算符/表達式規則

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于運算符信息的數學表達式檢索技術

RTL表達式和運算符

RTL表達式和運算符

評論