一、啟動流程介紹

普通的 FPGA 一般是可以從 flash 啟動,或者被動加載,但是ZYNQ不行,ZYNQ必須PS端參與

ZYNQ 的啟動是由 ARM 主導的,包括 FPGA 程序的加載, ZYNQ 啟動一般為3個階段,最少2個階段:

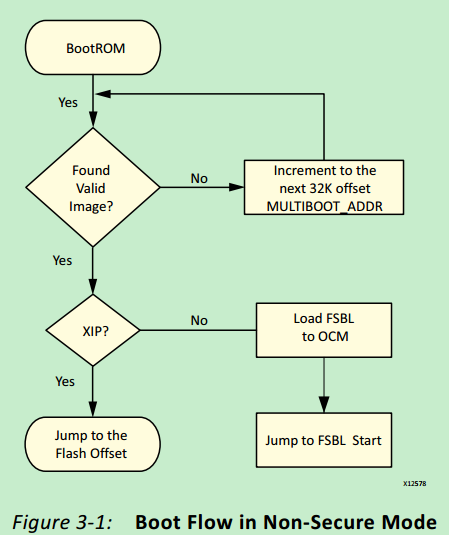

1、階段0:Stage-0 Boot (BootROM)

階段0,主要是運行芯片內部固化的BootROM程序,這個BootROM主要是識別啟動模式(spi/sd/nand/nor/)是哪一種?

1)、根據啟動模式,設置相應的外設,當然有引腳復用了,還有時鐘;

2)、將FSBL從啟動介質中搬移到OCM(On-Chip Memory)中

3)、跳轉到FSBL處執行,將控制權交給FSBL程序

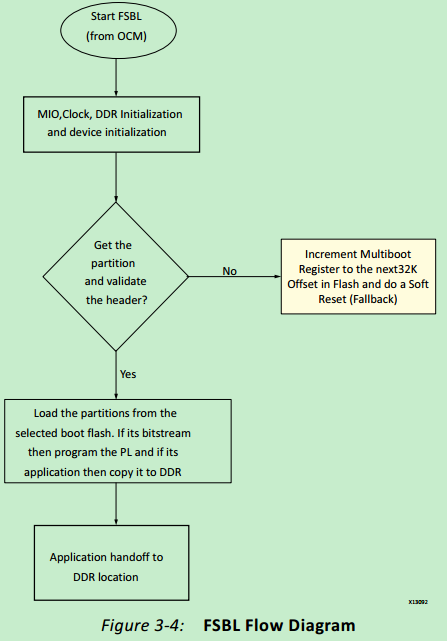

2、階段1:FSBL(First Stage Bootloader )

FSBL(第一階段引導加載程序)在BootROM之后啟動,這個BootROM將FSBL加載到OCM(On-Chip Memory )

FSBL負責下面的幾項工作:

1)、初始化PS端的配置數據(使用Xilinx硬件配置工具提供的);

完成MIO分配、時鐘PLL、DDR控制器初始化,SD、QSPI控制器初始化

2)、通過啟動模式從啟動介質讀取bitsttream文件,并用它燒寫PL端程序

3)、加載第二階段BootLoader或者邏輯代碼到DDR內存

4)、切換到第二階段BootLoader或者邏輯代碼運行

下圖是一個簡單的FSBL流程圖:

3、第二階段啟動流程:Second Stage Bootloader

第二階段引導加載程序是可選的,并由用戶設計,一般是在跑系統的情況下使用,比如 linux 系統的u-boot(用petalinux 工具制作 linux 系統 )

二、制作FSBL第一階段的啟動代碼

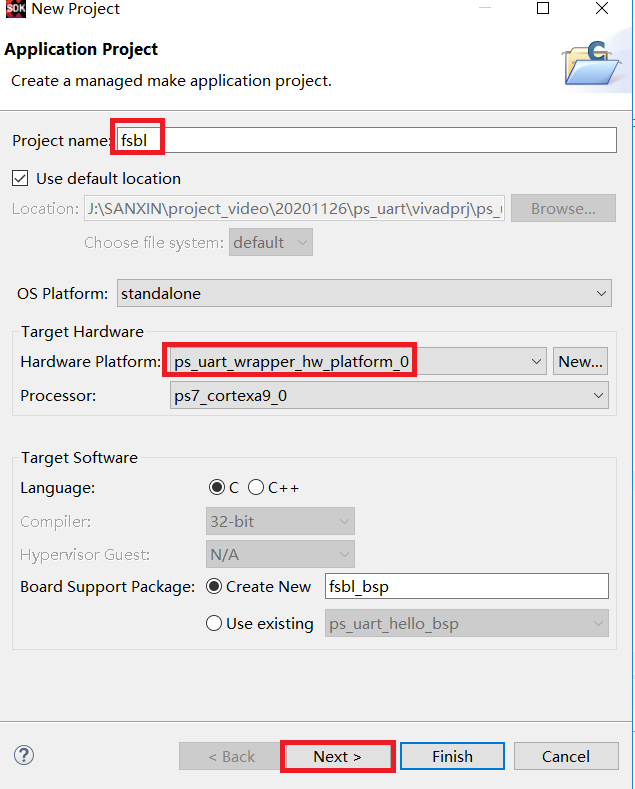

1、新建一個名為 fsbl 的 APP,特別注意硬件平臺選擇我們自己配置的ps_uart_warpper_hw_platform_0 ,點擊next

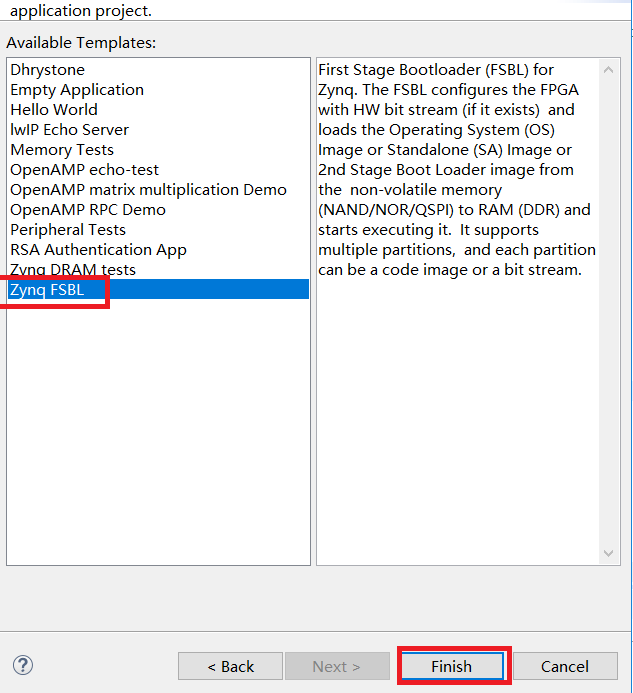

2、在彈出的對話框選擇Zynq FSBL,點擊Finish

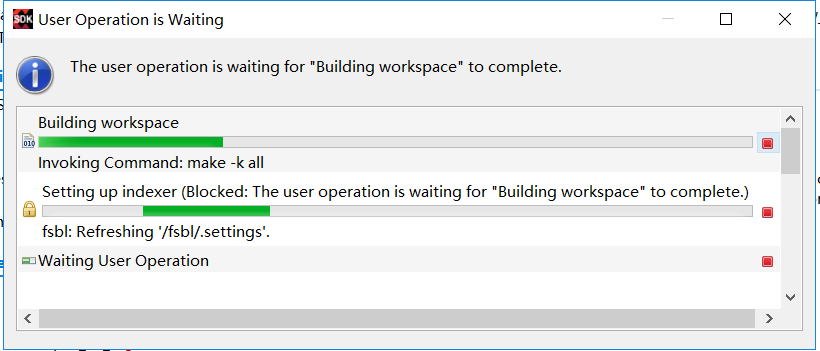

3、然后軟件會自動的進行編譯FSBL,時間看電腦的性能

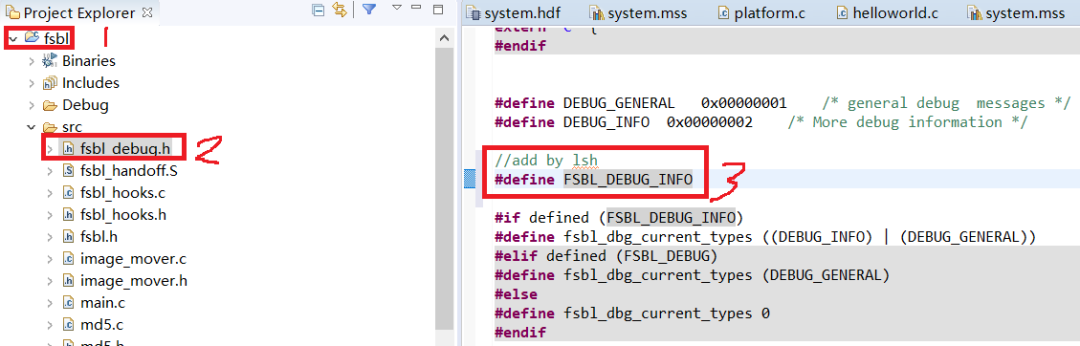

4、等編譯完成,修改代碼,添加調試宏定義 FSBL_DEBUG_INFO

這個宏可以在啟動輸出 FSBL 的一些狀態信息,有利于調試,但是會導致啟動時間變長。

5、修改后保存, SDK 默認會自動編譯,生成 fsbl.elf 文件。也可以右鍵點擊build project手動編譯

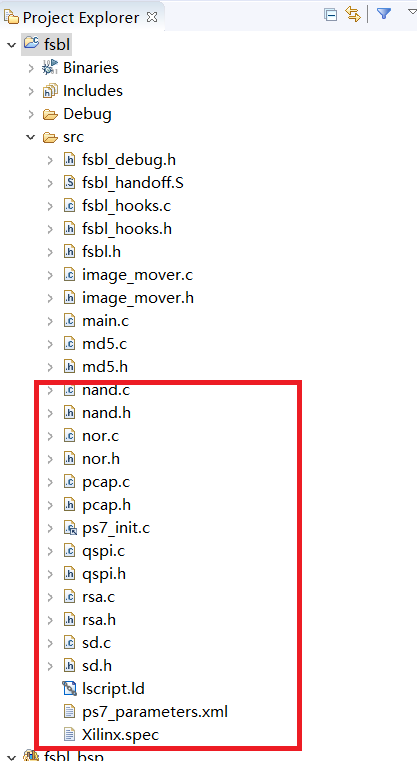

6、我們的工程文件夾包含很多外設文件ps7_init.c, nand, nor, qspi, sd 等

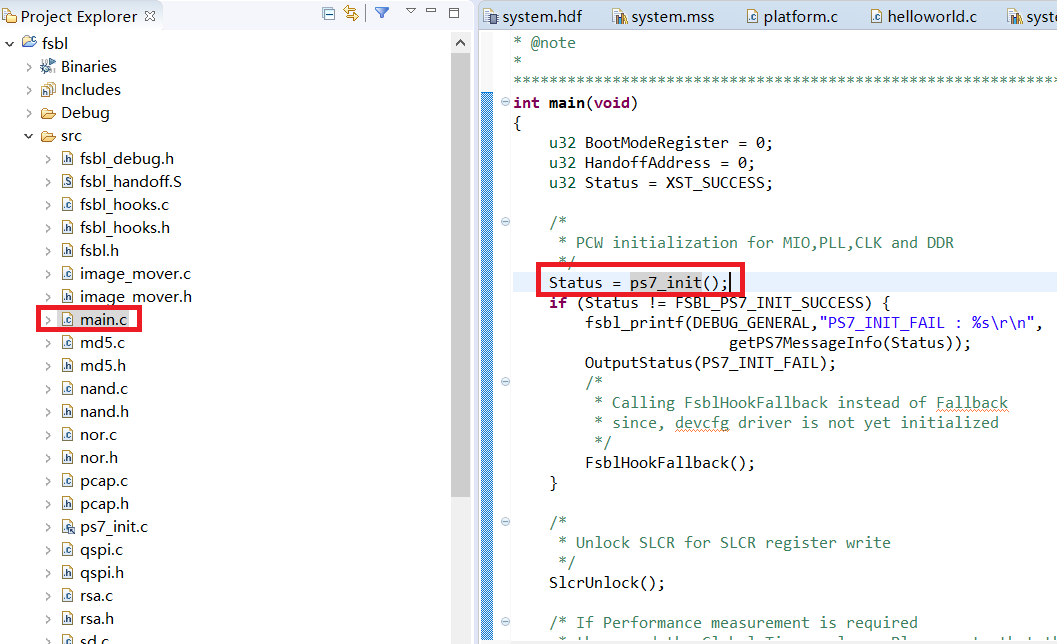

7、fsbl的 main.c 中,第一個運行的函數就是 ps7_init ,這個fsbl內容也可以根據自己需要進行更改,例如加點自己的打印信息

8、創建 BOOT 文件

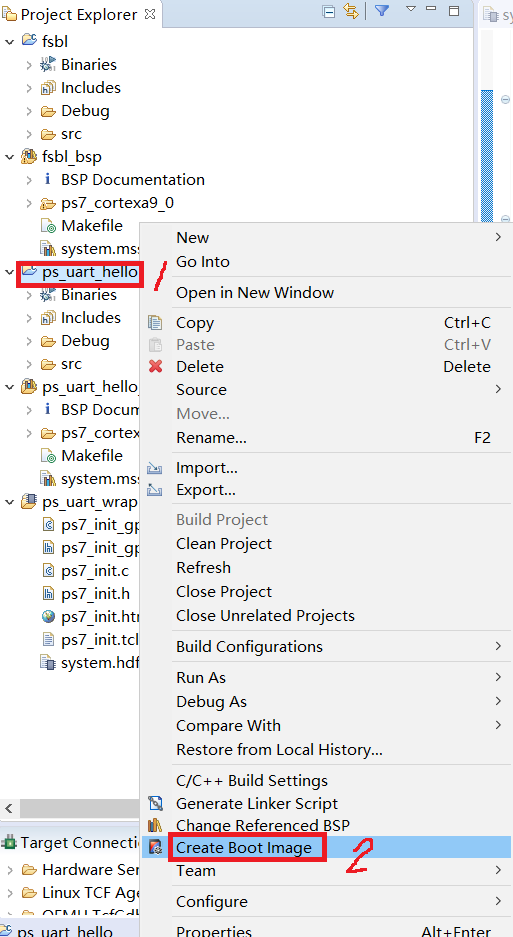

8.1、選擇 APP (就是我們的應用:ps_uart_hello)工程,右鍵選擇 Create Boot Image

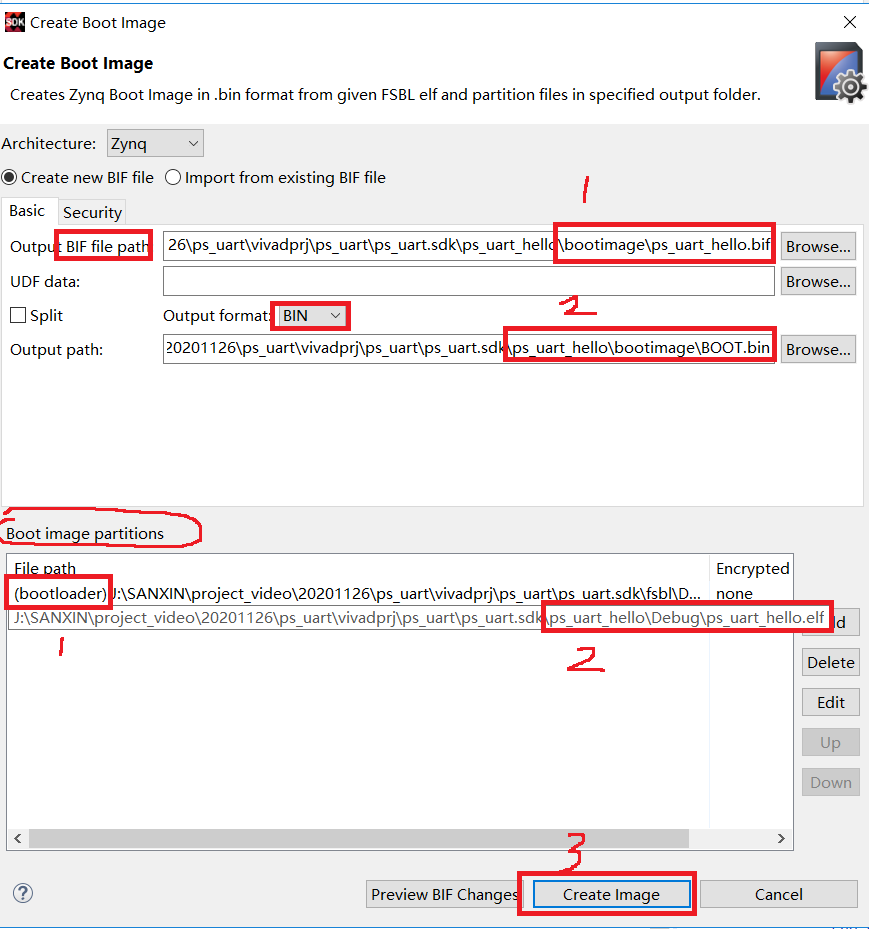

8.2、在彈出的對話框中可以看到BIF文件和BOOT.bin的生成路徑

BIF文件是生成BOOT.bin文件的配置文件;

BOOT.bin是我們需要的啟動文件,可以燒寫到SD卡、QSPI里

8.3、在彈出的對話框,Boot image partitions 列表中有要合成的文件

第一個文件一定是 bootloader 文件,就是上面生成的 fsbl.elf 文件;

第二個文件是 FPGA 配置文件 bitstream,本實驗沒有PL端程序,所以bitstream,不需要添加;

第三個是應用程序,在本實驗中為 ps_uart_hello.elf

8.4、由于沒有 bitstream,在本實驗中只添加 bootloader 和應用程序。點擊 Create Imag

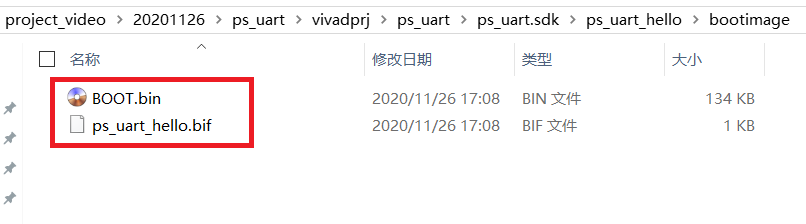

8.5、在生成的目錄下可以找到BOOT.bin文件

三、SD卡燒寫及測試

1、格式化 SD 卡,只能格式化為 FAT32 格式,其他格式無法啟動

2、放入 BOOT.bin 文件,放在根目錄

3、D 卡插入開發板的 SD 卡插槽

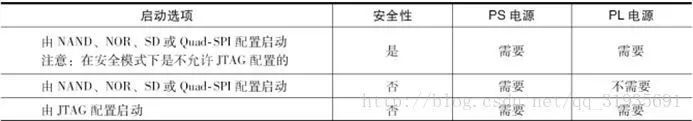

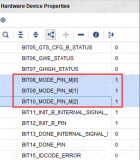

4、啟動模式調整為 SD 卡啟動

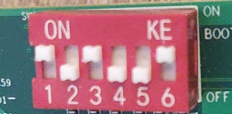

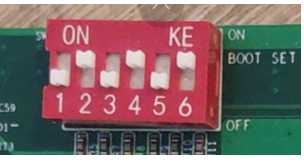

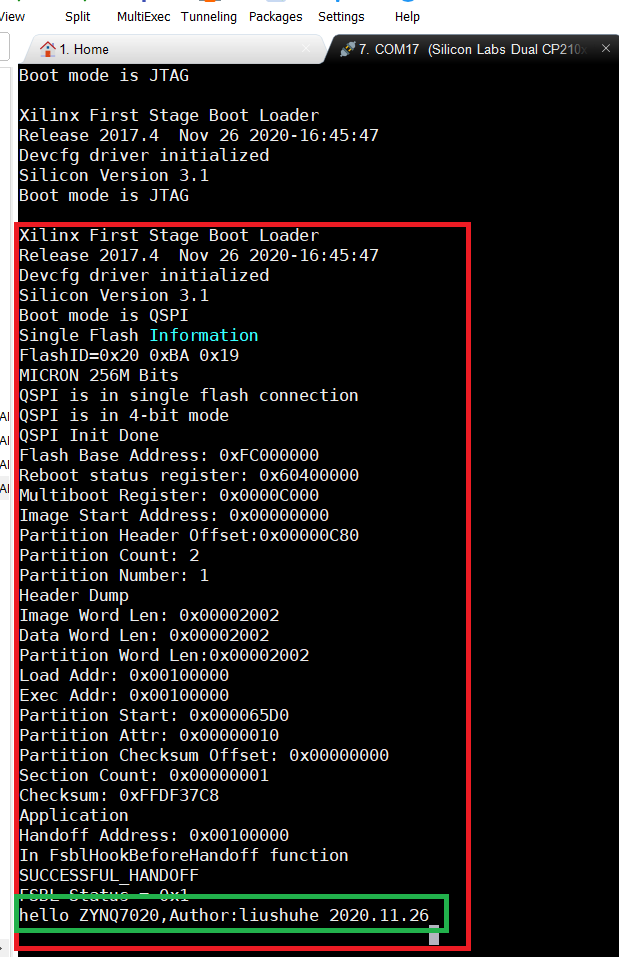

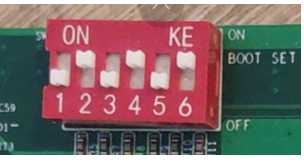

開發板設置撥碼為【 101001(1~6 SD卡 模式)】

5、打開串口,開發板上電

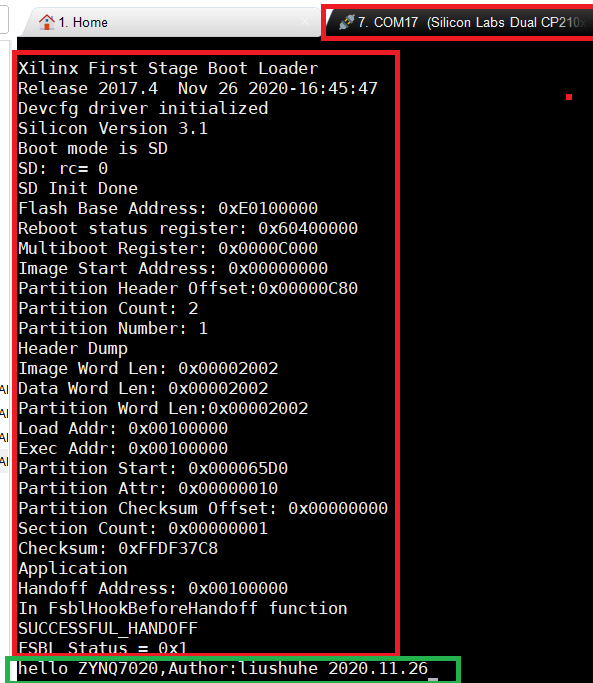

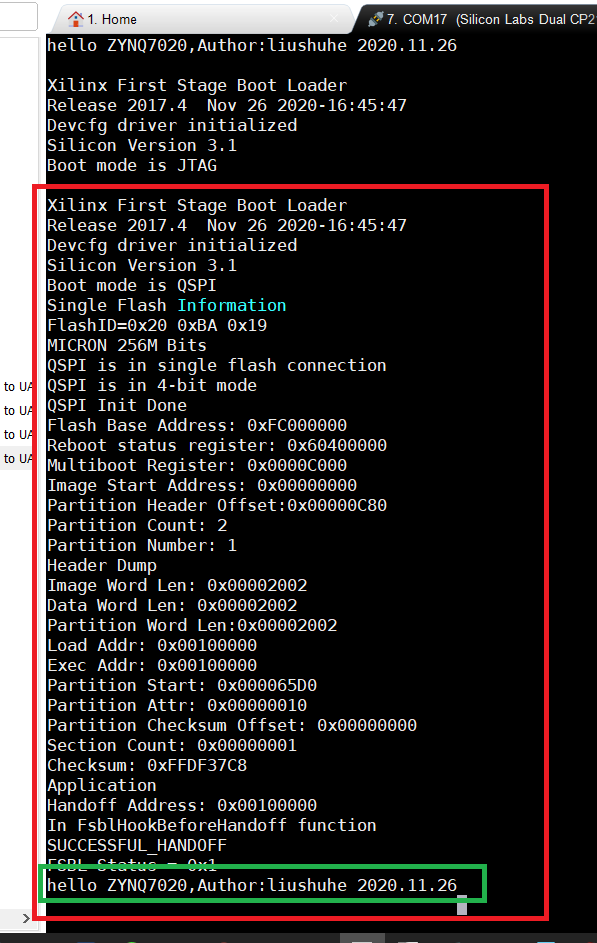

6、可以看到SD卡啟動成功,紅色部分為FSBL打印信息,綠色為我們的APP打印信息

7、SD卡固化成功

四、QSPI程序固化

QSPI 燒寫有2種方式:xSDK軟件燒寫、或者Vivado軟件燒寫

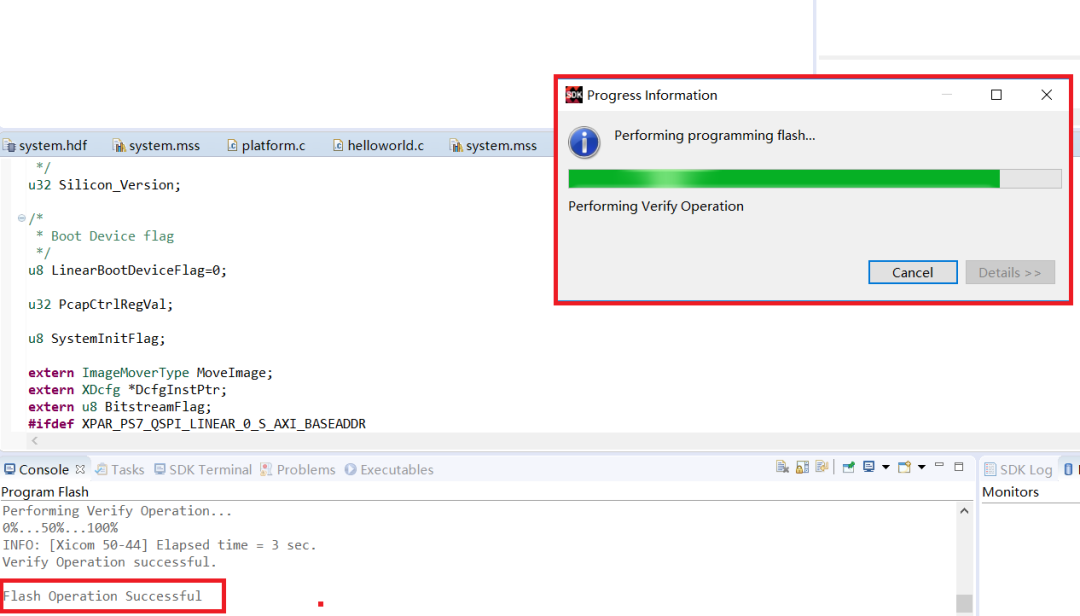

五、QSPI燒寫及測試(xSDK軟件燒寫)

首先將開發板設置為JTAG模式【 010101(1~6 JTAG 模式)】

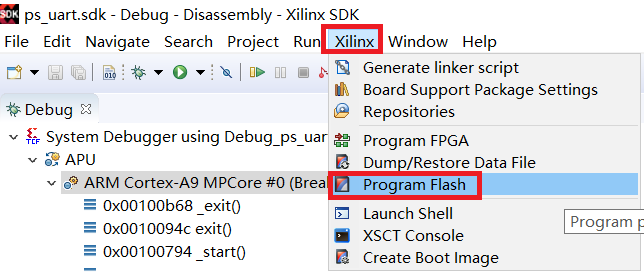

1、在 SDK 菜單 Xilinx -》 Program Flash

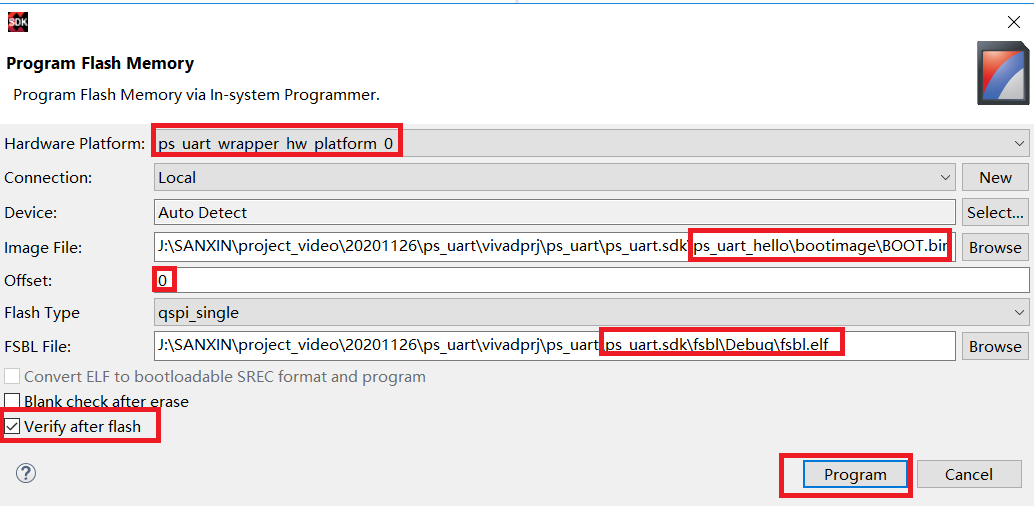

2、參數配置

《1》、Hardware Platform 選擇我們自己定制的平臺;

《2》、Image FIle 文件選擇要燒寫的 BOOT.bin;

《3》、FSBL file 選擇創龍定制的 fsbl.elf,只有用這個 fsbl 才能燒寫(我會另寫一篇博客單獨寫怎么定制fsbl.elf文件);

《4》、選擇 Verify after flash,在燒寫完成后校驗 flash

3、注意:第一次固化的時候,里面有uboot在執行,燒寫不成功,所以要先在軟件點固化,然后快速給開發板上電

4、將啟動設置為QSPI【 100101(1~6 QSPI 模式)】,驗證固化有沒有成功

5、打印的信息和我們在DUBUG的時候一致,代表我們固化成功

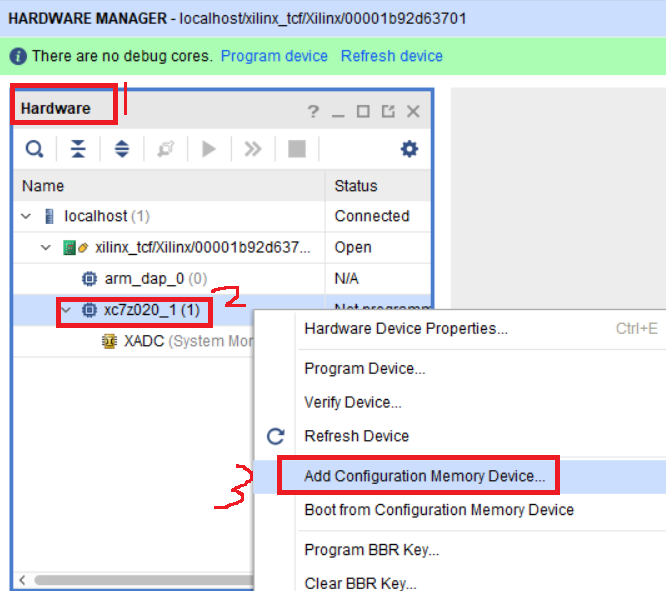

五、QSPI燒寫及測試(vivado軟件燒寫)

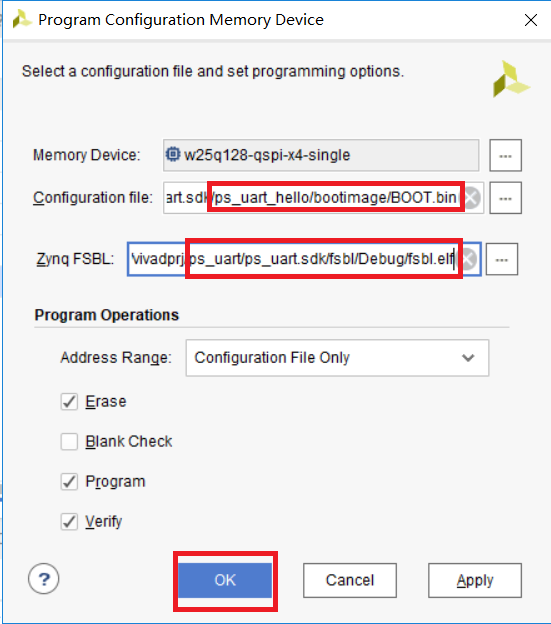

1、在 HARDWARE MANGER 下選擇器件,右鍵 Add Configuration Memory Device

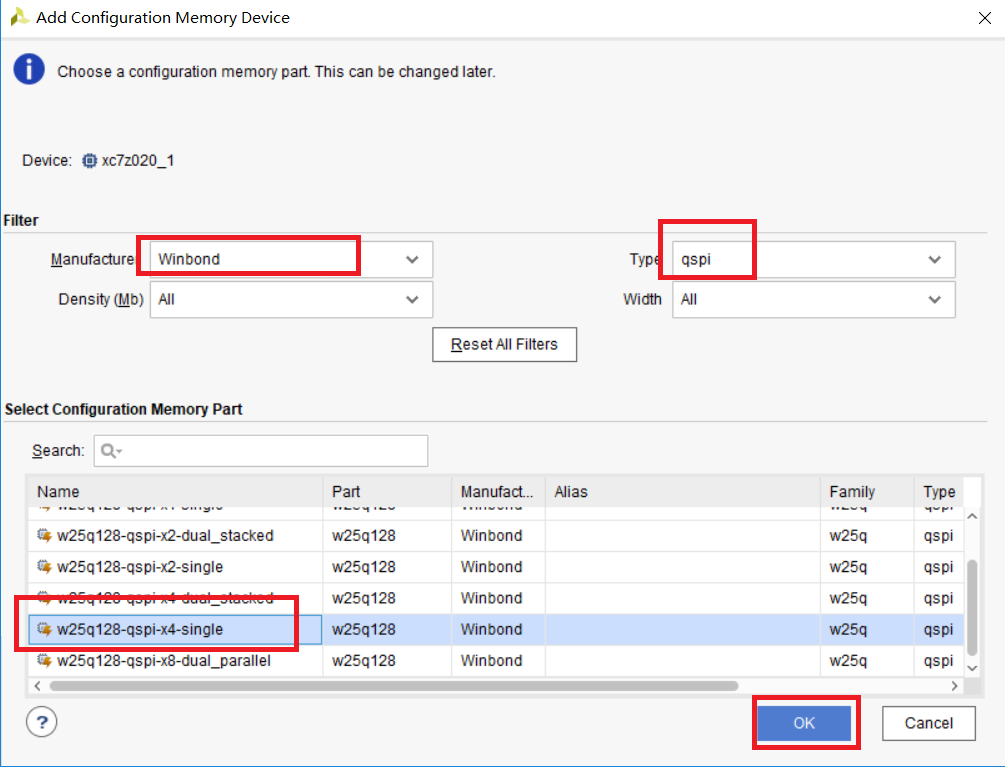

2、選擇嘗試 Winbond,類型選擇 qspi,寬度選擇 x4-single,這時候出現 w25q128

選擇紅框型號,開發板使用 MT25QL256ABA1EW9-0SIT,但是不影響燒錄

3、在彈出的對話框,提示我們是否立即燒寫,點擊OK

選擇ps_uart_hello/bootimage/目錄的BOOT.bin,選擇fsbl/debug/目錄下的fsbl.elf文件

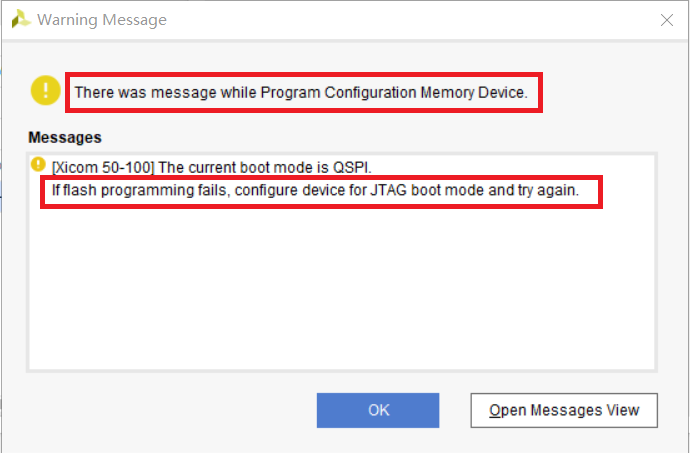

4、提示我們當前是處于QSPI模式的,如果編程失敗,請更改模式,再次重試

5、我們將啟動模式改為JTAG模式【 010101(1~6 JTAG 模式)】

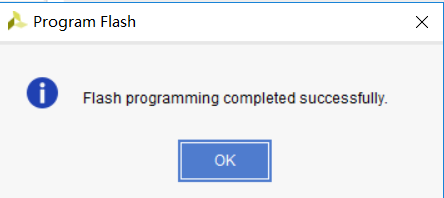

6、斷電上電,再次嘗試燒寫,沒有剛才的警告信息了

7、再將啟動模式切換為QSPI模式,QSPI【 100101(1~6 QSPI 模式)】,驗證固化有沒有成功

六、到此PS端的程序固化成功

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601858 -

FlaSh

+關注

關注

10文章

1621瀏覽量

147754 -

程序

+關注

關注

116文章

3777瀏覽量

80851 -

Zynq

+關注

關注

9文章

608瀏覽量

47128

原文標題:學員筆記精選 | ZYNQ7000系列基本開發流程 之 《PS端程序固化》篇

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

詳解Zynq的兩種啟動模式

ZYNQ 的啟動流程介紹

ZYNQ 的啟動流程介紹

評論