這篇文章記錄ZYNQ7020的PS端的基本開發(fā)流程,關于PL端的開發(fā)流程,參考之前文章,這里放個超鏈接。

學員筆記連載 | Day5 Xilinx ZYNQ7000系列 PS、PL、PS-PL基本開發(fā)流程之PL端篇

本篇文章,以配置一個PS端的UART外設,并打印一句話《hello ZYNQ7020,Author:liushuhe 2020.11.26》來演示

ZYNQ7020的基本開發(fā)流程,本篇文章需要一點點的C語言知識,不會也不影響實驗的,跟著步驟做就行了。

一、任務分工

ZYNQ芯片分為PL和PS,PS端的IO分配相對是固定的,不能任意分配,雖然PS端的ARM是硬核,但是在ZYNQ當中也要將ARM硬核添加到工程當中才能使用,FPGA工程師負責把Vivado工程搭建好,提供好硬件給軟件開發(fā)人員,軟件開發(fā)人員便能在這個基礎上開發(fā)應用程序 ,軟件開發(fā)人員,不用關心FPGA的部分。

二、FPGA工程師搭建硬件平臺

我們這里演示搭建一個帶UART和arm A9處理器的硬件平臺

1.1、建立vivado工程

創(chuàng)建一個“ps_uart”的工程,具體過程,參考我文章開頭超鏈接文章;

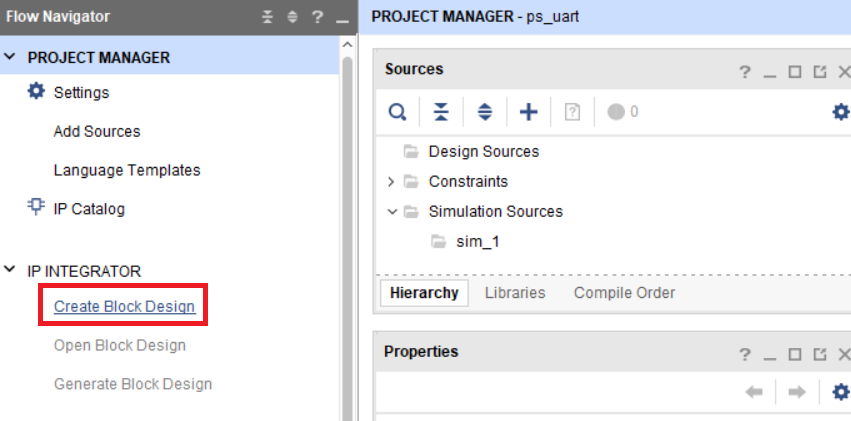

1.2、點擊“Create Block Design”,創(chuàng)建一個Block設計,也就是圖形化設計

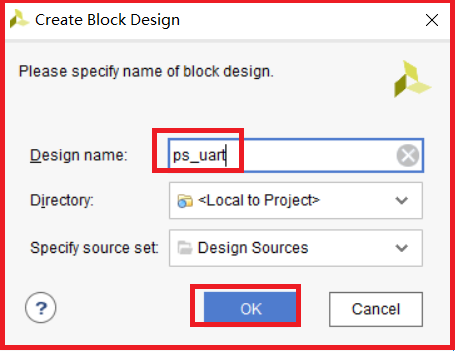

1.3、“Design name”可以不修改,我改成ps_uart便于識別

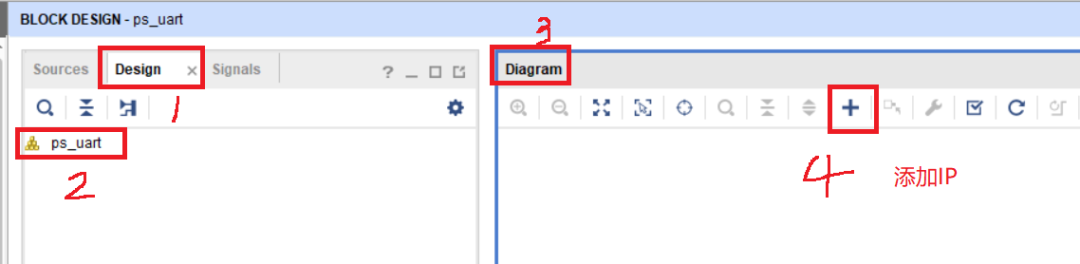

1.4、點擊“Add IP”快捷圖標

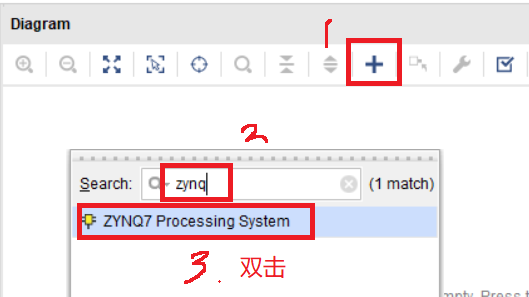

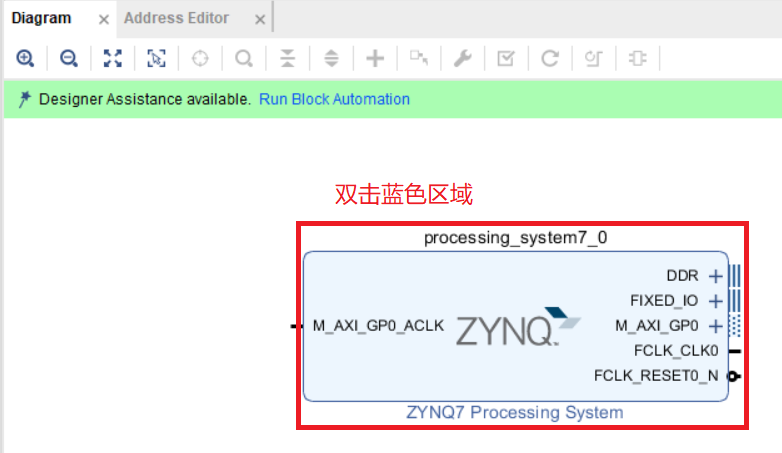

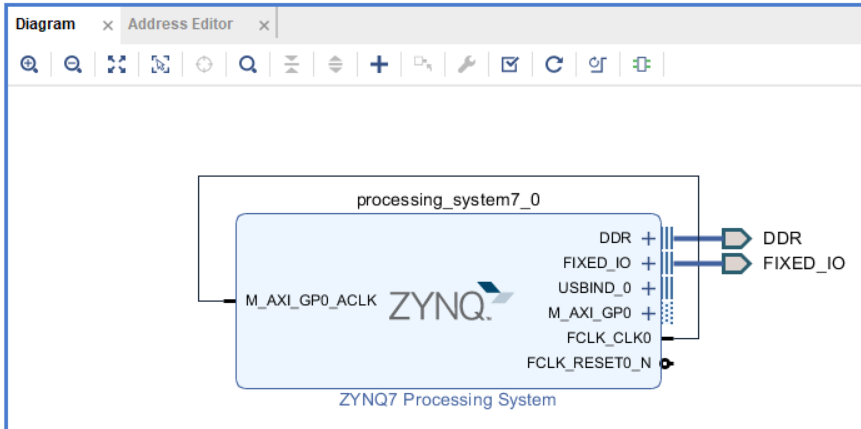

1.5、搜索“zynq”,在搜索結果列表中雙擊“ZYNQ7 Processing System

1.6、雙擊Block圖中的“processing_system7_0”(直接雙擊藍色區(qū)域),配置相關參數(shù)

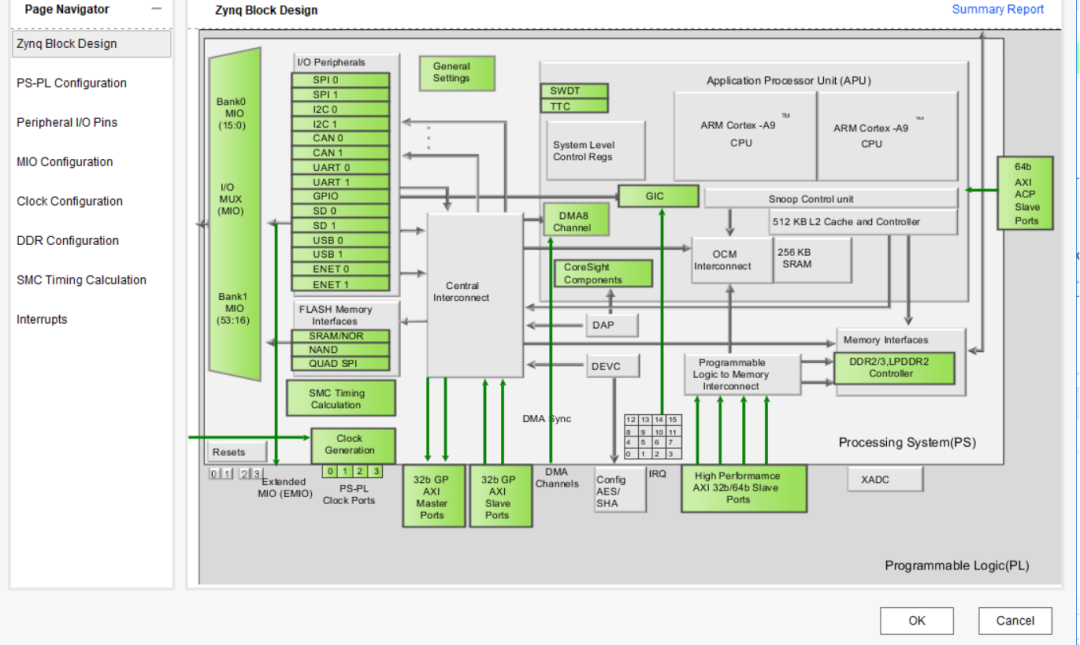

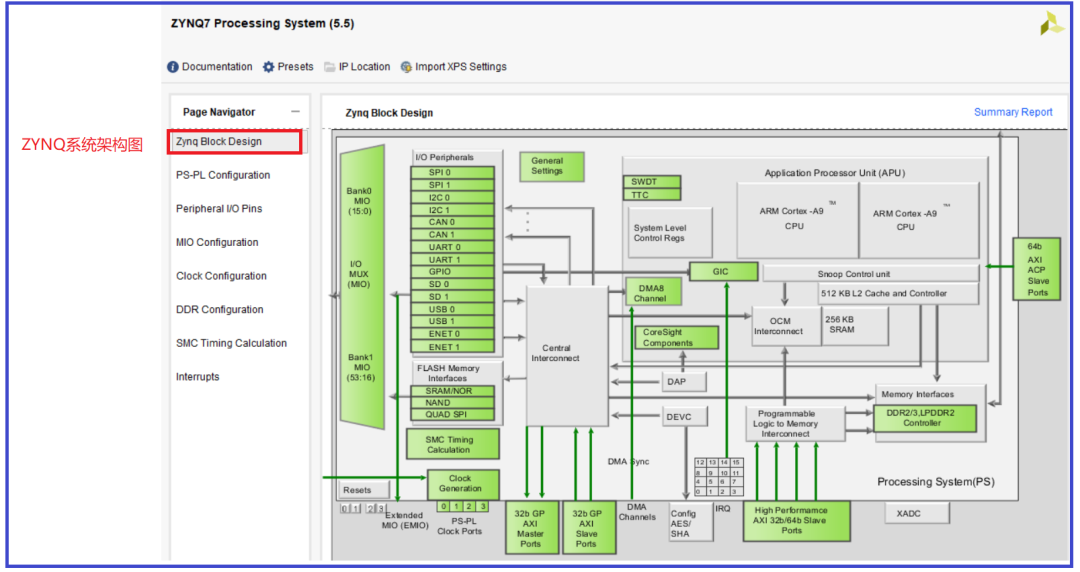

1.7、首先出現(xiàn)的界面是ZYNQ硬核的架構圖,可以很清楚看到它的結構,可以參考 官方文檔,在官網(wǎng)搜索ug585 即可

1.8、圖中綠色部分是可配置模塊,可以點擊進入相應的編輯界面

1.9、也可以在左側的窗口進入編輯 ,下面分別介紹左側選項代表的功能;

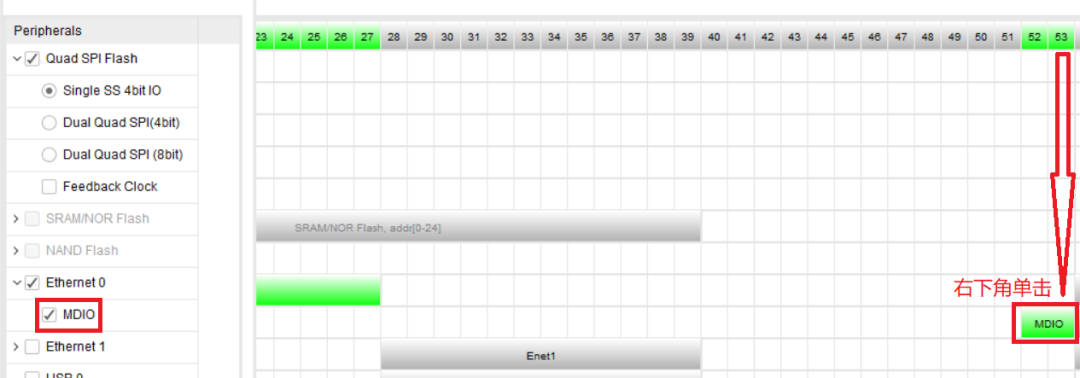

2.0、Zynq 塊設計參數(shù)配置,單擊綠色塊右下角,可以進行參數(shù)配置

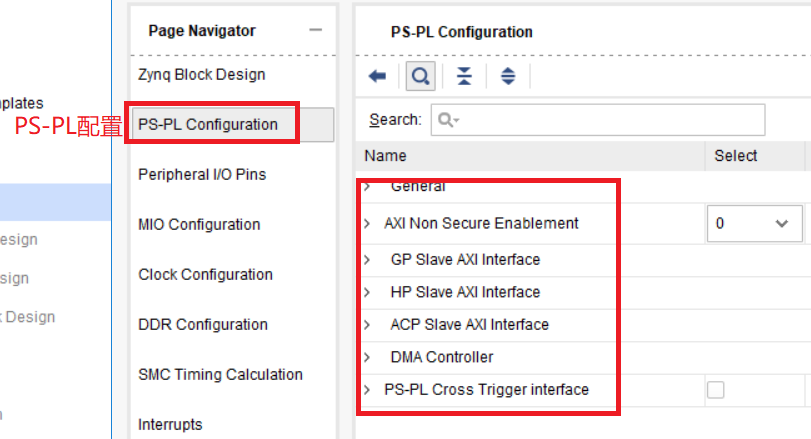

2.1、PS-PL Configuration 配置界面,主要是進行PS與PL之間接口的配置,主要是AXI接口,這些接口可以擴展PL端的AXI接口外設

核。

2.2、我們這篇文章是PS開發(fā)流程,關于PS-PL Configuration 配置在這里保持默認,在后面的實驗中我再補充

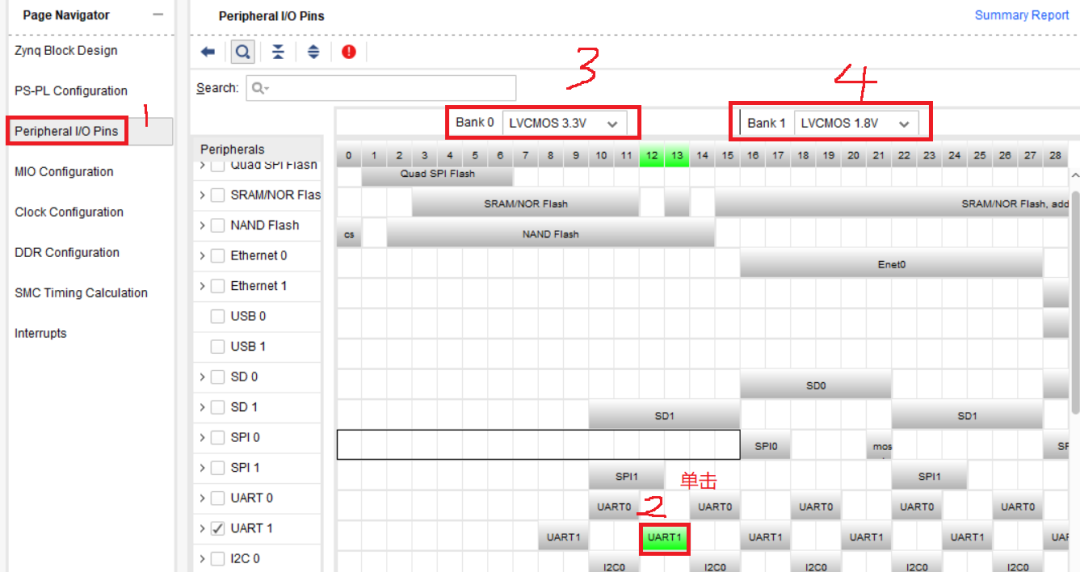

2.3、外設配置,ZYNQ的PS端外設很多是復用的 ,同一引腳可以配置為不同的功能

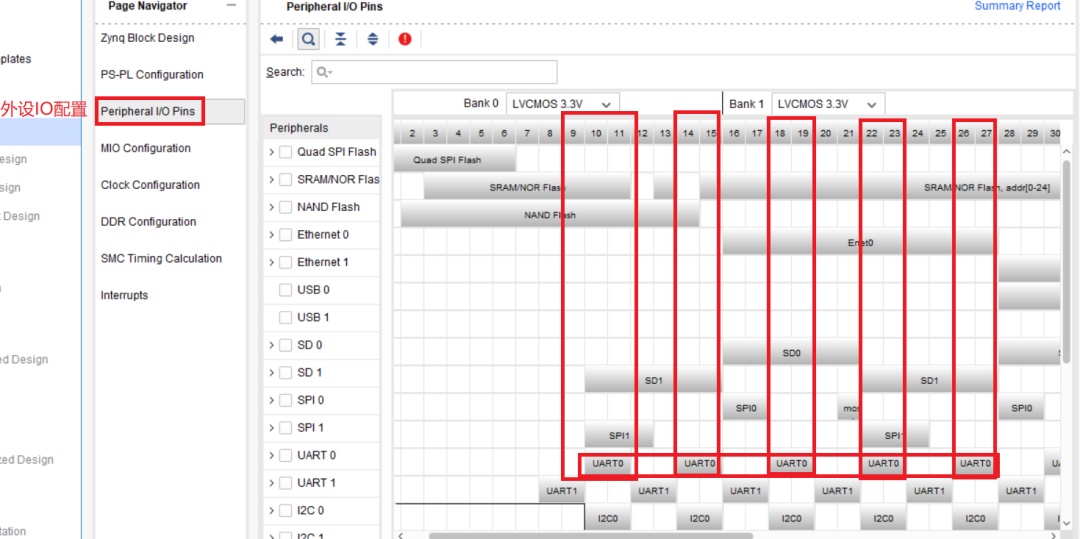

zynq內部只有2個串口,UART0、UART1、我們看UART0可以接在(10、11)/(14、15)/(18、19)/(22、23)/(26、27)

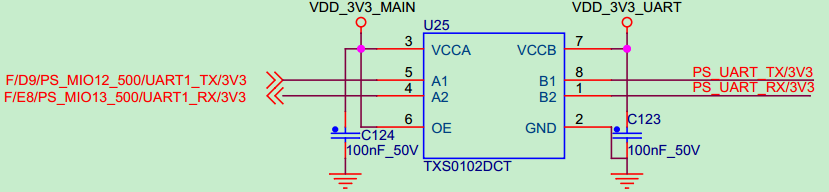

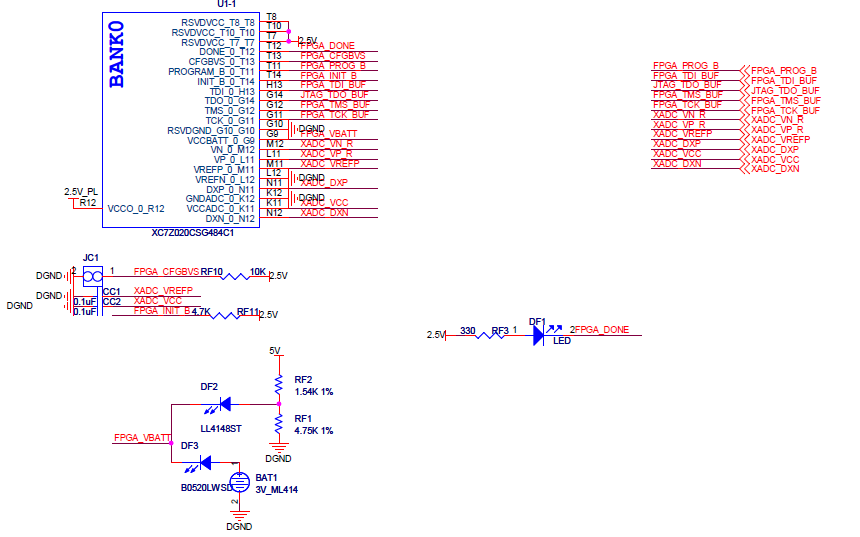

2.4、配置串口,我們的ps_uart需要一個串口來打印消息,查看ZYNQ7020開發(fā)板的原理圖

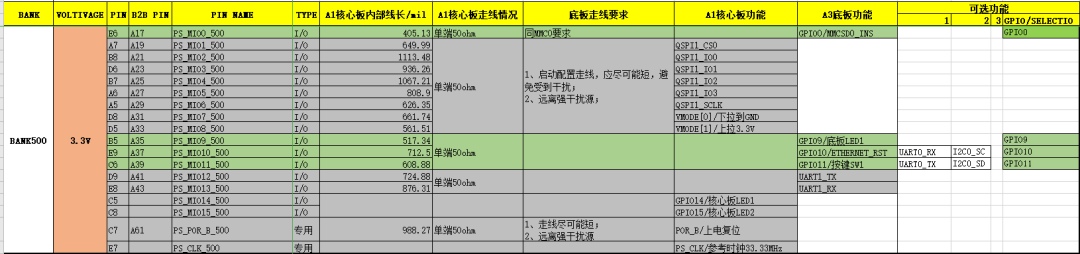

從原理圖看出,ZYNQ的PS端的串口,連接的是MIO12、MIO13端口,并且電源是3.3v

2.5、從I/O分配看,MIO12、MIO13是串口1,在MIO12、MIO13引腳對應串口上單擊,會看見該模塊變?yōu)榫G色,即代表分配成功

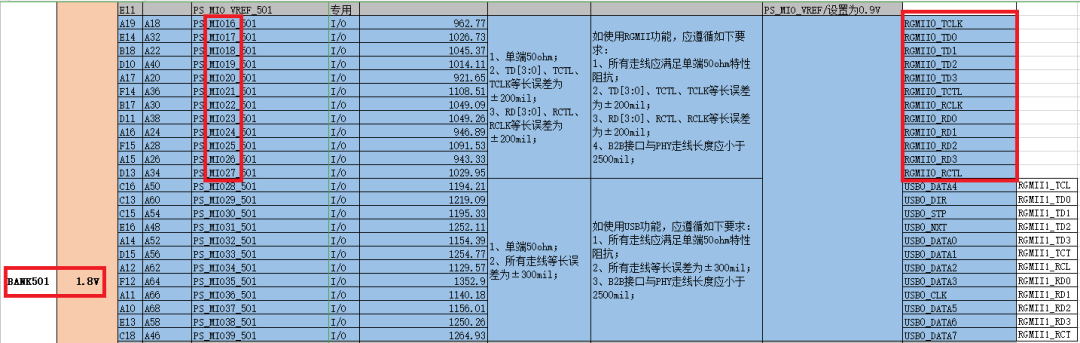

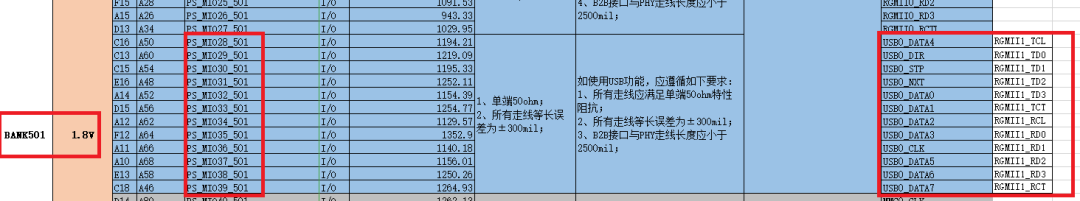

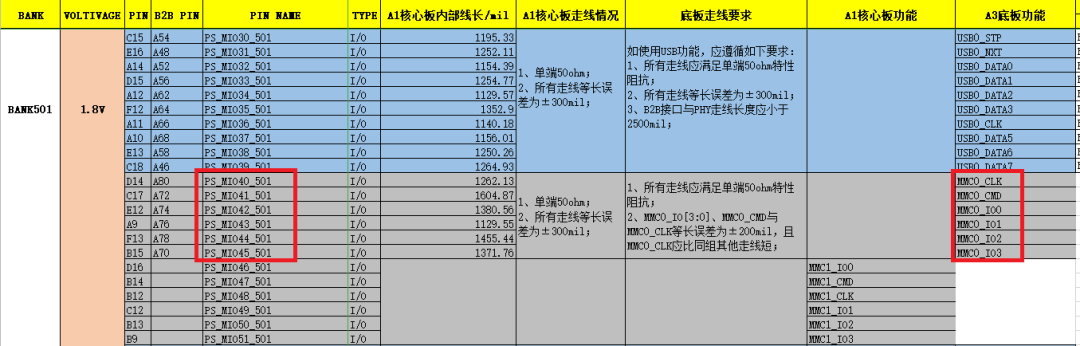

關于BANK0、BANK1的電壓,由于創(chuàng)龍沒有給核心板的原理圖,但是給了一個WORD的描述文檔,大家也要熟悉這個方式

國內很多廠家都是這樣,屬于技術保密

按照上述表格分配UART1電壓和引腳

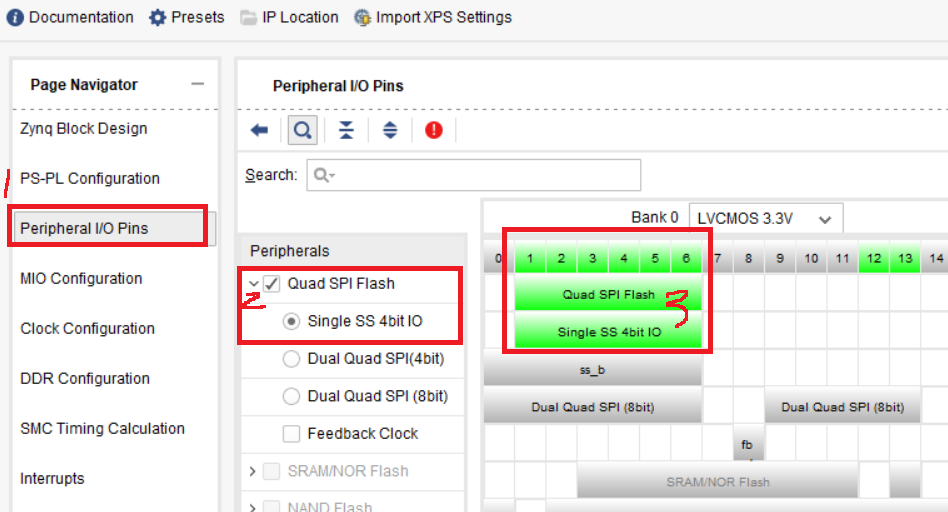

2.6、配置QSPI,QSPI可以作為ZYNQ的啟動存儲設備,ZYNQ可以通過讀取QSPI中存儲的啟動文件加載ARM和FPGA

從核心板word表格和創(chuàng)龍給的例程,得知我們選擇Quad SPI Flash為Single SS 4bit IO

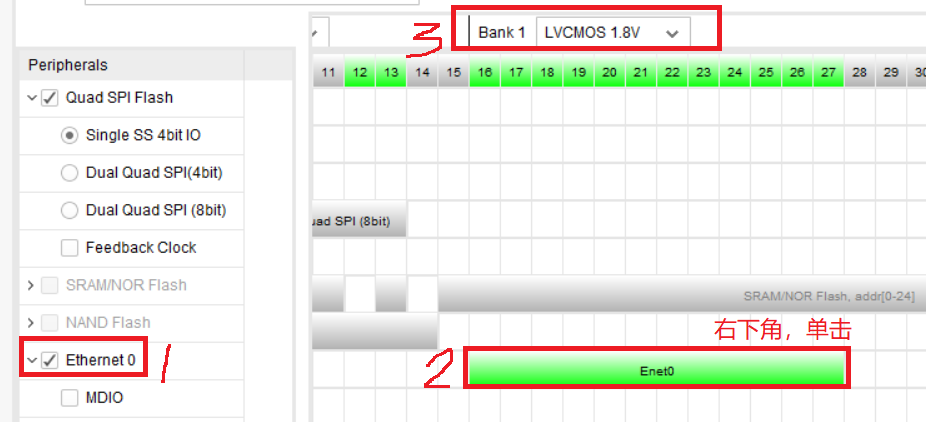

2.7、配置以太網(wǎng),在PS端設計有以太網(wǎng)接口

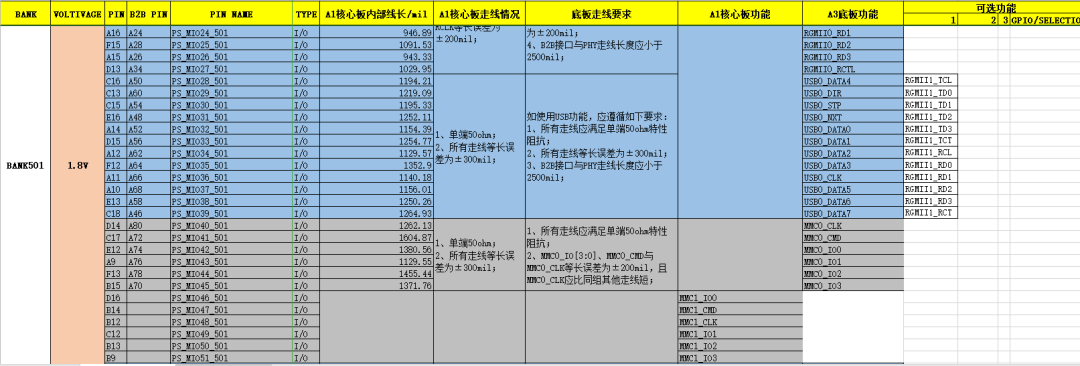

1、根據(jù)原理圖選擇Ethernet 0到MIO16-MIO27

電壓是1.8v

2、配置PHY寄存器配置接口,選擇MDIO并配置到MIO52-MIO53

2.8、配置USB0到MIO28-MIO39

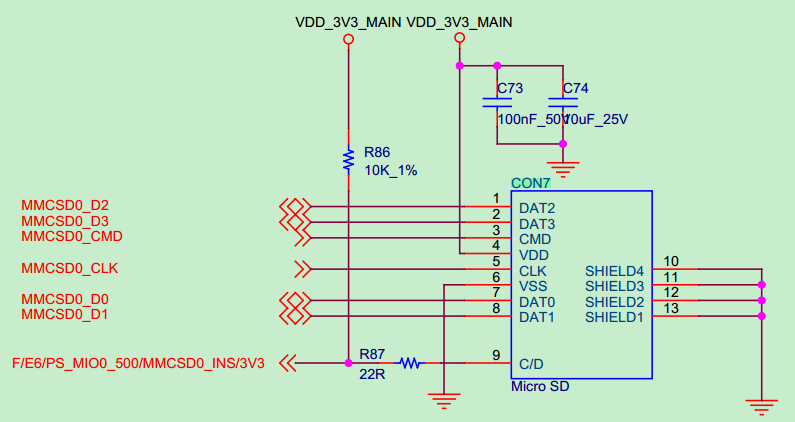

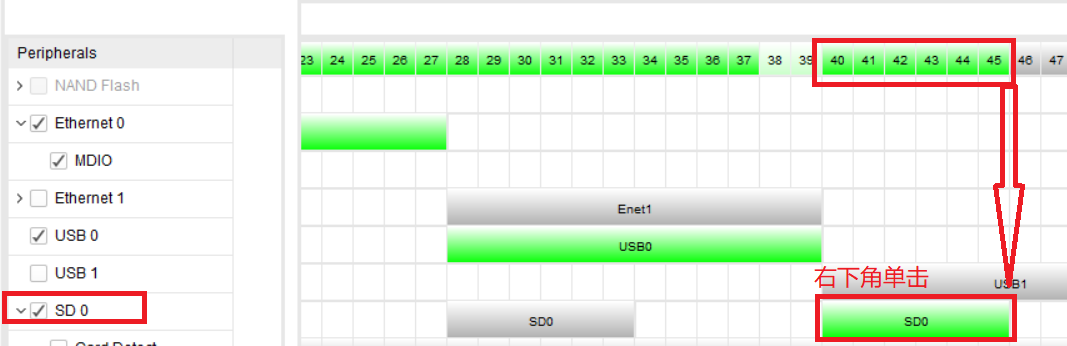

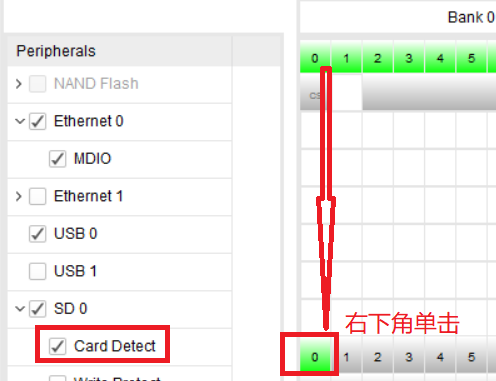

2.9、ZYNQ還可以SD卡啟動

查看底板原理圖,選擇 SD 0,配置到 MIO40-MIO45,選擇Card Detection MIO0,用于檢測 SD 卡的插入。

1、配置SD0

2、選擇Card Detection MIO0,用于檢測SD卡的插入

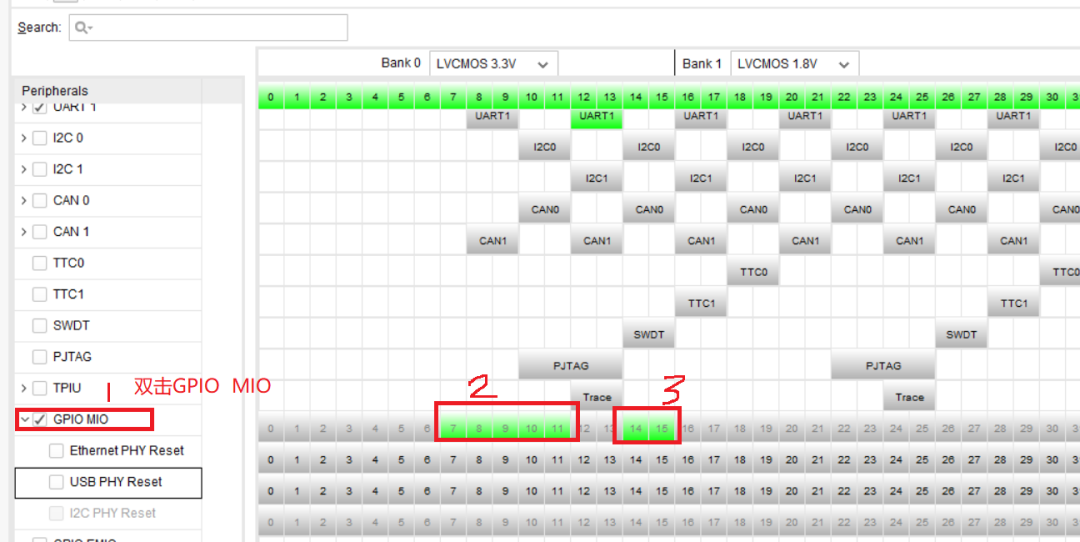

3.0、控制剩余未分配的MIO,用作GPIO ,打開GPIO MIO,PS便可以配置

1、雙擊GPIO MIO當出現(xiàn)打鉤的提示時,軟件會自動把我們未使用到的IO分配為GPIO

2、到這里引腳分配全部完成,如果以后做實驗需要配置其他外設,可以參考這個文章,作相應的修改即可

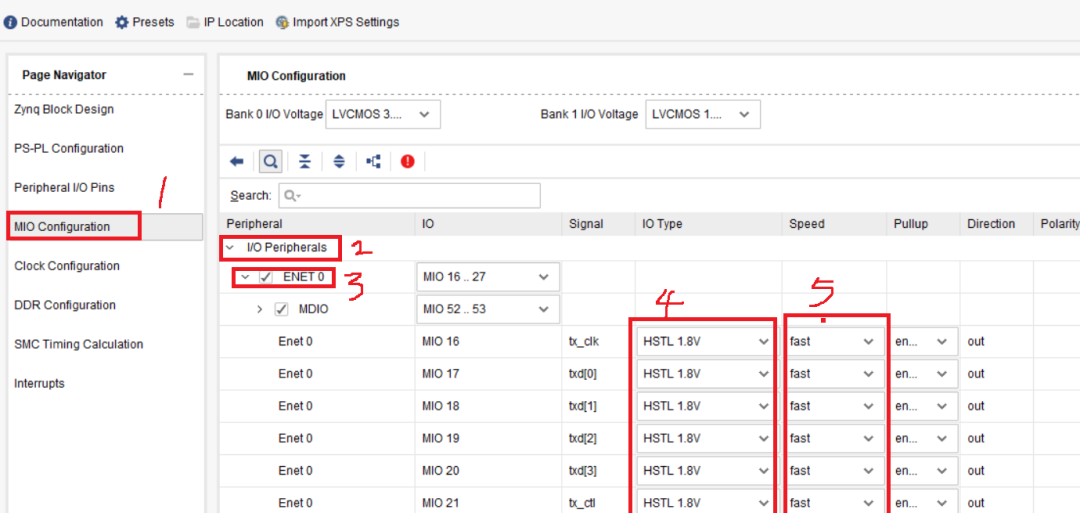

3.1、MIO配置

修改 Enet0的電平標準為 HSTL 1.8V, Speed 為 fast,這些參數(shù)非常重要,如果不修改,網(wǎng)絡可能不通。其他部分保持默認。

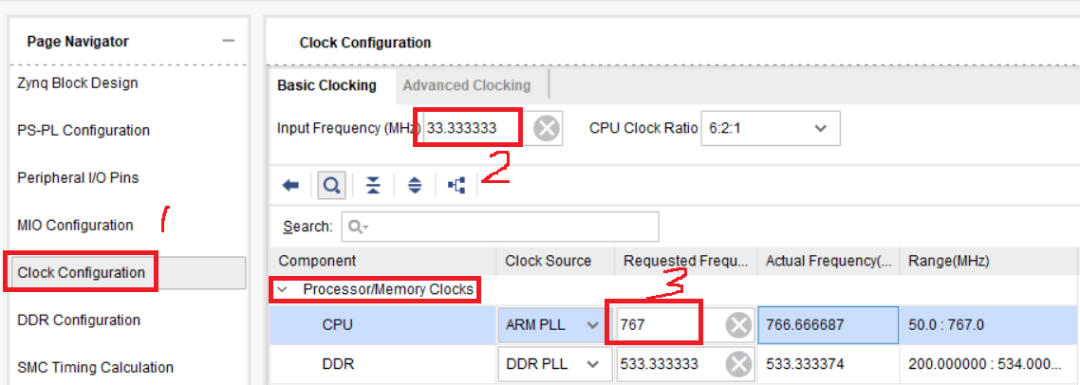

3.2、時鐘配置

在“Clock Configuration”選項卡中我們可以配置PS時鐘輸入時鐘頻率,這里默認是33.333333,和板子上一致,不用修改,

CPU 頻率改為 767Mhz,同時 PS 還可以給 PL 端提供 4 路時鐘,頻率可以配置,這里不需要,所以保持默認即可。

還有 PS 端外設的時鐘等也可以進行配置,這里保持默認。

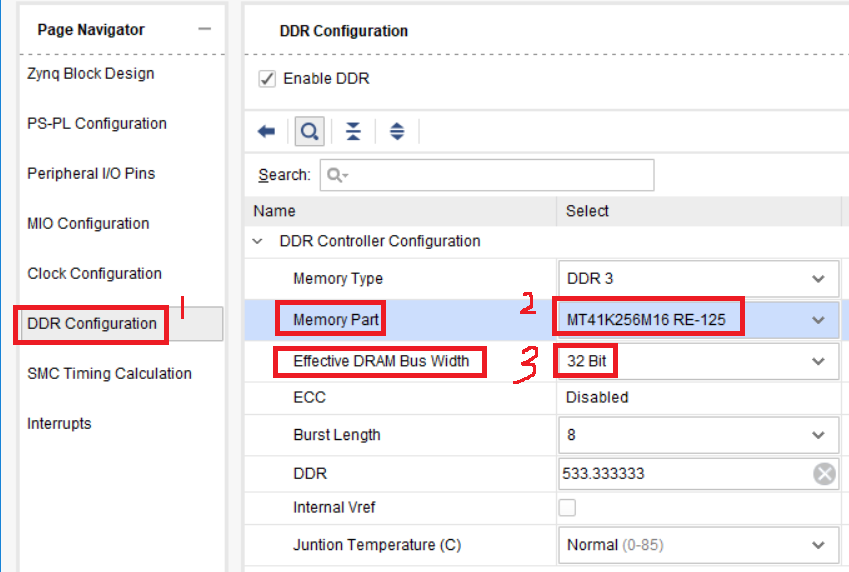

3.3、DDR3配置

在“DDR Configuration”選項卡中可以配置PS端ddr的參數(shù)

根據(jù)創(chuàng)龍的例程,內存芯片我們選擇《MT41K256M16 RE-125》,Effective DRAM Bus Width 選擇《32bit》

其他部分保持默認,點擊OK

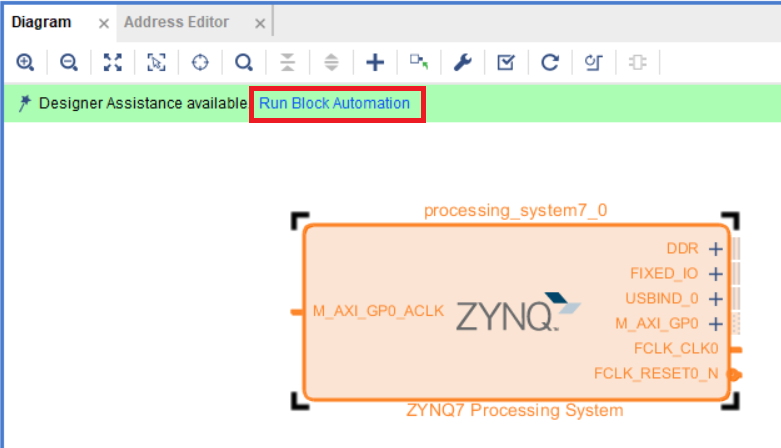

3.4、到這里ZYNQ核的配置完成,我們配置參數(shù)及導出硬件信息

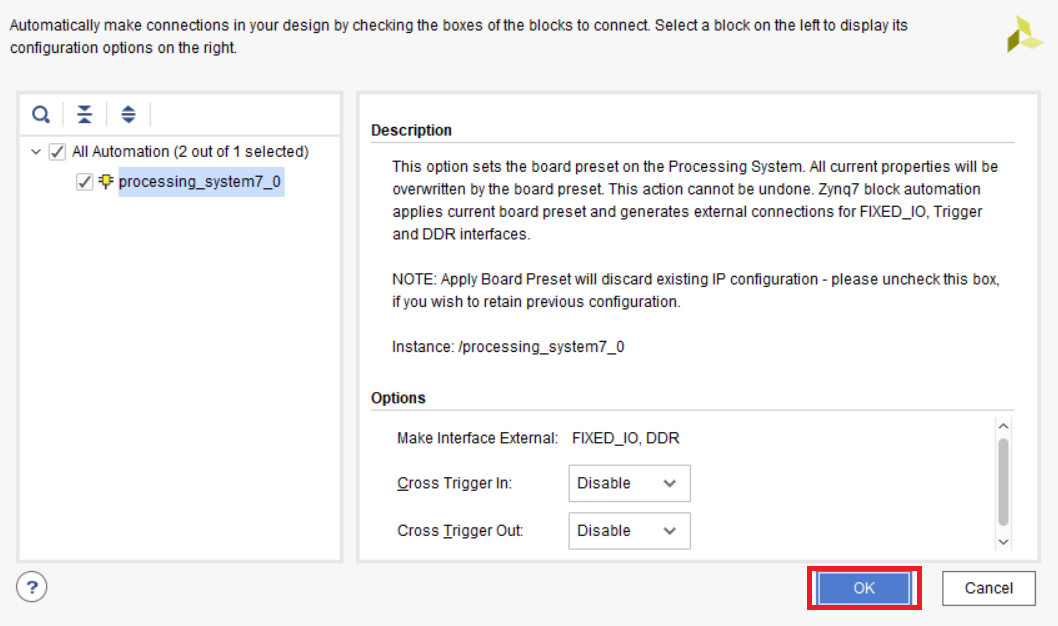

1、點擊“Run Block Automation”,vivado軟件會自動完成一些導出端口的工作

2、按照默認點擊“OK”

3、連接FCLK_CLK0到M_AXI_GP0_ACLK,按Ctrl+S保存設計

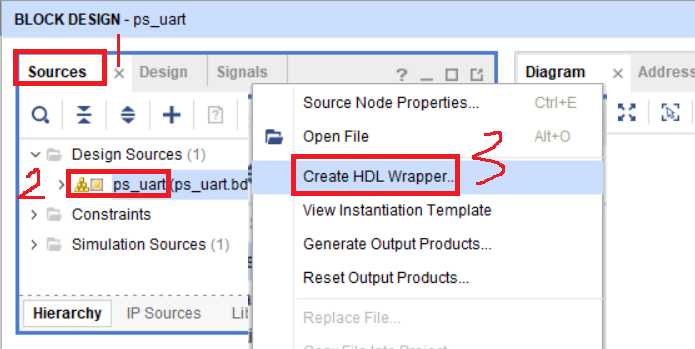

4、選擇Block設計,右鍵“Create HDL Wrapper...”,創(chuàng)建一個Verilog或VHDL文件,為ps_uart生成HDL頂層文件

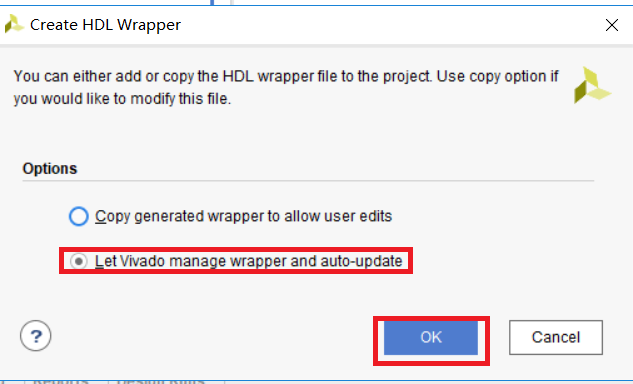

5、在彈出對話框,選擇讓vivado軟件自動更新 頂層文件

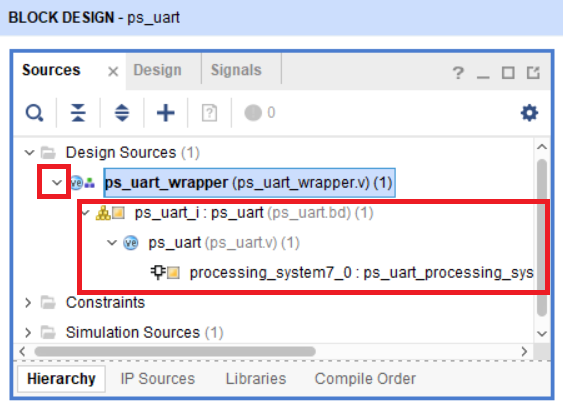

6、展開設計可以看到PS被當成一個普通IP來使用 ,之前生成那個頂層文件,其實就是為了把我們的硬件配置

生成一個IP核,供我們調用

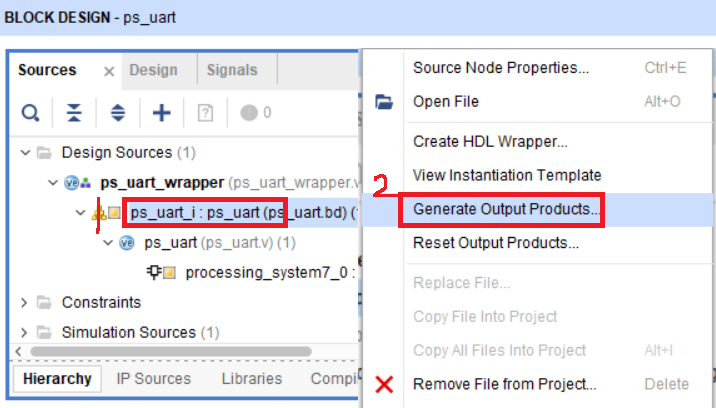

7、選擇block設計,右鍵“Generate Output Products”,此步驟會生成block的輸出文件,包括IP,例化模板, RTL 源文件, XDC 約束,第三方綜合源文件等等。供后續(xù)操作使用。

8、點擊“Generate”

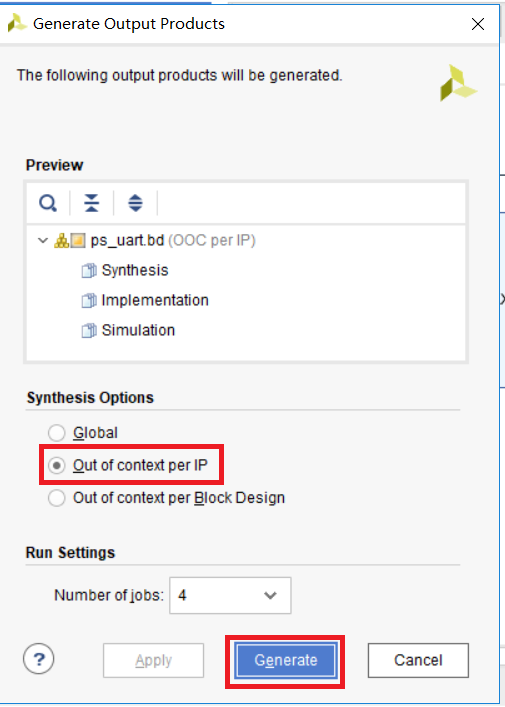

9、PS端的引腳不需要綁定 ,因為在生成的IP文件包含了PS端引腳分配的XDC文件

在IP Sources,Block Designs->ps_uart->Synthesis中,可以看到處理器的XDC文件,綁定了PS端的IO,因此不需要再新建XDC綁定這些引腳

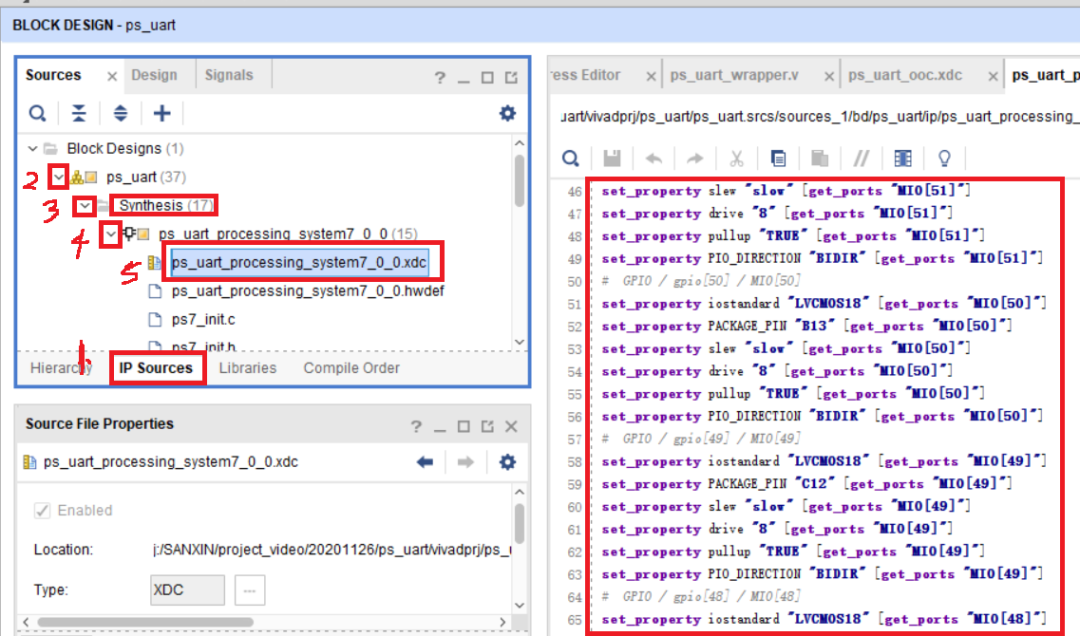

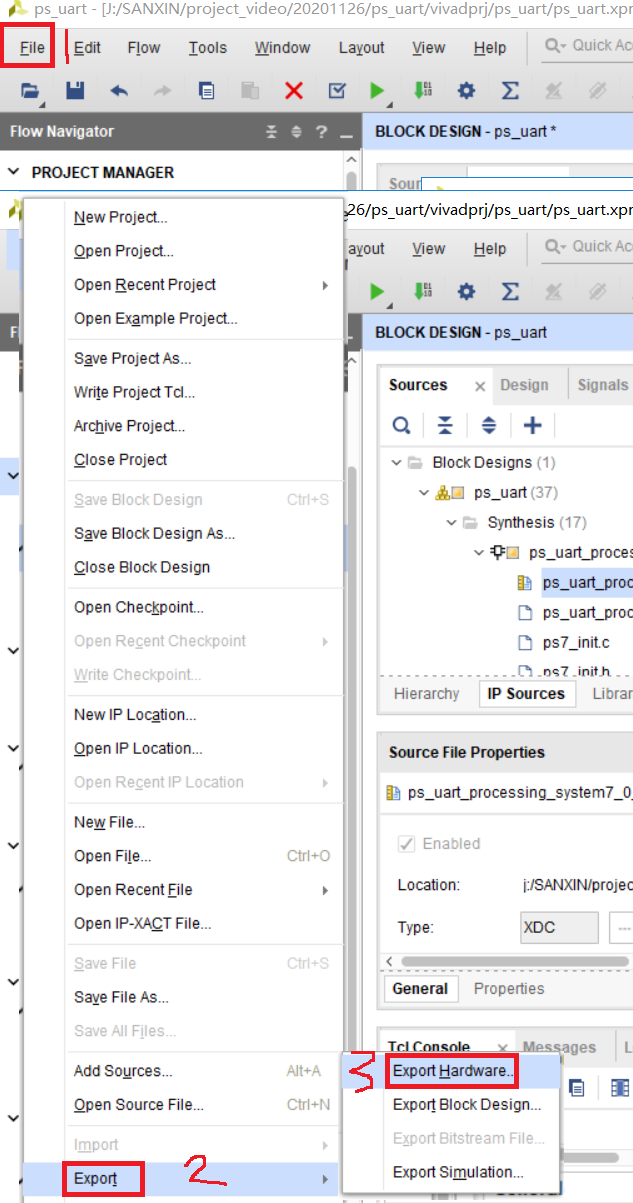

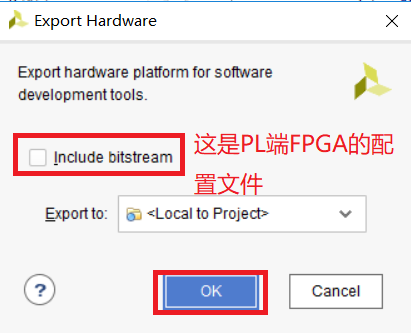

10、在菜單欄“File -> Export -> Export Hardware...”導出硬件信息,這里就包含了 PS 端的配置信息。

11、在彈出的對話框中點擊“OK”

12、因為我們這個實驗僅僅是使用了PS的串口,不需要PL參與,這里就沒有使能“Include bitstream” ,關于PS-PL的聯(lián)合實驗,我會另寫一篇

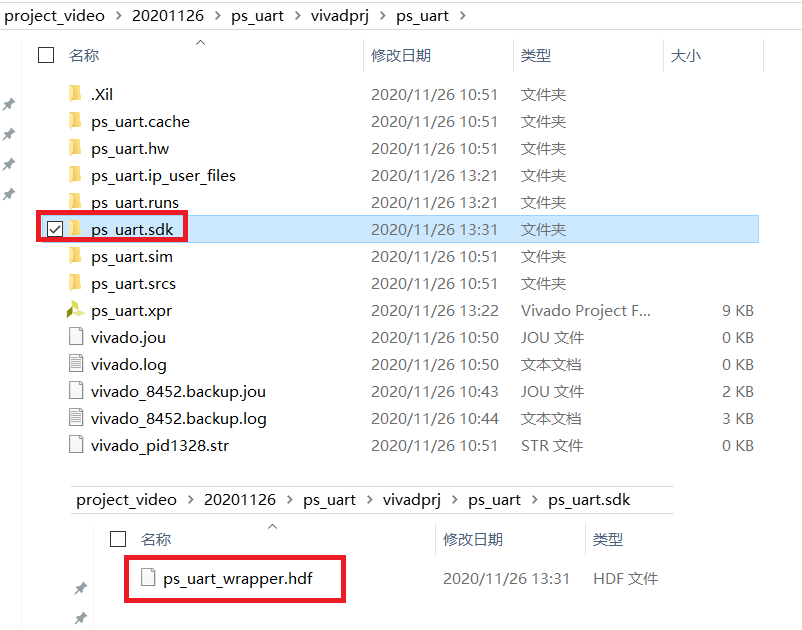

13、此時會多出 xx.sdk 文件夾,并且有個 hdf 文件,這個文件就是這個文件就包含了 Vivado 硬件設計的信息,供軟件開發(fā)人員使用。

14、到此為止, FPGA 工程師工作告一段落,剩下的工作交給ARM軟件開發(fā)人員。

二、ARM軟件編寫C語言程序,在串口打印一句話《hello ZYNQ7020,Author:liushuhe 2020.11.26》

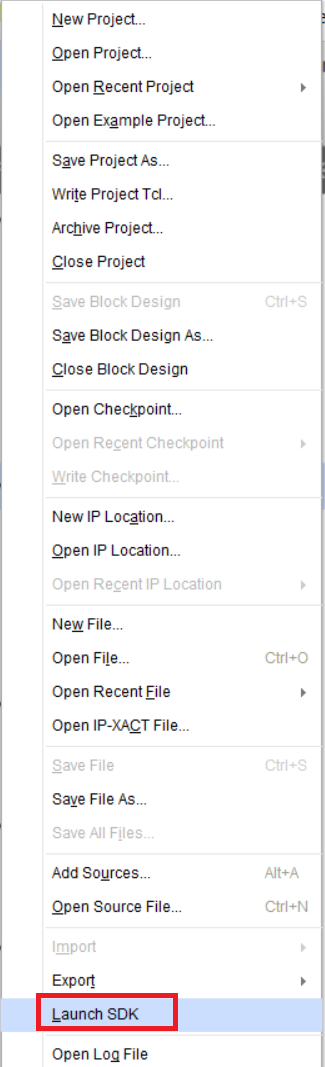

1、點擊Vivado菜單“File -> Launch SDK”,啟動SDK

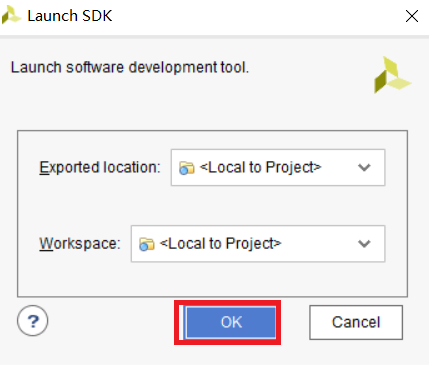

2、在彈出的對話框選擇OK

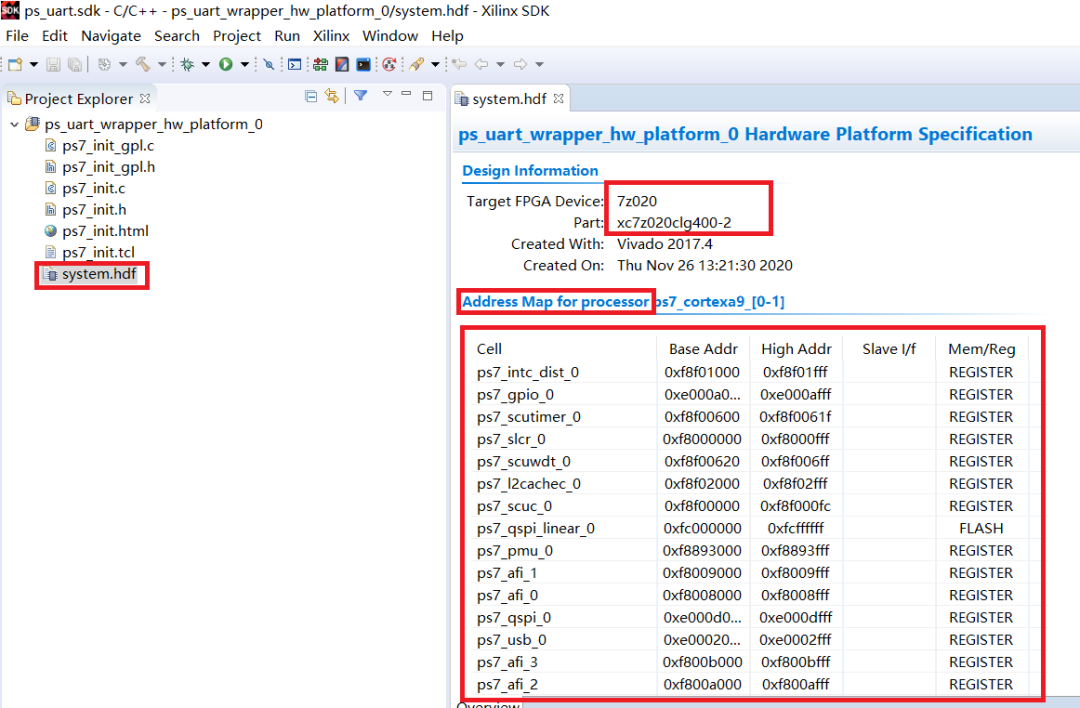

3、啟動SDK后我們會看到一個文件夾,有一個名為"system.hdf”文件,這個文件就包含了

Vivado硬件設計的信息,可以給軟件開發(fā)使用,也可以看到 PS 端外設的寄存器列表。

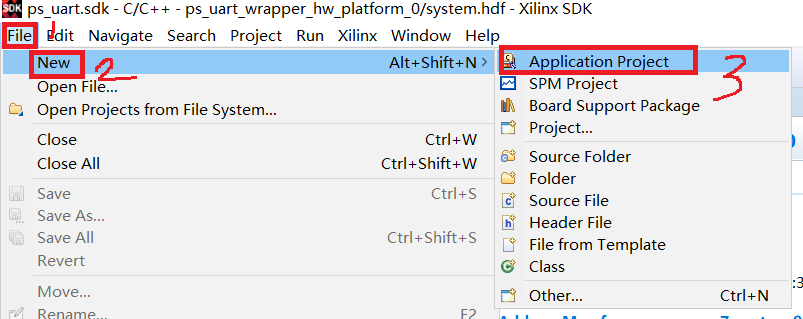

4、在SDK的菜單“New -> Application Project”,建立一個APP工程

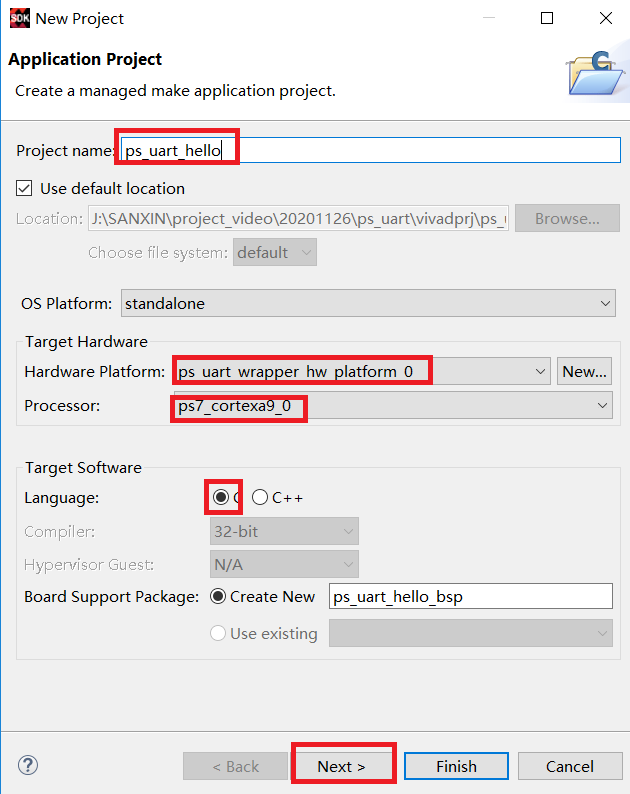

4、在彈出的對話框中,“Project name”填寫“ps_uart_hello”,硬件平臺選擇我們自己定義的ps_uart_wrapper_hw_platform

語言C、其他默認,點擊“Next”

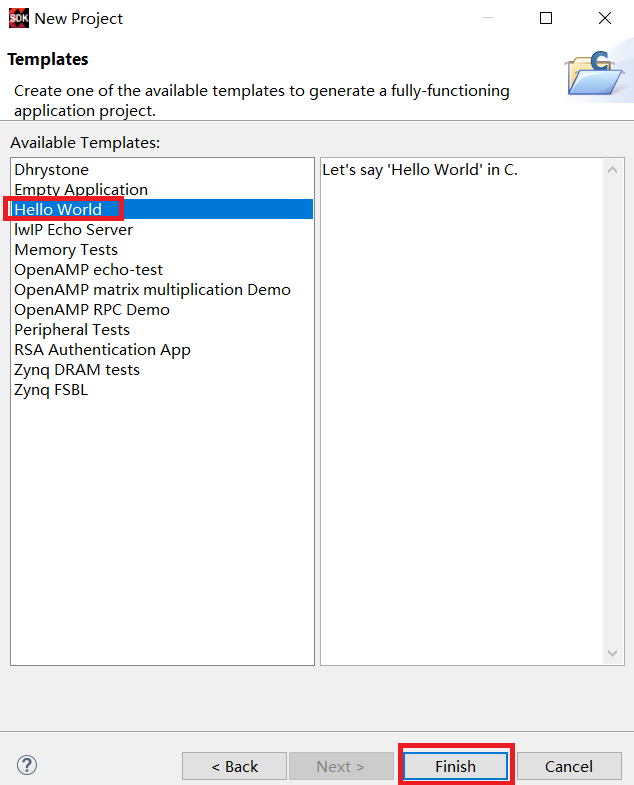

5、模板選擇《hello world》,點擊Finish

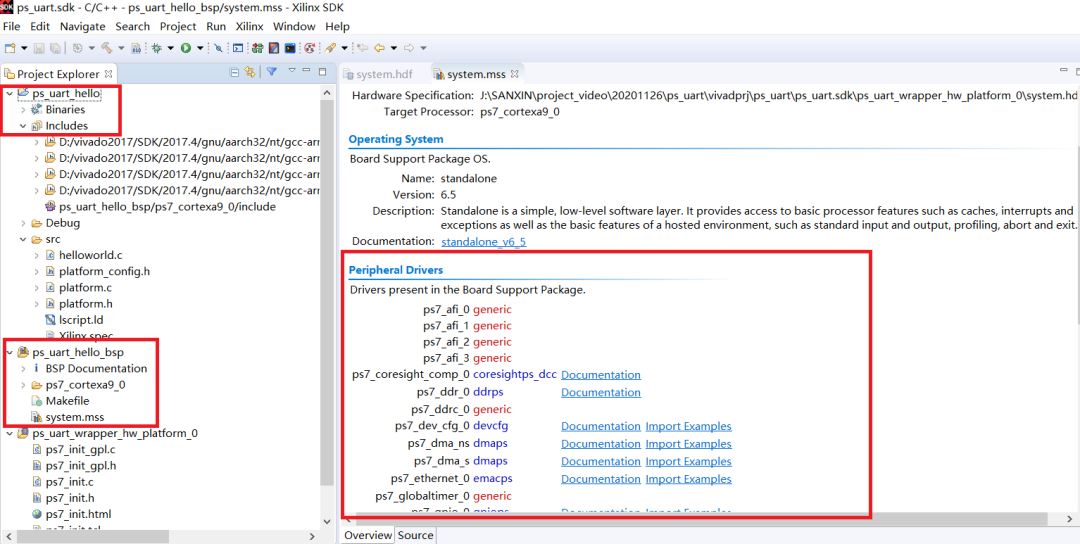

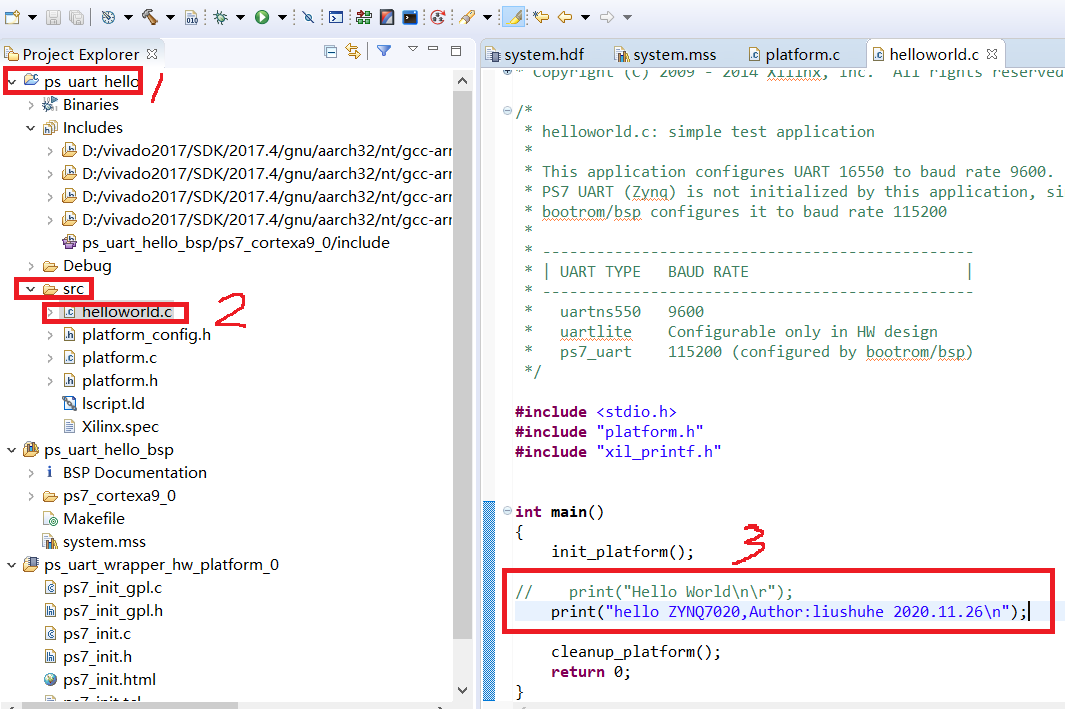

6、可以看到SDK創(chuàng)建了一個“ps_uart_hello”目錄,還有一個“ps_usrt_hello_bsp”的目錄,在“ps_usrt_hello_bsp”目錄中可以找到很多有用的信息,軟件開發(fā)人員比較清楚,BSP也就是 Board Support Package板級支持包的意思,里面包含了開發(fā)所需要的驅動文件,用于應用程序開發(fā)。

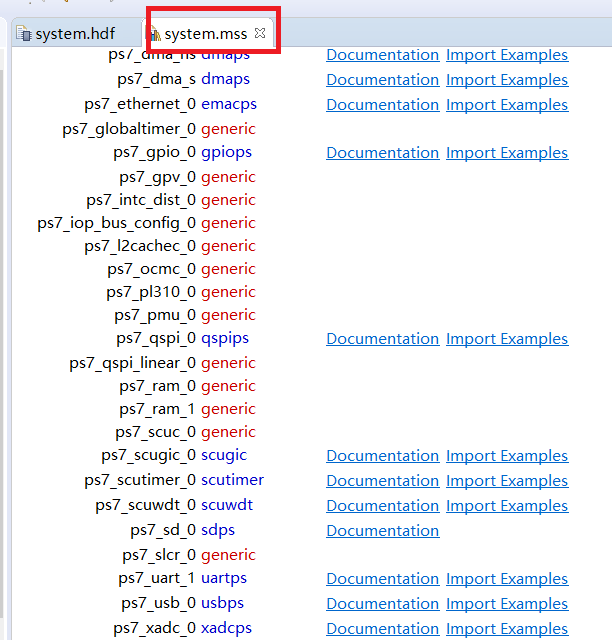

7、雙擊“system.mss”,還可以看到有些PS外設還提供了例程,這是用來了解學習這些外設的第一手資料。驅動文檔說明可以在 Documentation 中找到。通過 Import Examples 引入官方例子,加快學習。

8、連接JTAG線到開發(fā)板、UART的USB線到PC

9、打開串口終端調試工具,串口根據(jù)電腦的COM口設置,波特率設置為115200

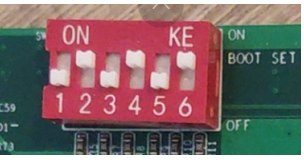

10、將開發(fā)板的啟動模式設置到JTAG模式

開發(fā)板設置撥碼為【010101(1~6 JTAG模式)】、【100101(1~6 QSPI模式)】、【101001(1~6 SD卡模式】

11、給開發(fā)板上電,準備運行程序

1、修改helloword.c,將printf打印修改為printf("hello ZYNQ7020,Author:liushuhe 2020.11.26 ");

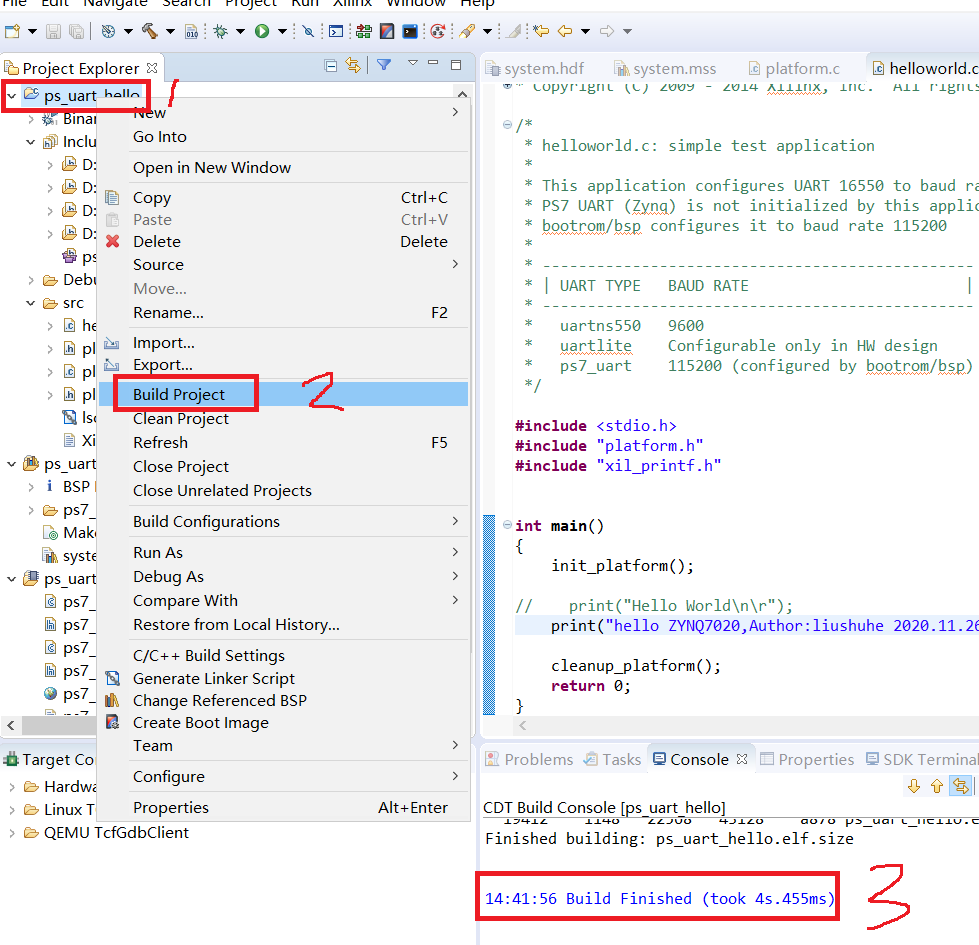

2、編譯代碼,右鍵單擊ps_uart_hello,在彈出的列表選擇Build Project,編譯完成可以看看沒有報錯

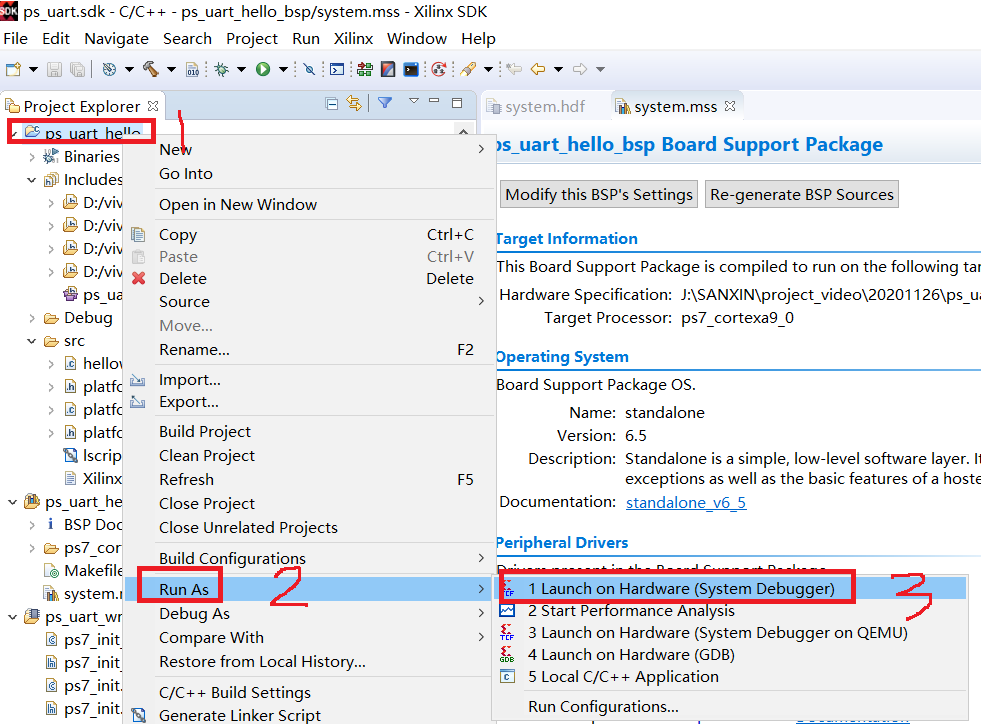

12、選擇“ps_uart_hello”,右鍵“Run as”,選擇第一個“Launch on Hardware(SystemDebuger)”,使用系統(tǒng)調試,直接運行程序。

13、可以看到串口沒有任何輸出

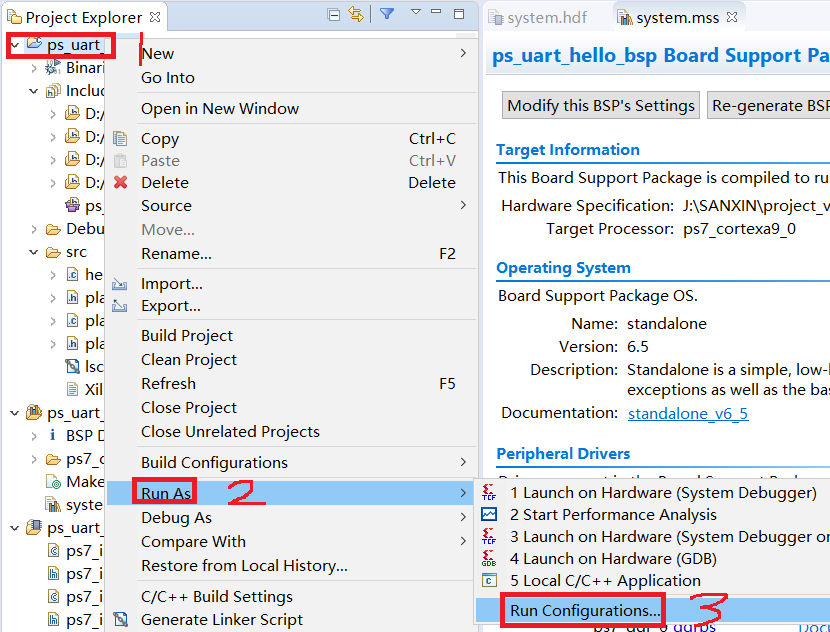

14、為了保證系統(tǒng)的可靠調試,需要添加一個配置,右鍵“Run As -> Run Configuration...”

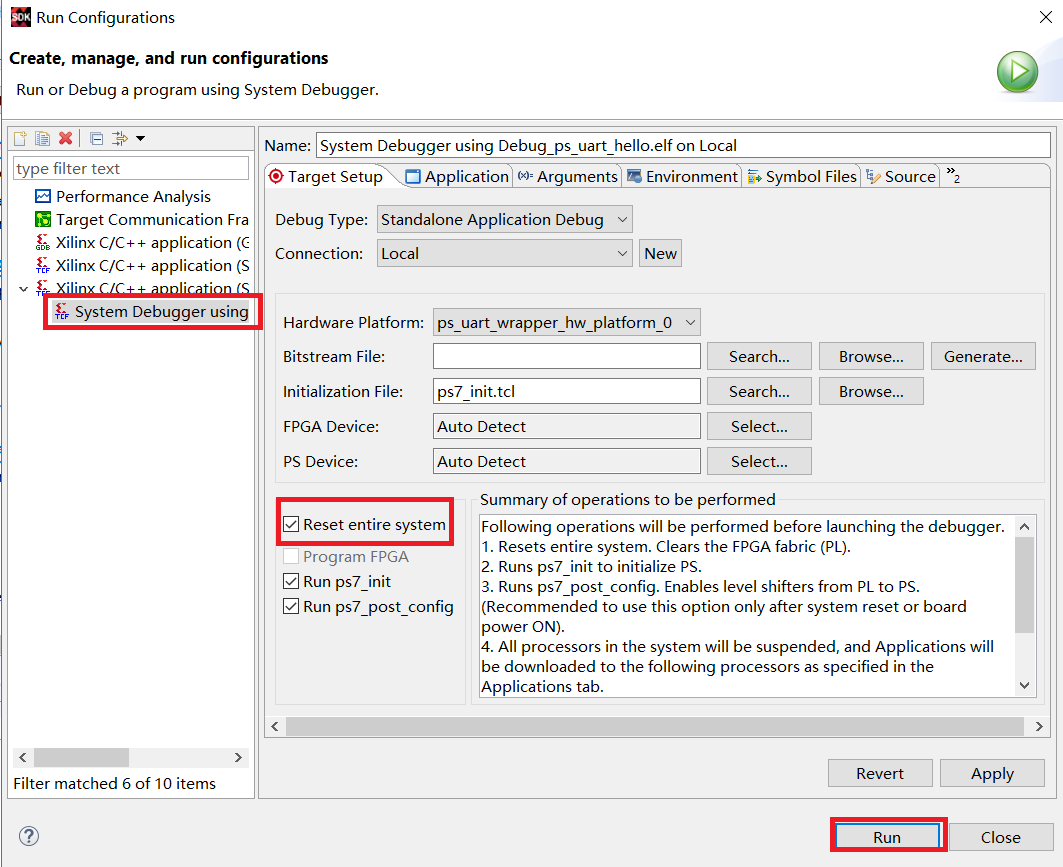

15、選擇“Reset entire system”復位整個系統(tǒng),如果系統(tǒng)中還有PL設計,還必須選擇“ProgramFPGA”,再次點擊“Run”

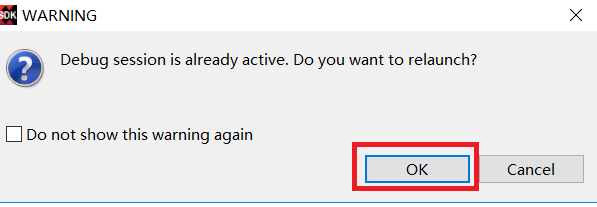

16、點擊“OK”,確認重新運行

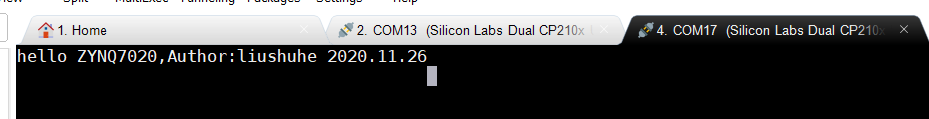

17、這次就可以看到熟悉《hello ZYNQ7020,Author:liushuhe 2020.11.26》顯示出來了

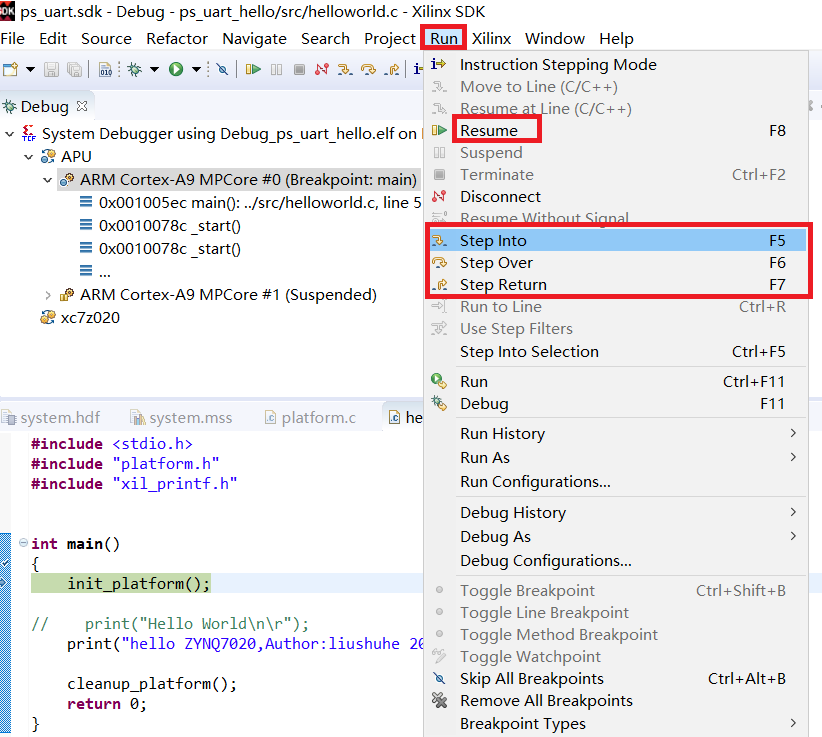

三、Debug調試

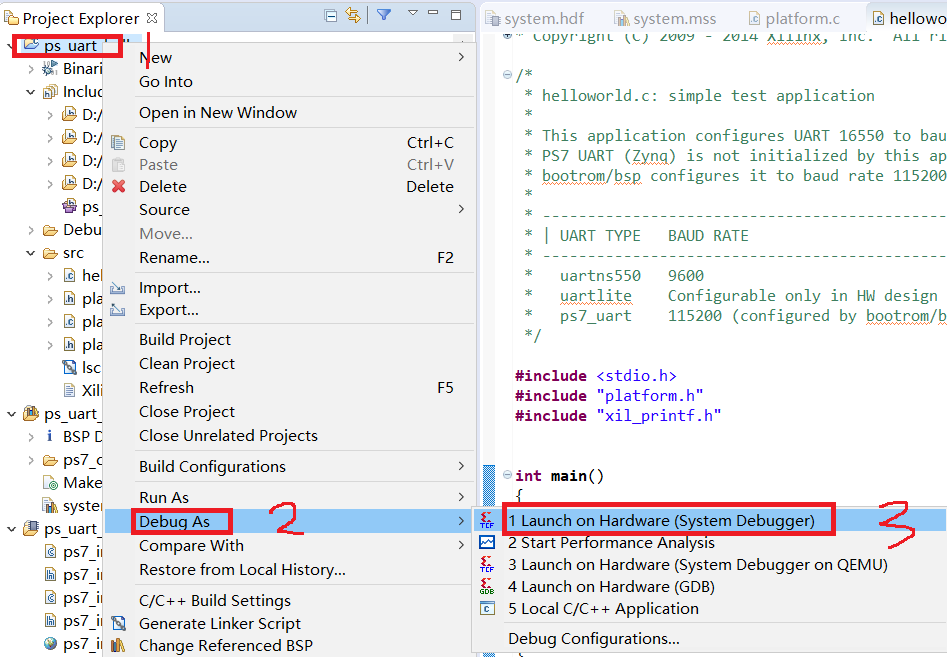

1、除了“Run As”,還可以“Debug As”,這樣可以設置斷點,單步運行

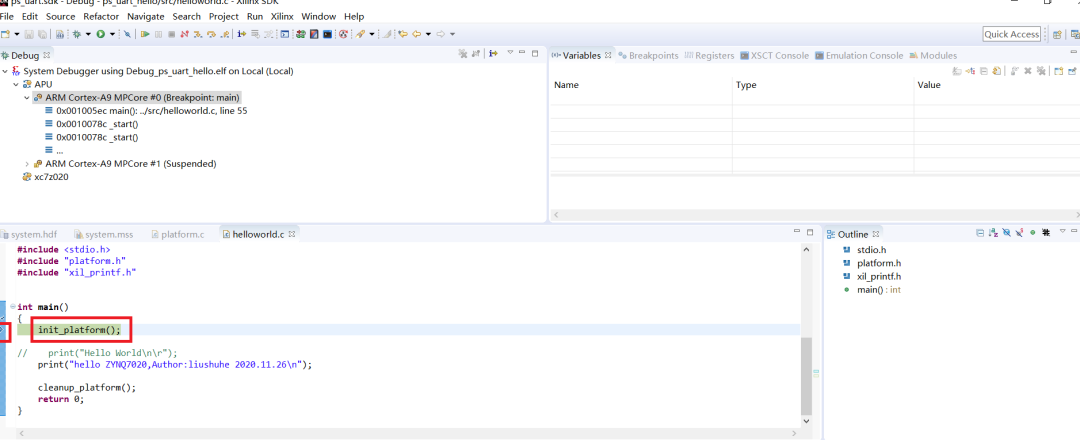

2、進入Debug模式 ,程序會自動運行到main函數(shù)處

3、和其他開發(fā)工具一樣,我們也可以逐步運行、設置斷點

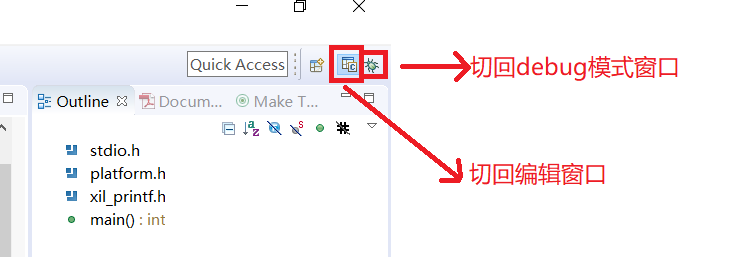

4、窗口右上角,有2個按鈕可以方便我們在debug和編輯模式之間進行切換

四、到此,關于ZYNQ7020 的PS端基本開發(fā)流程,全部跑通,關于PS-PL的聯(lián)合實驗,待我另寫一篇。

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19159瀏覽量

229112 -

FPGA

+關注

關注

1626文章

21665瀏覽量

601802 -

Zynq

+關注

關注

9文章

608瀏覽量

47124

原文標題:學員筆記精選 | ZYNQ7000系列之《PS端 》串口打印

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

ZYNQ7000系列 PS、PL、AXI 、啟動流程基本概念

vivado zynq實現(xiàn)錯誤

zynq7020板子+ad采集+dma傳輸問題?

zynq 7020 PS和zynq PL是如何通話的?

基于Zynq的嵌入式開發(fā)流程

分享!基于Zynq-7010/7020的多路千兆網(wǎng)口實現(xiàn)方案

實現(xiàn)上位機與zynq7020開發(fā)板通信的方法

AD9681是否可被zynq-7020的pl端驅動?

Zynq-7020千兆網(wǎng)口的3種擴展方案

基于zynq7020器件來搭建Linux系統(tǒng)

ZYNQ7020的PS端的基本開發(fā)流程

ZYNQ7020的PS端的基本開發(fā)流程

評論