隨著信號的沿變化速度越來越快,今天的高速數字電路板設計者所遇到的問題在幾年前看來是不可想象的。對于小于1納秒的信號沿變化,PCB板上電源層與地層間的電壓在電路板的各處都不盡相同,從而影響到IC芯片的供電,導致芯片的邏輯錯誤。為了保證高速器件的正確動作,設計者應該消除這種電壓的波動,保持低阻抗的電源分配路徑。

為此,你需要在電路板上增加退耦電容來將高速信號在電源層和地層上產生的噪聲降至最低。你必須知道要用多少個電容,每一個電容的容值應該是多大,并且它們放在電路板上什么位置最為合適。一方面你可能需要很多電容,而另一方面電路板上的空間是有限而寶貴的,這些細節上的考慮可能決定設計的成敗。

反復試驗的設計方法既耗時又昂貴,結果往往導致過約束的設計從而增加不必要的制造成本。使用軟件工具來仿真、優化電路板設計和電路板資源的使用情況,對于要反復測試各種電路板配置方案的設計來說是一種更為實際的方法。本文以一個xDSM(密集副載波多路復用)電路板的設計為例說明此過程,該設計用于光纖 /寬帶無線網絡。軟件仿真工具使用Ansoft的SIwave,SIwave基于混合全波有限元技術,可以直接從layout工具Cadence Allegro, Mentor Graphics BoardStation, Synopsys Encore和 Zuken CR-5000 Board Designer導入電路板設計。圖1是SIwave中該設計的PCB版圖。由于PCB的結構是平面的,SIwave可以有效的進行全面的分析,其分析輸出包括電路板的諧振、阻抗、選定網絡的S參數和電路的等效Spice模型。 ?

?

圖1, SIwave中xDSM電路板的PCB版圖,左邊是兩個高速總線,右邊是三個Xilinx的FPGA。

xDSM電路板的尺寸,也就是電源層和地層的尺寸是11×7.2 英寸(28×18.3 厘米)。電源層和地層都是1.4mil厚的銅箔,中間被23.98mil厚的襯底隔開。

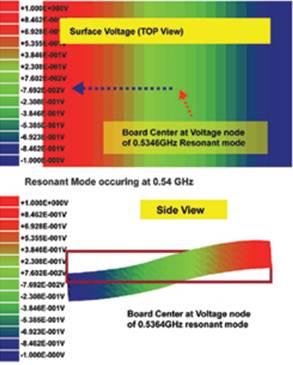

為了理解對電路板的設計,首先考慮xDSM電路板的裸板(未安裝器件)特性。根據電路板上高速信號的上升時間,你需要了解電路板在頻域直到2GHz范圍內的特性。圖2所示為一個正弦信號激勵電路板諧振于0.54GHz時的電壓分布情況。同樣,電路板也會諧振于0.81GHz和0.97GHz以及更高的頻率。為了更好地理解,你也可以在這些頻率的諧振模式下仿真電源層與地層間電壓的分布情況。

圖2所示在0.54GHz的諧振模式下,電路板的中心處電源層和地層的電壓差變化為零。對于一些更高頻率的諧振模式,情況也是如此。但并非在所有的諧振模式下都是如此,例如在1.07GHz、 1.64GHz和1.96 GHz的高階諧振模式下,電路板中心處的電壓差變化是不為零的。

圖2, 正弦信號激勵電路板諧振于0.54GHz時的電壓分布情況。

找到零壓差變化點有助于我們將需要在短時間內產生大量電流變化的器件放置于此。例如,如果要將一塊Xinlix的FPGA芯片放在電路板上,該芯片會在 0.2納秒內產生2A的輸入電流變化。如此短時間內的大電流變化將帶來電路板的電源完整性問題,會使電路板產生各種模式的諧振,導致電源層和地層電壓的不均勻。然而,電路板中心處在某些諧振模式下具有零壓差變化的特性,因此將FPGA芯片放置于此可以避免電路板產生這些低頻的諧振模式。FPGA芯片不能激發這些低頻諧振模式,是由于從電路板的中心處將無法耦合至這些諧振模式。

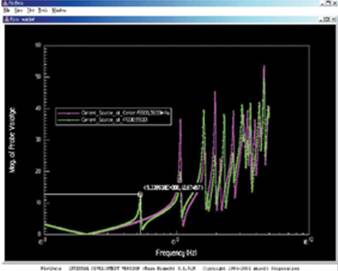

圖3中的紫色曲線顯示的是當位于電路板中心處的芯片從電源平面吸入電流時引起的諧振。事實上,峰值出現在高階的諧振頻率1.07GHz、1.64GHz和1.96GHz上,而不是低階的諧振頻率0.54GHz、0.81GHz和0.97GHz上,這正如我們所料。 ?

?

圖3, 紫色曲線顯示的是當位于電路板中心處的芯片從電源平面吸入電流時引起的諧振;綠色曲線表示當將芯片放置偏移中心位置時的響應。

盡管器件的布局與放置的位置有助于減小電源完整性的問題,但它們并不能解決所有的問題。首先,你不能將所有的關鍵器件放在電路板的中心。通常情況下,器件放置的靈活性是有限的。其次,在任何給定的位置總有一些諧振模式會被激發。例如,圖3中綠色曲線表示當你將芯片放置在沿某一坐標軸偏移中心位置時, 0.54GHz的諧振模式將被激發。成功的設計電路板的PDS(電源分配系統)的關鍵在于在合適的位置增加退耦電容,以保證電源的完整性和在足夠寬的頻率范圍內保證地彈噪聲足夠小。

退耦電容

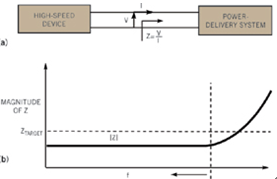

設想FPGA在0.2納秒的上升沿吸入2A的電流,此時電源電壓會暫時降低(壓降),而地平面電壓會暫時被拉高(地彈)。其變化幅度取決于電路板的阻抗和芯片偏置管腳處的用于提供電流的退耦電容(圖4a)。

由于電流的瞬變值為2A,電壓的瞬變值由V=Z×I決定,Z是從芯片端看出的阻抗,因此,為了避免電壓的尖峰波動,在從直流到信號帶寬的頻率范圍內,Z值必須低于某一門限值。(圖4b) ?

?

圖4,其變化幅度取決于電路板的阻抗和芯片偏置管腳處的用于提供電流的退耦電容;為了避免電壓的尖峰波動,在從直流到信號帶寬的頻率范圍內,Z值必須低于某一門限值。圖中虛線部分即為PDS阻抗應該滿足的目標區域。

在該設計中,為了保持電源完整性,電源—地的電壓波動必須保持在標準值3.3V的5%以內。因此噪聲不能大于0.05×3.3V=165 mV。可以據此按照歐姆定律計算出PDS的最大阻抗165mV/2A=82.5mΩ,圖4中虛線部分即為PDS阻抗應該滿足的目標區域。

對于最低頻率,通常是1kHz或者更低的頻率——電源滿足阻抗特性的要求,電源和地層的結構通常不會破壞阻抗特性,因為它們呈現低電阻與電感特性。而當頻率高于1kHz時,電流通路的互感大到足以使電壓超過限定值,根據: ?

?

對于更高的頻率,退耦電容作為電源層與地層之間的低阻抗連接是必要的。需要滿足PDS阻抗要求的信號帶寬可由下式估計: ?

?

在該設計中,其帶寬為1.75GHz。為了達到這么寬的帶寬,通常需要在MHz信號區域放置很多高頻瓷片電容,在kHz信號區域放置體積較大的電解電容。這些電容矩陣與其它器件共同占用寶貴的電路板空間。在反復試驗的設計方法中,物理原型是不可缺少的,而虛擬原型技術使設計者可以在不需要物理原型的基礎上解決這個問題。

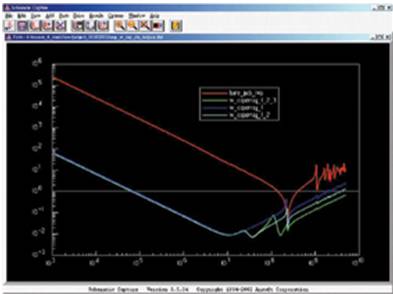

為PCB板設計PDS,例如此例中的xDSM板,使用SIwave可以在IC芯片處放置一個端口,計算電路板在適當帶寬內的輸入阻抗。圖5中紅色曲線顯示的是電路板上無電容時的阻抗。阻抗軸與頻率軸都取對數坐標。仿真顯示了電路板本身電容的影響而忽略了經過電源的低感應電流回路。從圖中可以看出,阻抗隨著頻率的減少而增加,但由于經過電源的回路也有低阻抗,因此這種關系并不是嚴格的。 ?

?

圖5,紅色曲線顯示的是電路板上無電容時的阻抗;深藍色曲線是經過重新設計后的阻抗特性;淺藍色曲線是又增加10nF電容矩陣后的阻抗曲線;綠色曲線表示再次增加1nF電容矩陣后的結果。

根據Z=1/(j?C),紅色曲線中的直線部分表明電路板本身的電容為74nF。為了使阻抗在1MHz處低于目標阻抗82.5mΩ,電容值至少應為 2μF——幾乎是電路板本身電容的30倍。為此首先需要增加22個0.1μF的電容矩陣。圖中深藍色曲線是經過重新設計后的阻抗特性。在大多數的頻率范圍內,設計滿足了阻抗特性的要求。但在帶寬的高端,電容的ESL(等效串聯電感)、ESR(等效串聯電阻)以及由電容間距帶來的附加電感使阻抗曲線沒有達到阻抗特性要求。

由于更小的電容具有更小的ESL和ESR值,因此增加旁路有助于提高其高頻特性。圖5中的淺藍色曲線是又增加10nF電容矩陣后的阻抗曲線。綠色曲線表示再次增加1nF電容矩陣后的結果。每一級別電容矩陣的增加都提高了阻抗特性,但結果仍然剛剛滿足阻抗特性的要求。

在設計的這個階段,設計者可以增加電磁仿真與電路仿真一起來完成設計。這種方法使設計者可以精確地為低端的阻抗建模,包括電源的負載效應。它也可以直接仿真電源管腳上的噪聲從而直接驗證電源層噪聲,避免對電源層阻抗的過多分析導致的不必要的設計開銷。

首先應在選定的位置添加輸入和輸出端口。上文已經在一個IC芯片處添加了端口,接著應該在電源輸入端添加一個端口,同時在其它兩塊芯片的安裝位置添加兩個端口。然后在SIwave中你可以進行寬頻掃描,在整個帶寬內獲得4×4的S參數散射矩陣。接下來可以使用Full-Wave Spice產生與Spice兼容的電路文件以便在電路仿真環境中進一步分析。

在產生的電路文件中,PCB板在電路的中心位置。電路文件還包括 FPGA的模型——伴有一個電流探針和一個差分電壓探針的電流源。Full-wave Spice創建的Spice電路還包括上文提到的三個電容矩陣。如果在IC處再增加第四個電容矩陣將進一步減小高端阻抗。電路還包括一個直流電源,電源伴有少量容值從1nF到100μF的退耦電容。另外還包括其它兩個IC芯片的模型,周圍伴有少量100nF的電容矩陣。 ?

?

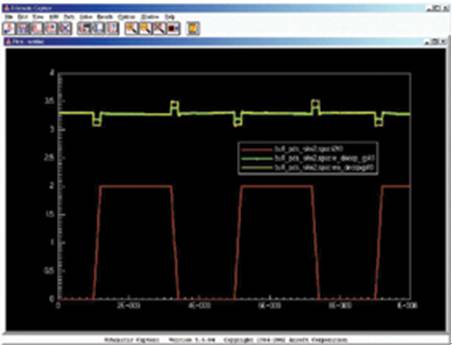

圖6,藍色和綠色曲線分別表示在沒有添加和添加最后一組電容矩陣后IC芯片的電源完整性曲線;紅色曲線代表芯片輸入電流的突變。

圖6顯示了FPGA的電源電壓的噪聲仿真結果。紅色曲線代表芯片輸入電流的突變——在0.2納秒內電流由0A變化到2A。藍色曲線表示沒有添加最后一組電容矩陣時IC芯片的電壓曲線。與3.3V相比,電壓的波動已經很小了,但還是超過了5%的規范要求。綠色曲線表示添加了第四組電容矩陣后電壓的波動曲線,最終的設計滿足了電源噪聲小于165mV的規范要求。

可以用同樣的方法分析電路板上其它的芯片,保證他們不受電源壓降和地彈的影響。在本例中另外兩芯片分別吸收100mA和50mA電流,相對來說,它們對噪聲的貢獻是很小的。

高速電路的PCB板級設計是十分具有挑戰性的。為了保證電路的正確工作,需要精心設計電路的PDS,包括在電路板上添加數以百計的退耦電容,并且根據需要選擇合適的電容值及其位置。采用對虛擬原型進行仿真的方法替代反復試驗的設計方法來優化電路板的電源完整性設計,可以有效縮短設計周期并且節約設計成本。

-

電路板

+關注

關注

140文章

4810瀏覽量

96085 -

軟件

+關注

關注

69文章

4570瀏覽量

86693 -

無線網絡

+關注

關注

6文章

1410瀏覽量

65708

原文標題:電源完整性與地彈噪聲的高速PCB仿真

文章出處:【微信號:Elec-sunday,微信公眾號:電子芯期天】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

優化電路板的電源完整性設計高速PCB仿真

電路板為什么是綠色的_電路板上的元件介紹圖

雙面電路板如何拆_雙面電路板元件拆焊

電路板抄板是什么意思

電路板抄板是什么意思

什么是電路板,電路板的基礎知識簡介

xDSM電路板設計的電源完整性與地彈噪聲資料下載

什么是電路板抄板打樣? 電路板抄板打樣服務流程

剛性電路板的特點及與柔性電路板的區別

xDSM電路板的設計

xDSM電路板的設計

評論