2019 年是極紫外 (EUV) 光刻技術的重要里程碑。當年,EUV圖案化技術首次用于7nm技術一代邏輯芯片的量產。插入以圖案化芯片后端 (BEOL) 的最關鍵層,它可以打印間距為 36-40nm 的金屬線。

憑借 13.5nm 的極短波長,EUV 光刻已被引入以取代 193nm(浸入式)光刻——這是由瑞利方程決定的分辨率轉換。根據這個方程式,可以通過在晶圓曝光期間使用波長較小的光來提高光刻工具的分辨率,從而提高其打印具有特定半間距或臨界尺寸 (CD) 的特征的能力。此外,193nm 復雜且昂貴的多重圖案化要求——包括將芯片圖案分割成兩個或更多更簡單的掩模——可以再次移回單一圖案化 EUV。

在開發方面,研究人員一直在不斷嘗試進一步推動當今最先進的 EUV 全場掃描儀,即 ASML NXE:3400B 的單次打印能力。例如,今年早些時候,imec 和 ASML 能夠展示 28nm 間距的單次曝光圖案化線/空間準備就緒,對應于 5nm 邏輯技術節點的關鍵 BEOL 金屬層。這使當前的掃描儀接近其大批量制造的分辨率極限,約為 13 納米(26 納米間距)。隨著邏輯的發展,存儲器制造商越來越多地考慮使用 EUV 光刻技術來滿足未來存儲器的高密度要求——例如用于關鍵 DRAM 結構的圖案化。

與此同時,正在探索多重圖案 EUV 光刻選項,以將 EUV 推進到下一個節點。雖然這些“技巧”提供了更輕松的間距,但它們也有一個缺點:處理步驟數量增加,增加了圖案化步驟的成本、復雜性和處理時間。

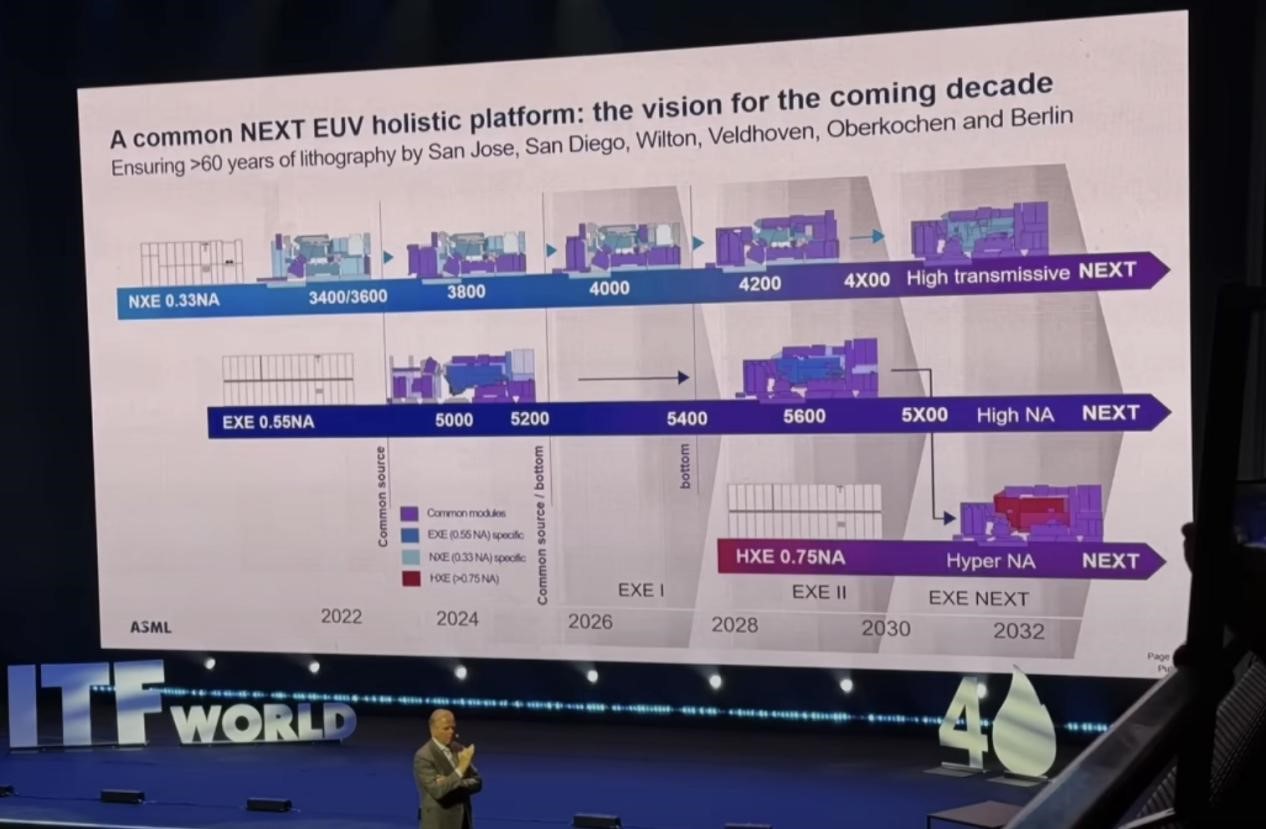

2023 年將標志著 EUV 光刻技術發展的新里程碑。屆時,預計第一代新一代 EUV 光刻工具將進入現場:高 NA EUV 光刻掃描儀——預計以更少的圖案化步驟打印 2nm(及以上)邏輯芯片的最關鍵特征。瑞利方程再次證明了向高 NA 光刻的過渡,它為提高分辨率提供了第二個旋鈕:增加投影鏡頭的數值孔徑 (NA)。NA 控制用于形成圖像的光量(更準確地說是衍射級數),從而控制圖像的質量。

之前已經應用過向更高 NA 成像設備的過渡,請記住從 193nm 干法到 193nm 浸沒式光刻的轉變。當時,用水代替透鏡和晶圓之間的空氣的光學技巧使 NA 增加了 45%。在 EUV 的情況下,ASML 將通過重新設計光刻系統中的光學器件,從當前的 0.33 NA 變為 0.55NA(即 NA 增加 67%)。0.55NA EUV 光刻有望最終實現 8nm 分辨率,對應于一次曝光中 16nm 間距的印刷線/間距。

雄心勃勃的時間表……

0.55NA EUV 光刻技術將把圖案化推向比當前 0.33NA EUV 光刻系統更小的特征。但前進的道路是雄心勃勃的。EUV 光刻系統的開發可以追溯到 2000 年代,從安裝第一臺預生產的 EUV 掃描儀到最近在大批量制造中引入 EUV 光刻,有十年的時間跨度。對于高 NA,目標是將時間框架壓縮到僅 3 年,預計 2023 年將推出第一個原型(EXE:5000)。

圖 1:ASML 的 EXE:5000 高 NA EUV 光刻掃描儀渲染圖(由 ASML 提供)

在第一個高數值孔徑工具問世之前,專用實驗室設備和當前一代的極紫外光刻工具和材料正被推向極限,以盡可能地準備和降低新的高數值孔徑 EUV 光刻技術的風險。

同時,imec 正在與 ASML 合作開設一個聯合高 NA 實驗室,將在其中建造高 NA 系統,連接到涂層和開發軌道,并配備計量設備。他們將共同為行業創建生態系統以滿足工藝要求,并建立與高NA工具開發相伴的基礎設施——包括變形成像、新掩模技術、計量、抗蝕劑篩選和薄膜圖案化材料開發等. 這些發展將在下面更詳細地討論。此外,客戶將可以使用高 NA 實驗室來開發他們的私有高 NA 用例。

解決過程和計量需求:共同努力

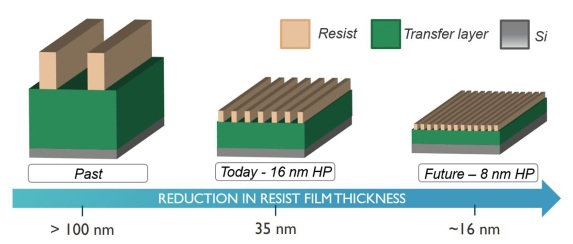

隨著高 NA EUV 光刻技術的出現,抗蝕劑更薄的趨勢將繼續存在,其最終目標是印刷 16nm 間距的線/間距,對應于寬度小至 8nm 的印刷線。這需要厚度小于 20nm 的抗蝕劑薄膜以保持 2:1 的理想縱橫比(定義為線的高度和寬度之間的比率)。使用較厚的抗蝕劑,縱橫比會增加,隨之而來的是線條崩塌的風險。高數值孔徑 EUV 光刻技術帶來了使用更薄抗蝕劑薄膜的第二個原因。根據第二個瑞利方程,焦深(DOF)——即(航空)圖像焦點所在的抗蝕劑高度——按數值孔徑的平方減小。模擬預測,相對于當前的 0.33NA 光刻,DOF 會有效降低 2-3 倍。

降低的抗蝕劑厚度要求為高 NA EUV 工藝帶來了新的需求,包括圖案轉移。篩選(新)抗蝕劑、優化硬掩模和蝕刻工藝的選擇性,以及評估超薄抗蝕劑時的圖案化限制是imec與其材料供應商合作的主要任務。

但向更小特征和更薄抗蝕劑薄膜的過渡也對計量提出了挑戰。比以往任何時候都強烈需要同時解決圖案和計量機會——一個服務于另一個的需求。例如,當抗蝕劑變得超薄時,印刷線內的材料量會變得非常小,以至于很難用當前使用的計量工具“看到”。例如,對于廣泛使用的 CD-SEM,使用更薄的抗蝕劑會導致圖像對比度大大降低。最近的實驗表明,底層的類型(即光刻膠膜下面的層)可以對 SEM 成像對比度產生積極影響。但是使用不同的底層來改進計量將反過來影響圖案轉移,需要優化蝕刻工藝。為了繼續優化模式轉移,

圖 2:抗蝕劑膜厚度減少的演變(HP = 半間距)。

下面,我們將介紹最近在圖案化和計量方面的一些見解。

評估模式轉移的限制

作為對第一個高 NA EUV 原型制作系統的預期,imec 使用目前最先進的 0.33NA EUV 光刻系統 NXE:3400B 來預測更薄的抗蝕劑的性能——包括線路/空間和接觸孔。早些時候,imec 和 ASML 能夠使用這款 NXE:3400B 掃描儀打印最小間距(即 24nm 間距線/間距和 28nm 間距接觸孔),從而實現高 NA EUV 光刻掃描儀所需的早期材料開發。

例如,通過使用該工具,該團隊表明,線邊緣和線寬粗糙度 (LER/LWR)——在圖案化線/空間的最關鍵參數中——在使用更薄的抗蝕劑薄膜時往往會增加。在這些實驗中,使用了化學放大抗蝕劑 (CAR),這是一種依賴于當 EUV 光子撞擊表面時在抗蝕劑內形成的電子的化學放大的抗蝕劑。自 1990 年代初以來,這些 CAR 已在工業中大量使用,并已逐漸優化以獲得更好的抗蝕劑性能。但對于高數值孔徑光刻,該行業可能需要 CAR 以外的抗蝕劑,具有更好的分辨率。因此,我們看到了新型光刻膠材料的出現,例如金屬氧化物抗蝕劑 (MOR)。我們的第一個實驗似乎表明這些 MOR 對于更小的特征和更薄的抗蝕劑確實具有更好的圖案轉移能力。Imec 與多家材料供應商合作開發這些概念并評估諸如污染風險和工藝集成挑戰等關鍵問題。

圖 3:觀察到縮小 EUV 抗蝕劑膜厚度會增加線寬粗糙度 (LWR)。

高 NA EUVL:計量的機會

如前所述,計量學的第一個主要挑戰是需要應對目前使用的 CD-SEM 工具降低的圖像對比度。Imec 看到了兩種方法來解決這個問題,并繼續測量用更薄的抗蝕劑印刷的非常小的線條。第一種方法是調整工具的設置。使用 CD-SEM 工具的某些旋鈕(例如掃描速率)結果證明會對成像對比度產生積極影響——即使在薄膜厚度低至 15nm 時也能看到圖案。第二種方法是與imec 的計量供應商密切合作,探索替代計量技術。在分辨率方面非常有前途的是例如低壓 SEM、氦離子顯微鏡、散射儀……

圖 4:減少抗蝕劑膜厚度(從 30nm 到 10nm)(上)對 CD SEM 圖像對比度產生負面影響,但(中)可以通過使用 CD-SEM 計量旋鈕或(下)使用不同的底層來改善。

除了例如 10nm 寬度的線之外,圖案內還有更小的特征需要成像。隨著縮放的繼續,測量 LER 和覆蓋性能(即一層與下一層的對齊程度)等參數變得更加困難——需要遠低于 10nm 的圖像分辨率。然后是缺陷,更具體地說,隨機打印故障的出現:隨機的、非重復的、孤立的缺陷,例如微橋、局部斷線和缺失或合并的觸點。它們被認為是由能量和波長之間的基本關系產生的。隨著波長越來越短——EUV 光刻在 13.5nm 下運行——來自光源的能量分布在更少的光子上。因此,只有幾個光子可以創建一個圖案。

具有進一步提高的分辨率和減小的抗蝕劑厚度的高 NA EUV 光刻技術的出現將進一步推動這一發展。Imec 一直在開發方法來系統地量化 EUV 材料中的缺陷水平,并了解導致故障的許多因素。關鍵是傳統上依賴光學技術的晶圓檢測策略的發展和改進。最近,基于電子束的檢測越來越受到關注。盡管它在發現小缺陷方面看起來很有希望,但它也有一個主要缺點:檢查整個晶圓所需的時間急劇增加——需要解決方案來提高工具生產率和吞吐量。

此外,越來越多地設置金屬化圖案的電氣測試,以尋找與通過光學和電子束檢測技術獲得的數據的相關性。這允許增加對隨機模式失敗的學習,并獲得更多關于它們影響產量的方式的見解。通過這種方式,使用掃描電子顯微鏡、寬帶等離子光學和電子束技術獲得的缺陷檢測數據已經可以成功地與從電氣測量獲得的數據相關聯。電氣測試是在允許測量電開路(以及因此抗蝕劑中的橋)的大面積釕金屬化蛇形結構以及允許測量電學的金屬化叉叉和尖端對尖端結構上進行的。短褲(因此抵抗中的關鍵斷裂)。

掩模技術:充分利用高 NA EUV 光刻技術的另一個關鍵因素

光掩模是芯片制造的重要組成部分,因為它保存了用于最終設備的設計布局信息。理想情況下,該信息包含在掩模上的暗(即吸收)和亮(即反射)區域中。現在正在打印越來越小的特征,與理想掩模的偏差越來越多地影響最終的晶圓圖案。因此,需要解決口罩的具體挑戰。其中包括減少掩模 3D 效果、增強對掩模壽命及其對打印隨機故障的貢獻的理解。最重要的是,在高 NA EUVL 光學系統中引入畸變會給掩模行業帶來額外的復雜性。在這一切中,imec 團隊扮演著重要的角色。通過與 ASML 及其材料供應商的密切合作,imec 致力于設計優化和認證用于高 NA EUV 光刻的光掩模。下文將更詳細地描述這項工作。

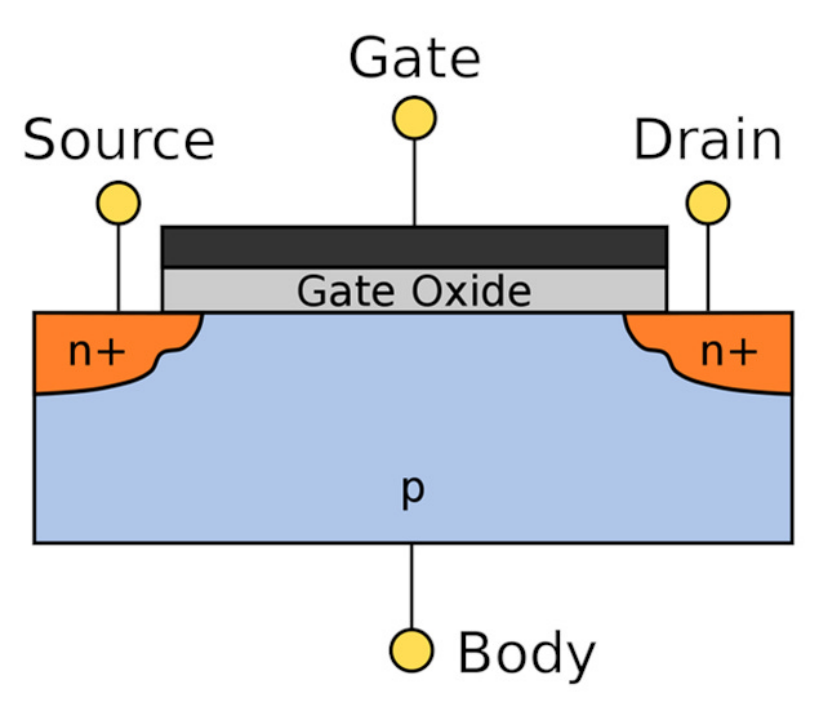

用于減少掩模 3D 效果的新型吸收材料

今天的 EUV 掩模由約 300nm 厚的反射多層堆疊組成,由 40 到 50 層交替的硅 (Si) 和鉬 (Mo) 層組成,覆蓋著一層薄的釕層。在這個堆棧上,由鉭硼硝酸鹽 (TaBN) 制成的吸收器帶有圖案。當 Mo 和 Si 的多層反射入射光時,吸收器阻擋反射,這種組合定義了晶片上的特征。

圖 5:EUV 光掩模的卡通橫截面

當前的基于 Ta 的吸收器的厚度通常約為 60-70nm,旨在吸收足夠量的光。與光的 13.5nm 曝光波長相比,該厚度較大。因此,以特定入射角(在傳統 EUV 光刻中以 6° 為中心)照射掩模并從多層反射的光對“厚”掩模的 3D 形貌敏感,例如經歷多層和吸收體誘導相變形。這會扭曲空中圖像——最終轉移到光刻膠中的光圖案——并降低其圖像對比度。這些所謂的掩模 3D 效果還伴隨著更多的與特征相關的放置變化和對晶圓的最佳聚焦。這對已經受到 DOF 預算減少的高 NA EUV 光刻提出了額外的挑戰。

最初,應用源照明和掩模設計的創新來補償掩模 3D 效果。近年來,注意力正轉向改進掩模材料作為控制晶圓上掩模 3D 效應的參數,從而有助于提高高 NA DOF。

這推動了 imec 研究探索新的吸收材料,這些材料要么具有不同的 EUV 折射率(低 n 材料,如 RuTa 或 PtMo,允許衰減相移),要么具有高 EUV 消光系數(高 k 材料,如 PtTe 或Ni具有高吸收能力)。對于每種材料類型,都需要優化厚度以實現最佳成像權衡。Imec 正在進行材料篩選,以尋找這些材料中最有前途的材料。基于這些材料的新掩模架構預計將在今年年底前在 imec 的當前 EUV 掃描儀上進行測試。

圖 6:EUV 掩模吸收材料空間與參考 TaBN

變形面具來了

高數值孔徑 EUV 光刻技術對掃描儀內的光學器件進行了重大重新設計,允許具有更大入射角的光照射到晶圓上,從而使系統具有更高的分辨率。在相同的掃描儀放大倍率下,這會帶來一個缺點。具有更高入射角的光也會照射到掩模上,如果不采取行動,這將大大惡化 3D 掩模效果。

克服這些額外陰影效應的一種方法是將掩模放大率從其歷史的 4 倍增加到 8 倍,并結合使用更大的掩模空白。但放棄最初的 6 英寸 x 6 英寸面罩尺寸,同時保持較高的面罩質量將極大地影響面罩行業。為了盡量減少這種影響,ASML 和蔡司推出了變形鏡頭,一種在 x 和 y 方向(分別為 4x 和 8y(y 是掃描方向))具有不同放大倍率的鏡頭。保留了 6 英寸面罩,但其設計向一個方向拉伸。增加的放大倍率(在一個方向上)將圖像場大小(即,在一個步驟中曝光的晶片部分)縮小到一半,因此掃描儀最終可能僅在設備的一部分上打印特征。對于具有較大裸片尺寸的芯片尤其如此,這對如何設計這些芯片施加了限制。對于這些芯片,芯片制造商必須采用一種稱為縫合的技術。圖案的一部分用一個蒙版曝光,下一部分用第二個蒙版曝光,兩個蒙版縫合在一起。Imec 研究改進縫合的方法,例如通過減少兩個面罩之間固有的所謂過渡區。在硬件方面,ASML 致力于加速掩模和晶圓階段,以彌補半場成像造成的生產力損失。并將兩個面具縫合在一起。Imec 研究改進縫合的方法,例如通過減少兩個面罩之間固有的所謂過渡區。在硬件方面,ASML 致力于加速掩模和晶圓階段,以彌補半場成像造成的生產力損失。并將兩個面具縫合在一起。Imec 研究改進縫合的方法,例如通過減少兩個面罩之間固有的所謂過渡區。在硬件方面,ASML 致力于加速掩模和晶圓階段,以彌補半場成像造成的生產力損失。

圖 7:掩模示意圖,以及在 0.55NA 掃描儀上打印期間掩模和晶圓的主要方向(由 ASML 提供)

薄膜開發

在光刻技術中,光掩模通常與薄膜一起被提及——薄膜是用于在大批量半導體制造過程中保護掩模免受污染的薄膜。它安裝在光掩模表面上方幾毫米處,因此如果顆粒落在薄膜上,它們將離焦太遠而無法打印。然而,開發 EUV 薄膜并不簡單。所有 EUV 掃描儀都面臨的一個主要挑戰是使薄膜吸收盡可能少,以保持 EUV 光刻的吞吐量和經濟性。此外,薄膜必須能夠承受未來光刻工具不斷增加的 EUV 功率,包括高 NA EUV 光刻工具——8 倍放大倍率帶來了薄膜和掩模級別功率密度降低的好處。艾美克,與合作伙伴合作,開發了一種創新的基于 CNT 的薄膜解決方案,該解決方案有可能在超過 600 瓦的掃描儀功率下存活。CNT 薄膜的可行性已通過在 imec 的 EUV NXE:3300 掃描儀上的使用得到成功證明。該團隊現在正在努力延長使用壽命,以實現適用于下一代 EUV 光刻工具(包括高 NA)的高生產率薄膜解決方案,其光罩加速度大大提高。

圖 8:類似于 imec 的 NXE:3300B 中暴露的全尺寸 CNT 薄膜

從商品到關鍵部件……

該團隊專注于其他特定于面具的機會,例如面具生命周期的理解。掩膜在儲存時會發生碳生長,這會影響印在晶圓上的特征的關鍵尺寸。觀察到該效果取決于存儲條件,并且可以通過 EUV 曝光來逆轉。該研究揭示了盡可能控制和最小化存儲和壽命影響的重要性,以實現穩定的掩模印刷性能。另一個挑戰與掩模缺陷對隨機故障概率的貢獻增加有關。觀察到隨著掩模老化而增加的掩模多層的表面粗糙化起著至關重要的作用。這推動了替代多層“鏡面”材料的研究。此外,與以往相比,掩模上的小缺陷,例如邊緣放置錯誤或 CD 錯誤,會轉化為晶圓印刷后觀察到的錯誤。現在情況變得更糟了,因為晶圓在覆蓋、聚焦和邊緣放置誤差方面的預算已經變得非常小,這是縮放的直接后果。這促使需要大規模量化掩模對晶圓成像性能的貢獻。此外,正在研究以更精確和更小分辨率寫入掩模的其他方法,包括多光束掩模寫入,它允許不同(所謂的曲線)掩模形狀。所有這些都表明,掩模正從“簡單”的商品演變為對晶圓成像性能越來越重要的復雜組件。現在情況變得更糟了,因為晶圓在覆蓋、聚焦和邊緣放置誤差方面的預算已經變得非常小,這是縮放的直接后果。這促使需要大規模量化掩模對晶圓成像性能的貢獻。此外,正在研究以更精確和更小分辨率寫入掩模的其他方法,包括多光束掩模寫入,它允許不同(所謂的曲線)掩模形狀。所有這些都表明,掩模正從“簡單”的商品演變為對晶圓成像性能越來越重要的復雜組件。現在情況變得更糟了,因為晶圓在覆蓋、聚焦和邊緣放置誤差方面的預算已經變得非常小,這是縮放的直接后果。這促使需要大規模量化掩模對晶圓成像性能的貢獻。此外,正在研究以更精確和更小分辨率寫入掩模的其他方法,包括多光束掩模寫入,它允許不同(所謂的曲線)掩模形狀。所有這些都表明,掩模正從“簡單”的商品演變為對晶圓成像性能越來越重要的復雜組件。這促使需要大規模量化掩模對晶圓成像性能的貢獻。此外,正在研究以更精確和更小分辨率寫入掩模的其他方法,包括多光束掩模寫入,它允許不同(所謂的曲線)掩模形狀。所有這些都表明,掩模正從“簡單”的商品演變為對晶圓成像性能越來越重要的復雜組件。這促使需要大規模量化掩模對晶圓成像性能的貢獻。此外,正在研究以更精確和更小分辨率寫入掩模的其他方法,包括多光束掩模寫入,它允許不同(所謂的曲線)掩模形狀。所有這些都表明,掩模正從“簡單”的商品演變為對晶圓成像性能越來越重要的復雜組件。

AttoLab:加速高NA圖案化生態系統的發展

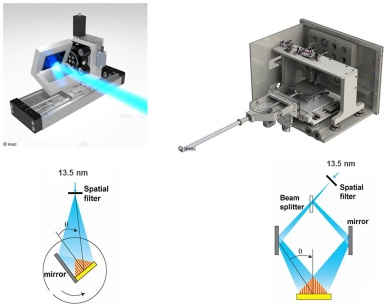

需要加快對薄光刻膠成像的學習是imec 決定投資與KMLabs 的聯合項目AttoLab 的原因之一。該實驗室使我們能夠在 ASML 的第一個 0.55NA EXE:5000 原型面世之前探索高 NA EUV 光刻條件下光刻膠成像的基本動力學。實驗室中的實驗裝置在 0.33NA EUV 光刻掃描儀已經獲得的基礎上提供了相應的見解。

在 AttoLab 中,13.5nm 的高 NA 曝光通過干涉型設置中的明亮、相干、高諧波 EUV 源進行模擬。最近,通過用于試樣實驗的基于勞埃德鏡的干涉裝置,20nm 節距線/空間首次可以在金屬氧化物光刻膠中成功地在 imec 成像。在這種布置中,從鏡子反射的光會與 13.5nm 高諧波發生源直接發射的光發生干涉,從而產生適合抗蝕劑成像的精細干涉圖案。可以通過改變干涉光束之間的角度來調整成像的抗蝕劑圖案的間距。此 Lloyd's-Mirror 設置為下一步提供了重要的學習信息:

基于干涉的 EUV 光源與 ASML 的高 NA EUV 激光器中使用的方法不同,后者將錫滴蒸發以產生 EUV 光。光子隨后從掃描儀內的幾個鏡子反彈,從掩模反射,最后撞擊晶片上的抗蝕劑。雖然 ASML 的掃描儀專為芯片的大規模生產而設計,但 AttoLab 中使用的干涉型工具永遠無法達到所需的全場吞吐量。

但是對于這些 13.5nm 飛秒包絡阿秒激光脈沖,imec 正在追求不同的目標:研究隨后在光刻膠材料中引起的 EUV 光子吸收和超快輻射過程,并了解更多關于關鍵隨機打印失敗的信息。對于這些研究,光束線與時間分辨紅外和光電子光譜等光譜技術相結合,并且正在建立相應的泵浦探針類型的實驗。光束線設計用于在幾秒鐘內在高 NA 條件下篩選各種抗蝕劑材料,并支持開發適用于高 NA EUV 光刻的優化圖案、蝕刻和計量技術。

圖 9:用于高 NA EUV 干擾試樣實驗的(左)勞埃德鏡設置示意圖(未按比例);(右)用于全 300 毫米晶圓實驗的干涉室

結論

從 0.33NA 到 0.55 高 NA EUV 光刻技術的轉變為光刻行業提供了一個重要的機會,可以在很短的時間內共同應對挑戰并為該工具的推出做好準備。imec 與 ASML 在聯合的高 NA EUV 實驗室中專注于與高 NA 掃描儀開發相關的基礎設施準備工作。為此,imec依靠并邀請所有材料和設備供應商為建立完整的高NA生態系統做出貢獻。所有這些努力的回報將是巨大的,因為 0.55NA EUV 光刻工具有望將摩爾定律推向 2nm 甚至更遠的技術世代。

致謝

這項工作是imec 高級圖案化團隊與imec 的設備和材料供應商密切合作的結果。

審核編輯 黃昊宇

-

光刻機

+關注

關注

31文章

1147瀏覽量

47253

發布評論請先 登錄

相關推薦

問一下一個單片機的io口分別控制四個燈板該怎么設計電路?

Hyper-NA光刻系統,價格會再次翻倍嗎?

Rapidus對首代工藝中0.33NA EUV解決方案表示滿意,未采用高NA EUV光刻機

ASML考慮推出通用EUV光刻平臺

臺積電A16制程采用EUV光刻機,2026年下半年量產

英特爾率先推出業界高數值孔徑 EUV 光刻系統

Intel和ASML宣布全球第一臺High-NA光刻機“首光”

高速風筒的下一個風口是直發吹風機?【其利天下技術】

英特爾成為全球首家購買3.8億美元高數值孔徑光刻機的廠商

高NA EUVL:光刻的下一個主要步驟

高NA EUVL:光刻的下一個主要步驟

評論