在FPGA研發及學習過程中,有一個關鍵步驟就是下板實現,做硬件“硬現”很重要,一般來說用JTAG口比較常見一些,因此相信肯定有些大俠遇到過JTAG口失靈或者損壞無法使用的事情。最近我就遇到了這類事情,FPGA的JTAG口突然就不能下載程序了,而且這種事情已經不是第一次了,之前在做項目的時候也出現過,而且出現的形式也極其相似,之前還用的好好的,第二天就不行了,真是讓人郁悶。為此,本人也是去嘗試了很多解決辦法,一開始也沒有去設想是JTAG口壞了,于是乎,本人換了usb-blaster,可一點反應也沒有。難道真的是JTAG口壞了?于是,本人就去查閱相關資料去搞清楚問題的本質在哪里,下面就是本人的一些收獲,分享出來,僅供各位大俠參考,一起交流學習。

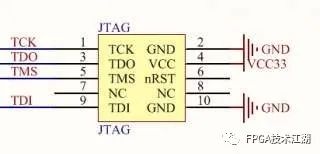

根據查閱資料及本人的一些實踐經驗所得,在使用JTAG下載接口的過程中,請不要隨意帶電插拔,否則會損壞FPGA芯片的JTAG口信號管腳。那么如何去確認JTAG口已經損壞了呢。首先你要去排除基本的幾項因素,一是,是否匹配連接,有很多設備會對應很多接口,在實際條件下要匹配正確,否則也會出現上述情況;二是,排除下載線的問題,如果是下載線壞了,可以使用多根下載線去嘗試,排除這類問題。如果還是不能訪問FPGA的JTAG口,那么很有可能你的FPGA芯片的JTAG口已經損壞。此時請用萬用表檢查TCK,TMS,TDO和Tdi是否和GND短路,如果任何一個信號對地短路則表示JTAG信號管腳已經損壞。

至于JTAG口是什么,這里我們也來探討一下,JTAG英文全稱是 Joint Test Action Group,翻譯過來中文就是聯合測試工作組。

JTAG是一種IEEE標準用來解決板級問題,誕生于20世紀80年代。今天JTAG被用來燒錄、debug、探查端口。當然,最原始的使用是邊界測試。

1、邊界測試

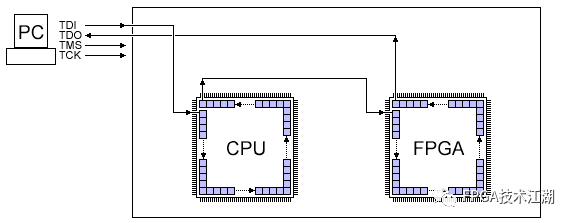

舉個例子,你有兩個芯片,這兩個芯片之間連接了很多很多的線,怎么確保這些線之間的連接是OK的呢,用JTAG,它可以控制所有IC的引腳。這叫做芯片邊界測試。

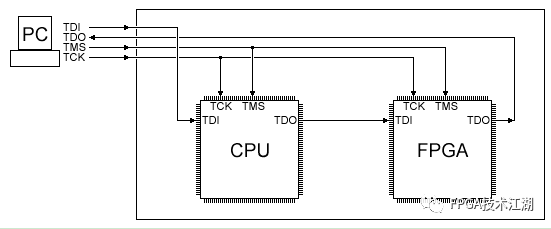

2、JTAG引腳

JTAG發展到現在已經有腳了,通常四個腳:TDI,TDO,TMS,TCK,當然還有個復位腳TRST。對于芯片上的JTAG的腳實際上是專用的。

TDI:測試數據輸入,數據通過TDI輸入JTAG口;

TDO:測試數據輸出,數據通過TDO從JTAG口輸出;

TMS:測試模式選擇,用來設置JTAG口處于某種特定的測試模式;

TCK:測試時鐘輸入;

TRST:測試復位。

CPU和FPGA制造商允許JTAG用來端口debug;FPGA廠商允許通過JTAG配置FPGA,使用JTAG信號通入FPGA核。

3、JTAG如何工作

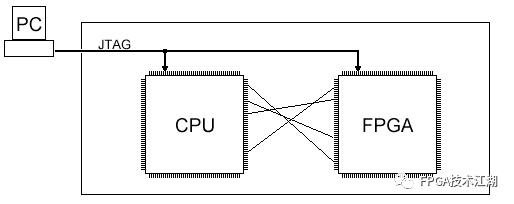

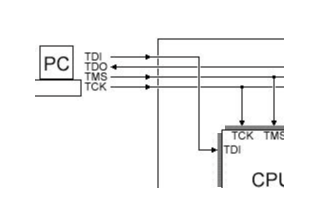

PC控制JTAG:用JTAG電纜連接PC的打印端口或者USB或者網口。最簡單的是連接打印端口。

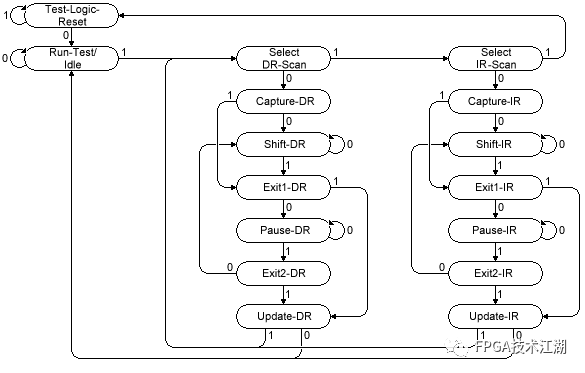

TMS:在每個含有JTAG的芯片內部,會有個JTAG TAP控制器。TAP控制器是一個有16個狀態的狀態機,而TMS就是這玩意的控制信號。當TMS把各個芯片都連接在一起的時候,所有的芯片的TAP狀態跳轉是一致的。下面是TAP控制器的示意圖:

改變TMS的值,狀態就會發生跳轉。如果保持5個周期的高電平,就會跳回test-logic-rest,通常用來同步TAP控制器;通常使用兩個最重要的狀態是Shift-DR和Shift-IR,兩者連接TDI和TDO使用。

IR:命令寄存器,你可以寫值到這個寄存器中通知JTAG干某件事。每個TAP只有一個IR寄存器而且長度是一定的。

DR:TAP可以有多個DR寄存器,與IR寄存器相似,每個IR值會選擇不同的DR寄存器。(很迷)

4、JTAG鏈相關疑問

計算JTAG鏈中的IC數目:

一個重要的應用是IR值是全一值,表示BYPASS命令,在BYPASS模式中,TAP控制器中的DR寄存器總是單bit的,從輸入TDI到輸出TDO,通常一個周期,啥也不干。

可用BYPASS模式計算IC數目。如果每個IC的TDI-TDO鏈的延遲是一個時鐘,我們可以發送一些數據并檢測它延遲了多久,那么久可以推算出JTAG鏈中的IC數目。

得到JTAG鏈中的器件ID:

大多數的JTAG IC都支持IDCODE命令。在IDCODE命令中,DR寄存器會裝載一個32bit的代表器件ID的值。不同于BYPASS指令,在IDCODE模式下IR的值沒有標準。不過每次TAP控制器跳轉到Test-Logic-Reset態,它會進入IDCODE模式,并裝載IDCODE到DR。

5、邊界掃描:

TAP控制器進入邊界掃描模式時,DR鏈可以遍歷每個IO塊或者讀或攔截每個引腳。在FPGA上使用JTAG,你可以知曉每個引腳的狀態當FPGA在運行的時候。可以使用JTAG命令SAMPLE,當然不同IC可能是不同的。

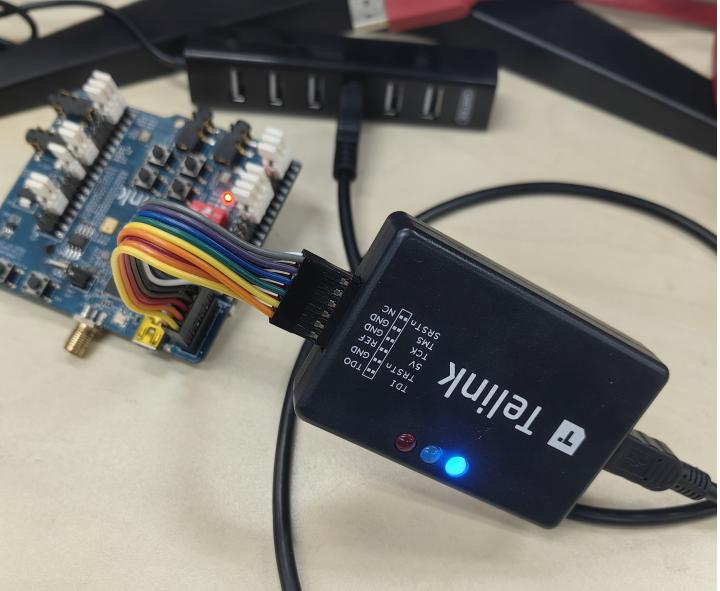

如果JTAG口已經損壞了,那只能“節哀順變”了,但是也不要只顧著傷心,最重要的是分析其中的原因,做其他事情也是一樣的道理。那我們就來分析分析,我們在使用的過程中,可能經常為了方便,隨意插拔JTAG下載口,在大多數情況下不會發生問題。但是仍然會有很小的機率發生下面的問題,因為熱插拔而產生的JTAG口的靜電和浪涌,最終導致FPGA管腳的擊穿。至此,也有人懷疑是否是盜版的USB Blaster或者ByteBlasterII設計簡化,去除了保護電路導致的。但經過很多實際情況的反饋,事實證明原裝的USB Blaster 也會發生同樣的問題。也有人提出質疑是否是ALTERA的低端芯片為了降低成本,FPGA的IO單元沒有加二極管鉗位保護電路。這類質疑其實都不是解決問題的本質,最重要的是我們要規范操作,盡可能的去減少因為實際操作不當導致一些硬件設備、接口等提前結束壽命或“英年早逝”,那重點來了,關于JTAG下載口的使用,我們需要如何去規范操作呢。

上電時的操作流程順序:

1.在FPGA開發板及相關設備斷電的前提下,插上JTAG下載線接口;

2.插上USB Blaster或者ByteBlasterII的電纜;

3.接通FPGA開發板的電源。

下電時的操作流程順序:

1.斷開FPGA開發板及相關設備的電源;

2.斷開USB Blaster或者ByteBlasterII的電纜;

3.拔下JTAG下載線接口,并放置適宜地方存儲。

雖然上述的操作步驟有點繁瑣,有時我們在使用的時候也是不以為然,但是為了保證芯片不被損壞,建議大家還是中規中矩的按照上述的步驟來操作。本人上述出現的問題,經過檢測后就是TCK跟GND短路了,雖然發生的概率不是很大,但是為了能夠更合理更長久的的使用硬件相關設備,還是建議大家在實操過程中,不要擔心繁瑣,中規中矩操作,換個角度思考,“多磨多練”也是對自己有好處的。最后,還是給各位嘮叨一句,關于JTAG下載口的使用最好不要帶電熱插拔,起碼可以讓JTAG口“活”的久一些,畢竟長情陪伴也是挺不錯的,不要等到失去了才知道惋惜。

審核編輯 :李倩

-

FPGA

+關注

關注

1626文章

21670瀏覽量

601882 -

JTAG

+關注

關注

6文章

398瀏覽量

71601 -

開發板

+關注

關注

25文章

4948瀏覽量

97202

原文標題:關于JTAG口,你了解多少?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

怎么實現5509A采用mic口和line口同時輸入兩路音頻信號,可以提供一下思路嘛?

自感線圈斷電時燈泡為啥會閃亮一下

Samtec小課堂 | 兩分鐘了解JTAG連接器

歡創播報 支付寶“碰一下”正式發布

使用esp32-s3的USB Serial/JTAG口連接linux時,找不到設備是怎么回事?

FPGA的JTAG口很脆弱?以后要多加小心了

請問UDE可以直接驅動miniWiggler JTAG口嗎?

【技術專欄】泰凌微電子JTAG工具使用教程(一)

探討一下JTAG口是什么?

探討一下JTAG口是什么?

評論