芯片驗證和調試,可以說是芯片開發中最具挑戰性的環節,通常需要耗費開發者們大量的時間和精力。

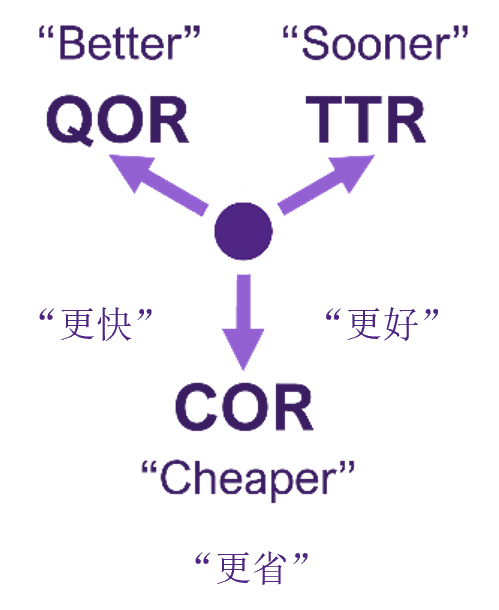

多年來,研究表明,每一代芯片上用于驗證階段的時間和資源占比均呈現不斷增加的態勢。總體而言,驗證階段工作的增長速度超過了芯片開發項目的其他階段。團隊要求芯片驗證能夠以更少的時間和資源來實現更好的結果。也就是說,驗證工具和技術不僅要緊跟市場需求,同時還要考慮三個維度:設計質量(QoR)、結果完成時間(TTR)、實現成本(CoR)。

基于機器學習(ML)的人工智能(AI)技術可以顯著改善芯片驗證的這三個維度要求,所以說,AI是芯片驗證升級過程中不可或缺的關鍵技術。

將AI技術用于

靜態驗證和形式驗證

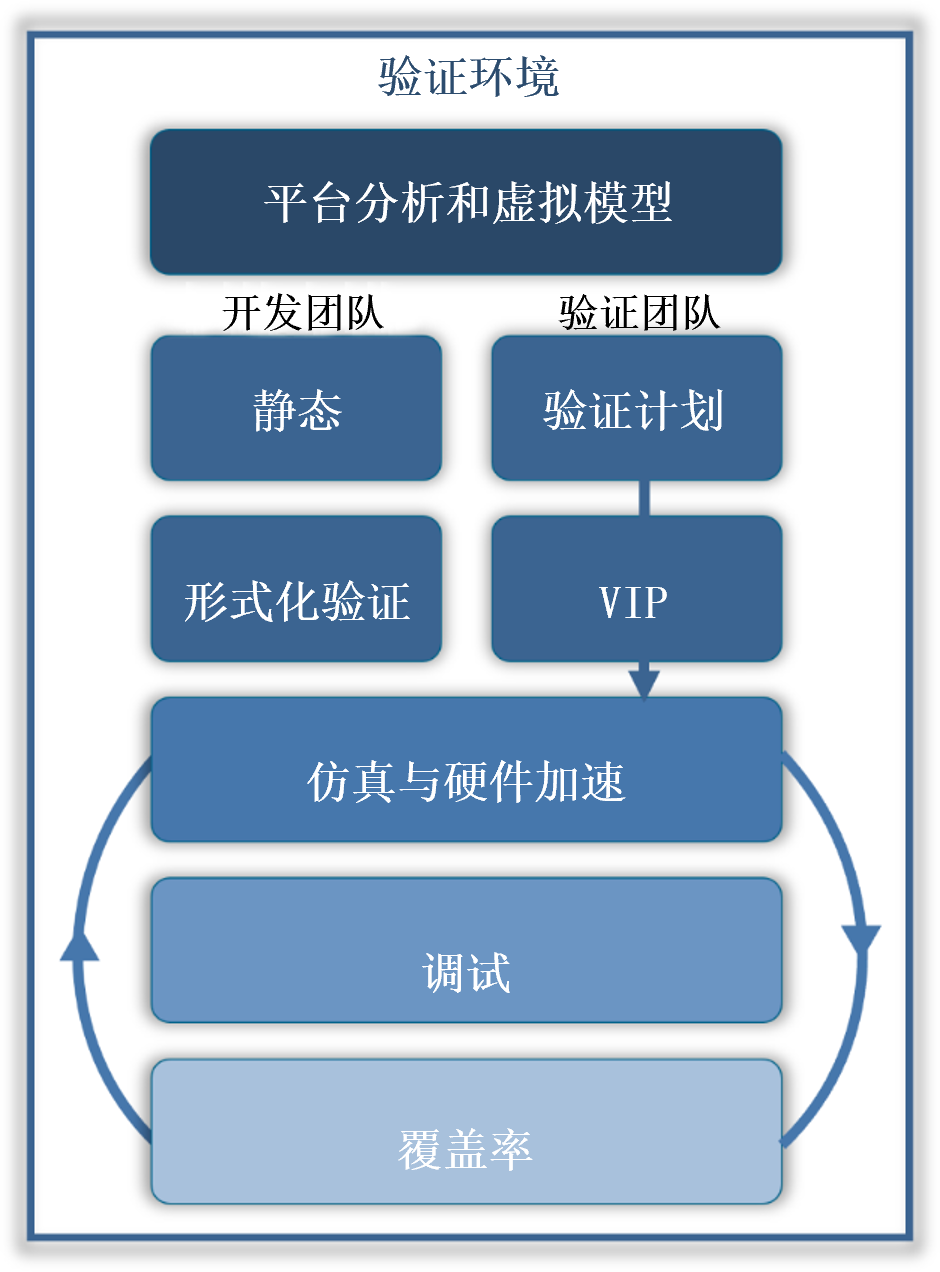

在了解AI技術如何賦能芯片驗證之前,先來看看一個典型的芯片驗證流程是怎樣的:

首先,在開發者編寫寄存器傳輸級(RTL)代碼之前,架構團隊會構建芯片的虛擬模型并分析系統性能。待做出關鍵決策后,設計團隊將開發RTL模型,并通過使用具有強大語言校驗功能的集成開發環境(IDE)來捕獲編碼錯誤,并進行修復。

修復校驗錯誤后,開發者將運行靜態驗證工具來檢測設計中的結構錯誤。

之后,開發者們通過形式驗證所提供的更深入的分析,嘗試證明RTL設計的關鍵屬性。這些工具可由開發者運行,也可以與形式化驗證專家合作完成。

與此同時,驗證團隊通常會利用現有的驗證IP(VIP)開發測試平臺和模型,運行一系列測試以實現驗證計劃的目標。此類測試主要在仿真環境中運行,但近年來使用硬件加速平臺也變得越來越普遍。

覆蓋率指標是衡量驗證進度的主要方法。覆蓋率收斂是一個高度迭代的過程,這往往也是驗證計劃中最耗時的部分。

▲ 芯片驗證流程的高維度視圖

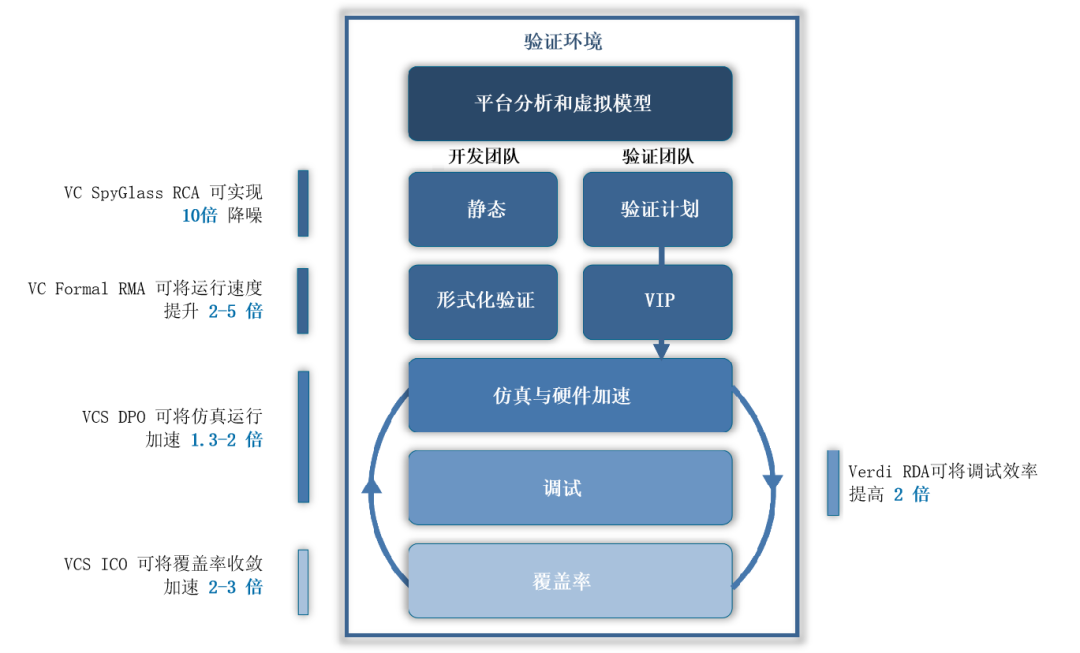

在靜態驗證過程中,一個錯誤就可能會導致數百甚至數千個違例的出現,對開發者來說是件非常頭大的事情。在這一過程中引入AI/ML是非常有用的,AI/ML可以根據相似的特征將違例進行自動歸類,在此基礎上,開發者還可利用根本原因分析(RCA)專門識別和修復每個群組中的某一個違例行為,進而解決相應群組中的其余違規行為,這種自動化可以將調試效率提高10倍。新思科技用于靜態驗證的VC SpyGlass平臺和用于特定低功耗靜態驗證的VC LP就包含了這項AI技術。

形式驗證是檢測設計過程中深層錯誤最有效的方法,這些錯誤在仿真測試中很可能會遺漏。為了做到全面檢測,形式驗證使用了大量強大的引擎來來對驗證過程中所需要的成千上萬的設計屬性進行證明。因此最大限度地提高引擎性能,對于確保形式驗證的效率至關重要。

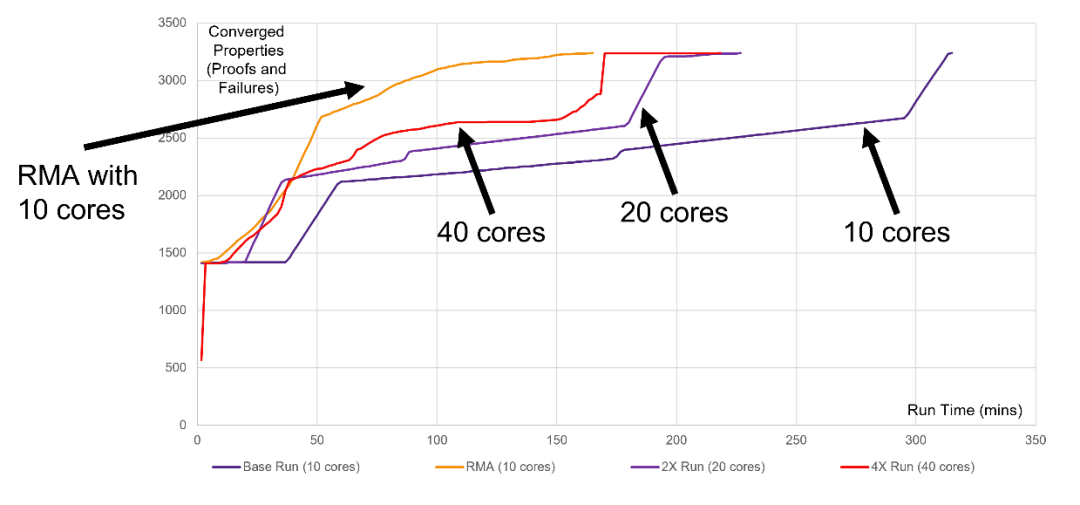

新思科技VC Formal 是業內首個在引擎編排、回歸和調試中利用ML技術的形式化驗證工具。引擎編排旨在將引擎與屬性正確配對,在物理計算資源和時間的限制下實現最短運行時間和最佳收斂效果。VC Formal在處理每個屬性時均采用即時強化學習法,同時學習有效和無效內容,以指導下一組操作的編排,這一功能稱為“智能策略選擇”。此外,針對每個屬性所做的決定會在運行結束時保存到數據庫中,以便利用之前的學習成果優化后續運行結果,這個叫做“回歸模式加速器”(RMA)。

基準數據顯示,此類ML技術可將速度提升10倍以上,帶來額外的收斂效果,在降低TTR和COR的同時提高QOR。

▲ 利用RMA加快屬性收斂

將AI技術用于

仿真和調試

仿真是芯片驗證的核心,仿真類錯誤約占錯誤發現總數的65%。

有時,為修復錯誤而對設計所做的更改可能無法正常工作或引入了新的問題,因此頻繁的回歸對于快速檢測問題并保持項目的正常進行至關重要。

仿真和回歸性能存在數個影響因素,而其中至少兩個因素可采用AI進行改進。首先是仿真和回歸運行時的設置。現代仿真器有許多選項和開關,會對性能產生重大影響。驗證開發者需要時間和專業知識來優化特定設計和測試平臺的仿真器設置。而隨著代碼的演進,可能需要調整設置以保持最佳性能。利用ML來學習并維護仿真器選項和開關這一自動化過程可以極大地提高回歸性能和效率。

新思科技的VCS仿真器中的動態性能優化(DPO)技術就是利用AI來改進仿真性能,它使用ML和基于規則的AI技術從先前的回歸運行中進行學習,自動調整VCS設置以獲得最佳性能。這一過程將自動完成,無需用戶輸入。與手動進行仿真器設置相比,DPO可使仿真運行速度提高1.3-2倍。

對整體回歸性能影響最大的是覆蓋率收斂所需的時間。以前,驗證開發者會審查仿真報告以確定未達到的覆蓋率,然后修改測試或編寫新測試以覆蓋設計中的缺失部分。有了受約束的隨機測試平臺,他們通常是修改測試平臺的約束條件,以便將自動刺激生成集中于未覆蓋的情況,但這仍然需要手動完成。重復已經實現的覆蓋會浪費大量時間。AI/ML在驗證中的另一項應用可以改善這一情況,VCS仿真器的智能覆蓋優化(ICO)功能可以優化受約束的隨機刺激的統計質量,并提供對影響覆蓋率的測試問題的分析結果。在最近的芯片項目中,ICO已經被證明可將覆蓋率的收斂速度提高2-3倍。驗證團隊可以在更短的時間內實現更高的總覆蓋率,從而縮短時間并節省資源。

調試是驗證流程的最后一步,它與仿真是同時進行的。在項目期間會運行無數次仿真回歸。每次回歸失敗時,驗證團隊都必須檢查報告并調試失敗的原因。RTL和測試平臺代碼會隨著錯誤的修復以及新功能的添加和測試而不斷變化,回歸失敗已是家常便飯。但手動處理日常的回歸失敗給驗證工程資源造成了巨大負擔。如今,AI/ML技術可以助力解決這一問題。盡管仿真測試失敗的原因通常比靜態違規行為要復雜得多,但自動RCA的原則仍然適用。

新思科技的Verdi自動調試系統中的回歸調試自動化(RDA)功能可根據故障特征自動將故障分類,比如故障是來自設計還是測試平臺,然后這些故障會被自動分箱,再通過RCA找出具體分類中故障的原因。RDA技術可以將整體調試效率提高2倍。

▲ 新思科技驗證流程采用AI/ML技術帶來的優勢

下載白皮書

借助AI實現更快更好更高效的驗證

AI和ML技術在芯片設計和驗證流程中的應用與日俱增。單就驗證而言,AI/ML可以加速靜態驗證的故障分析,提升形式化驗證的性能,提高仿真效率,加速覆蓋率收斂,快速輕松地完成仿真調試。圖9總結了流程改進為驗證團隊和整個芯片項目帶來的好處。新思科技的解決方案通過提供更好的QOR、更快的TTR和更省的COR來實現驗證團隊的目標并解決其所面臨的主要挑戰。如今,強大而靈活的AI/ML技術已多點開花,改進驗證流程的多個方面。

新思科技發布芯片驗證白皮書《借助AI實現更快、更好、更高效的驗證》,更加詳細的闡述了本文中提到的種種驗證挑戰,以及AI技術帶來的改變,和新思科技EDA解決方案中一些具體功能。

審核編輯:湯梓紅

-

AI

+關注

關注

87文章

30172瀏覽量

268433 -

新思科技

+關注

關注

5文章

787瀏覽量

50307 -

芯片驗證

+關注

關注

5文章

34瀏覽量

47201

原文標題:注入AI的芯片驗證有多高效?翻開這份白皮書獲取答案【附下載】

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

“視網膜”重裝來襲 AI技術為視頻業務場景賦能

新能力上線 | 訊飛AI能力星云賦能,4項OCR技術助力“證”途!

【HarmonyOS HiSpark AI Camera】AI功能攝像機驗證

機器學習如何賦能風力發電?

AI賦能“電子哨兵”推動城市的智能化和數字化進程(附“電子哨兵”方案)

英碼科技精彩亮相火爆的IOTE 2023,多面賦能AIoT產業發展!

2018 AI為誰賦能 如何打造AI企業核心競爭力

AI技術正在賦能我國提升疫情治理

AI技術如何賦能智慧交通?

高通AI技術如何賦能物聯網等廣闊領域?

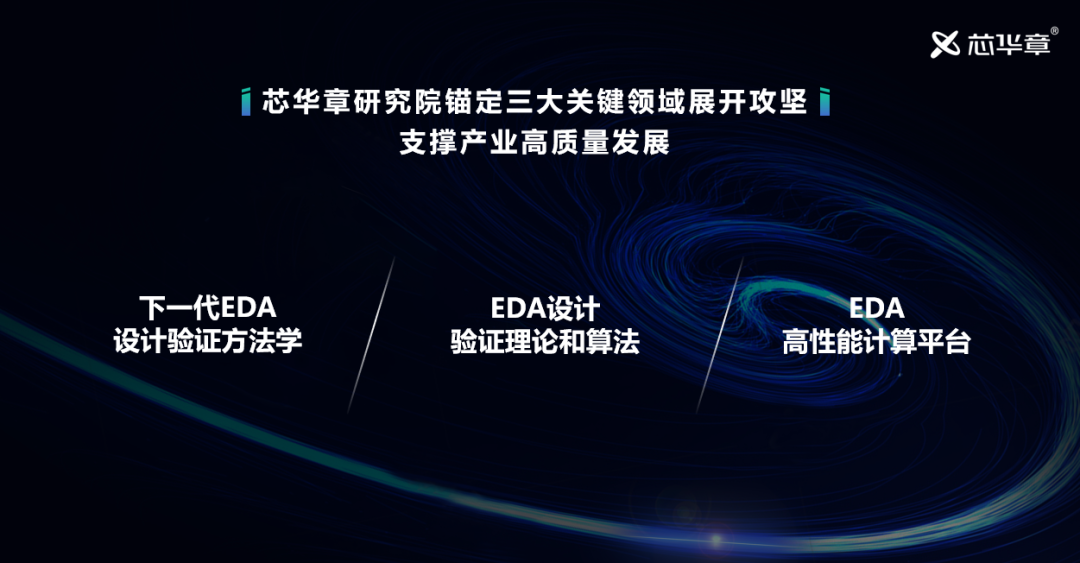

光計算賦能 芯華章研究院攜手曦智科技 聯合打造芯片驗證黑科技

AI技術如何賦能芯片驗證

AI技術如何賦能芯片驗證

評論