7月27日,《NanoCell精準高效的特征提取解決方案》在線研討會火熱舉辦,概倫電子高級首席研發工程師章勝分享了標準單元庫開發挑戰及單元庫特征化工具。錯過直播也沒關系,一文帶你了解概倫電子精準高效的標準單元庫EDA解決方案NanoCell。

標準單元庫是芯片設計的重要基礎。在先進工藝下,大量Sign-Off工藝角的引入,對單元庫的特征如時序、功耗、噪聲及統計變化提出更高的提取要求,從而使仿真計算量呈幾何級數增大,成為數字芯片設計的瓶頸。因此,單元庫特征提取的效率提升是縮短開發周期的關鍵。

標準單元庫開發挑戰

工藝難度增大,器件尺寸在縮小;設計難度增大,設計裕量在減小,這些要求更復雜的特征提取模型,更多的工藝角和更高質量的單元庫。

隨著晶體管的物理尺寸進入納米級,電子遷移率降低、漏電流增大、靜態功耗增大等問題層出不窮,使得新結構開發迫在眉睫。目前業界普遍的晶體管結構演化大致是22nm及以上是Planar平面晶體管結構工藝,16nm到3nm是FinFET鰭式場效應晶體管結構工藝,2nm及以下,從IMEC技術研究來看,下一代將是GAA(Gate-Around-All)環繞柵極晶體管結構工藝。

工藝和設計難度的增加,使得模型提取變得更為復雜。典型的就是先進工藝下,對于低壓設計的用戶需求。低壓情況下,器件的Variation統計變化增大,使得在Nominal 電壓下的各項設計指標正態分布變得非對稱,具有長尾效應,需要更先進的LVF模型,liberty format Variation模型來對此進行建模。而LVF是通過Monte-Carlo仿真取得的結果,因此需要大量的資源開銷。

為了滿足多種多樣的設計應用,單元的數量從幾百顆增加到一千多顆,用于時序、功耗、可靠性驗收的Sign-Off工藝角也由早期的幾個發展到幾百之多,因此需要海量的License、CPU、磁盤開銷來應對挑戰。

這么多庫的產生,需要高質量的驗證,以確保芯片的正常生成。面對這些挑戰,概倫電子標準單元庫特征化和驗證工具應運而生。

NanoCell設計初衷

基于概倫電子DTCO平臺,立足器件建模和仿真器領域深厚的技術積累,來解決標準單元庫特征提取遇到的難點和挑戰。

概倫電子擁有設計和制造兩大環節的核心關鍵工具,業界廣泛認可且長期采用的Golden器件建模工具BSIMProPlus,支持7nm/5nm/3nm最新工藝及BISM3/BSIM4/BSIM6/BSIMCMG行業標準緊湊型模型;高精度、高性能SPICE仿真器NanoSpice具有最嚴格的精度配置且經過國際領先代工廠的嚴苛驗證,配備高性能、輕量級調用接口。

標準單元庫特征提取工具NanoCell正是基于概倫電子深厚的器件建模和仿真器技術去開發,達到高精度、高性能,簡單易用的特征化工具。

NanoCell產品優勢

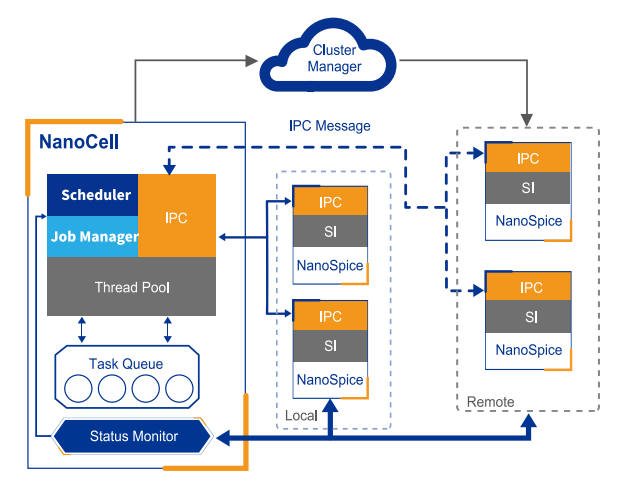

NanoCell是一款快速精確且簡單易用的標準單元庫特征化EDA工具。通過內置的NanoSpice仿真器,采用先進的分布式并行架構技術和單元電路分析提取算法,精確且高效的對單元電路進行時序、功耗及噪聲等特征進行仿真與提取,提供友好易使用的接口,幫助用戶縮短產品開發周期。

較之于其他標準單元庫特征化工具,NanoCell具有以下幾個特點:

- 精確-內嵌高精度仿真器NanoSpice

- 快速-先進的分布式并行架構

- 易用-友好且設置簡單的用戶接口

- 雙CPU架構支持(X86/ARM)

- 自動化單元電路分析、Arc提取

- 時序、功耗、噪聲等特征仿真和提取

NanoCell在精度方面嚴格對標業界主流的標準:

- Timing《 1%

- Constraint《 2ps

- Power《 5%

綜上所述,NanoCell支持當前業界主流的特征模型,包括NLDM、CCS、CCSN、CCSP、LVF以及Verilog;通過內置的高精度NanoSpice仿真器,模型精度達到業界標準;擁有強大的分布式并行計算能力;支持主流的HPC集群系統(SGE/LSF);同時提供ARM與X86的平臺支持。NanoCell是具有高精度、高靈活性、快速易操作的多平臺適用的標準單元庫特征化解決方案。

-

芯片

+關注

關注

453文章

50406瀏覽量

421817 -

eda

+關注

關注

71文章

2708瀏覽量

172881 -

概倫電子

+關注

關注

1文章

77瀏覽量

8708

原文標題:錯過直播?一文了解精準高效的標準單元庫EDA解決方案NanoCell

文章出處:【微信號:khai-long_tech,微信公眾號:概倫電子Primarius】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

概倫電子精準高效標準單元庫EDA解決方案NanoCell

概倫電子精準高效標準單元庫EDA解決方案NanoCell

評論