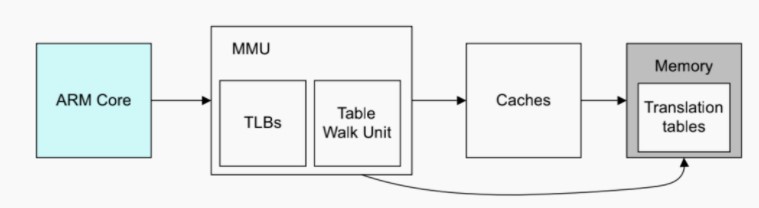

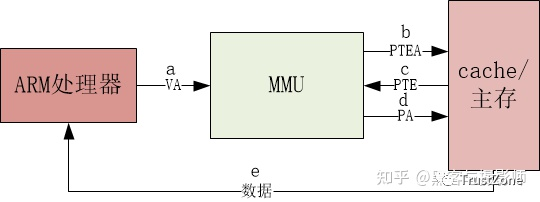

處理器中的MMU可以讓我們能夠構(gòu)建具有多個(gè)VA-PA映射表的數(shù)字系統(tǒng)。

不同程序操作同一個(gè)VA,這個(gè)VA被不同的頁表映射到不同的PA。

操作系統(tǒng)內(nèi)核將每個(gè)應(yīng)用程序的指令和數(shù)據(jù)放在物理內(nèi)存中,但是應(yīng)用程序并不是直接通過物理地址讀寫這些指令和數(shù)據(jù)。簡(jiǎn)單來說,就是通過MMU進(jìn)行VA-PA轉(zhuǎn)換,這讓程序設(shè)計(jì)變得簡(jiǎn)單很多。

所有的程序員都應(yīng)該了解和感謝虛擬地址,它讓你的工作沒那么dirty。因?yàn)檫@個(gè)dirty的工作被操作系統(tǒng)和硬件完成了。

頁表

在處理器中這種VA-PA的映射關(guān)系稱為頁表,頁表中的每一個(gè)頁表項(xiàng)都完成了某個(gè)VA-PA的映射對(duì)應(yīng)。頁表格式其實(shí)還比較復(fù)雜,除了VA-PA的映射關(guān)系,還有其他的一些內(nèi)存屬性和訪問權(quán)限定義。

處理器內(nèi)核生成的地址都是虛擬地址,然后在訪問實(shí)際物理內(nèi)存空間之前通過MMU映射成了物理地址。但是,基于不同的頁表粒度大小,比如說4KB,實(shí)際的VA-PA的映射只是將高比特做了替換。

在早期這個(gè)VA-PA的映射過程并不是由硬件完成的,后來才由硬件完成這個(gè)VA-PA轉(zhuǎn)換,形象點(diǎn)來說稱為translation table walking。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19165瀏覽量

229130 -

MMU

+關(guān)注

關(guān)注

0文章

91瀏覽量

18268

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

大疆嵌入式筆試題及參考,處理器讀取內(nèi)存的過程

處理器在讀內(nèi)存的過程中,CPU核、cache、MMU如何協(xié)同工作?

通過處理器創(chuàng)建MC9S08DZ60芯片

ARM處理器有哪些性能呢

MMU存儲(chǔ)管理單元的工作原理是什么?如何實(shí)現(xiàn)其流程呢

求助,尋找支持MMU的處理器

ARM CoreLink MMU-400系統(tǒng)內(nèi)存管理單元技術(shù)參考手冊(cè)

Arm CoreLink MMU?700系統(tǒng)內(nèi)存管理單元技術(shù)參考手冊(cè)

ARM CORELINK?MMU-600AE系統(tǒng)內(nèi)存管理單元技術(shù)參考手冊(cè)

S3C2410內(nèi)存管理單元MMU基礎(chǔ)實(shí)驗(yàn)

沒有MMU的處理器可否安裝操作系統(tǒng)呢?

鴻蒙輕內(nèi)核源碼分析:MMU 協(xié)處理器

通過處理器中的MMU進(jìn)行VA-PA轉(zhuǎn)換

通過處理器中的MMU進(jìn)行VA-PA轉(zhuǎn)換

評(píng)論