碳化硅 (SiC) 行業(yè)正在快速發(fā)展,為21世紀(jì)的眾多應(yīng)用提供高效且緊湊的電力電子解決方案。電動(dòng)汽車( EV) 市場(chǎng)是一個(gè)關(guān)鍵應(yīng)用,首先是特斯拉,現(xiàn)在其他公司在其動(dòng)力傳動(dòng)系統(tǒng)逆變器中采用了 SiC。市場(chǎng)上銷售的 600 至 1,700 V 的 SiC 器件范圍已廣為人知,并為傳統(tǒng)的硅 (Si) 功率器件提供了一種快速開關(guān)、寬帶隙的替代方案。

雖然包括開關(guān)速度和高溫能力在內(nèi)的技術(shù)優(yōu)勢(shì)現(xiàn)已廣為人知,但成本仍然是一個(gè)爭(zhēng)論點(diǎn)。PGC Consultancy 分析了 SiC 裸片成本,在本文和未來的文章中,他們將解釋高成本背后的原因以及可以采取哪些措施來降低價(jià)格。他們還提供了關(guān)于到本世紀(jì)末電動(dòng)汽車銷售可能會(huì)主導(dǎo)汽車行業(yè)的成本的長(zhǎng)期觀點(diǎn)。

碳化硅的成本

根據(jù) PGC 咨詢公司的數(shù)據(jù),2021 年 9 月,100-A 分立式 SiC MOSFET(650 V 和 1,200 V)的零售價(jià)幾乎是等效 Si IGBT 價(jià)格的 3 倍。盡管 SiC 器件的占用率要低 3 到 4 倍加工晶片上的區(qū)域。

造成這種成本的原因有幾個(gè): 主要貢獻(xiàn)者是 SiC 襯底,可以肯定的是,這種情況將持續(xù)一段時(shí)間。這是因?yàn)槭褂?Czochralski 工藝生產(chǎn)高質(zhì)量的硅晶片,在該工藝中,從 1,500?C 的熔融硅池中提取一米長(zhǎng)的硅晶錠。生產(chǎn) SiC 的升華過程需要大量能量才能達(dá)到 2,200?C,而最終可用的晶錠長(zhǎng)度不超過 25 毫米,并且生長(zhǎng)時(shí)間非常長(zhǎng)。其結(jié)果是與 Si 相比,SiC 晶片的成本增加了 30 到 50 倍。與 SiC 襯底成本相比,外延(在襯底表面上生長(zhǎng) SiC 器件的高質(zhì)量層)和制造成本等其他成本較低。然而,

正如 PGC 咨詢公司指出的那樣,另一個(gè)需要考慮的事實(shí)是制造各個(gè)階段的效率,我們?cè)谶@里也進(jìn)行了討論。良率與從晶錠中取出的不可用晶片的數(shù)量以及外延和制造后不可用的管芯數(shù)量有關(guān)。制造后影響芯片良率的一個(gè)主要因素是材料的質(zhì)量,其中包括導(dǎo)致器件無法制造的一系列缺陷以及影響可靠性的其他不太明顯的缺陷。正如 PGC Consultancy 指出的那樣,制造中的另一個(gè)問題是 MOSFET 柵極氧化物的可靠性。

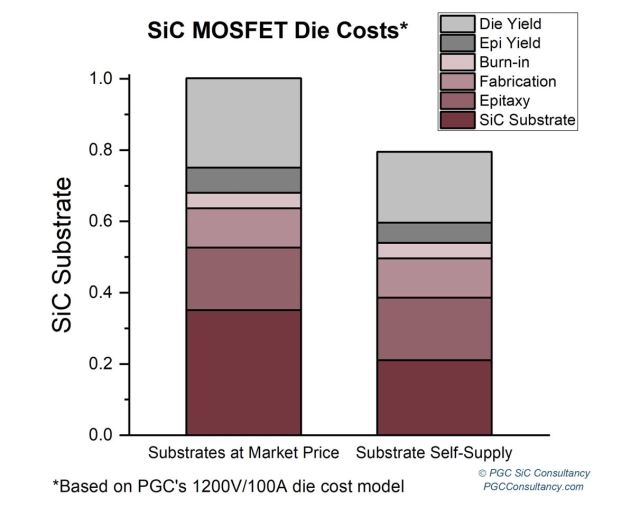

圖 1:SiC MOSFET 裸片的成本細(xì)分,基于在 150 毫米基板上制造的同類最佳 2021 1,200-V/100-A 器件

圖 1 顯示了 SiC MOSFET 裸片的成本細(xì)分,產(chǎn)量來自于 2021 年同類最佳 1,200-V/100-A 商用器件,在 150-mm 襯底上生產(chǎn)。這兩個(gè)堆棧近似于兩種基板供應(yīng)模式,將大多數(shù)以市場(chǎng)價(jià)格購(gòu)買基板的公司與垂直整合的公司進(jìn)行比較,因此可以以成本自供基板。所有其他費(fèi)用都被認(rèn)為是相等的。

折舊成本因公司而異,需要單獨(dú)分析,但是,隨著公司投資實(shí)現(xiàn) 200 毫米產(chǎn)能,這一比例將會(huì)增加。如果需要,設(shè)備的包裝是應(yīng)考慮的額外成本;然而,這個(gè)成本與基于硅的設(shè)備沒有什么不同。

降低 SiC 成本

讓我們看看 PGC Consultancy 詳細(xì)介紹的未來十年成本降低的貢獻(xiàn)者。如今,SiC 器件主要在 150 毫米直徑的基板上開發(fā)。Wolfspeed 和 GT Advanced Technologies(在被 onsemi 收購(gòu)之前)宣布了在 2022 年將尺寸升級(jí)到 200 毫米的提議。這將使單次制造運(yùn)行中可以生產(chǎn)大約 1.8 倍以上的設(shè)備,從而降低制造成本。然而,PGC Consultancy 并不認(rèn)為此次升級(jí)會(huì)顯著降低芯片成本中的襯底部分。正如之前從 100 毫米到 150 毫米的過渡中所看到的,成本可能會(huì)與面積成正比,但隨著技術(shù)的成熟和競(jìng)爭(zhēng)的加劇,成本將穩(wěn)步下降。

至少在開發(fā)的早期階段,從 200 毫米晶圓上取出的芯片的成本可能比 150 毫米晶圓的成本略高,但是,晶圓良率、外延良率和芯片良率的優(yōu)化將很快發(fā)生。經(jīng)過短暫的發(fā)展,200毫米晶圓的缺陷密度可能會(huì)降低,制造成本也會(huì)降低;這可能會(huì)導(dǎo)致早期這些晶圓直徑之間的錐形過渡。

如Wolfspeed的Mohawk Valley晶圓廠計(jì)劃所示,200 mm晶圓的加工并不簡(jiǎn)單,需要高度自動(dòng)化的專業(yè)工具。然而,從長(zhǎng)遠(yuǎn)來看,這項(xiàng)投資將償還成本,因?yàn)橹灰锌赡埽妥屓藗冞h(yuǎn)離加工,降低成本,預(yù)計(jì)將對(duì)產(chǎn)量產(chǎn)生積極影響。最后,在基板方面,越來越多的公司希望在“垂直整合”的公司內(nèi)自行供應(yīng)基板,以了解這對(duì)成本的影響(見圖1)。由于很少有芯片制造商能夠完全自主供應(yīng),這給那些能夠自主供應(yīng)的制造商帶來了競(jìng)爭(zhēng)優(yōu)勢(shì)。

除基板外,PGC咨詢公司認(rèn)為,器件設(shè)計(jì)的進(jìn)步在降低每一代SiC MOSFET的電阻和成本方面同樣重要。歐姆定律規(guī)定,單位面積電阻的任何降低都會(huì)導(dǎo)致電流密度的增加。這意味著可以減少芯片面積,同時(shí)保持給定的額定電流。然而,從較小芯片中去除廢熱的問題意味著不能忽略熱阻的變化,因此芯片面積與其電阻和熱阻的平方根成比例。因此,電阻降低50%將導(dǎo)致芯片的有源區(qū)減少29%。較小的芯片尺寸不僅增加了每個(gè)晶片的生產(chǎn)數(shù)量,而且還提高了成品率。

PGC Consultancy 的 SiC 成本預(yù)測(cè)模型基于 2021 年同類最佳 1,200-V/100-A 器件,如圖 2 所示。模型的三個(gè)輸入如上圖所示;基于這些假設(shè)的預(yù)計(jì)費(fèi)用如下所示。所有數(shù)據(jù)都標(biāo)準(zhǔn)化為 2022 年 150 毫米芯片成本的已知值或估計(jì)值。最佳和最壞情況由上限和下限表示。在 2022 年和 2027 年,預(yù)計(jì)會(huì)出現(xiàn)兩代(第 4 代和第 5 代),預(yù)計(jì)每代都會(huì)帶來 45% 的阻力降低,最壞情況下降低到 40%,最好情況下降低到 50% 。 如前所述,由于面積根據(jù)電阻的平方根而減小,因此電阻減少 40% 到 50% 會(huì)導(dǎo)致有源器件面積減少 23% 到 29%。初始裸片尺寸基于同類最佳 1、200V/100A MOSFET(截至 2021 年 9 月)。顯示的輸出是 200-mm 和 150-mm 襯底的 1,200-V/100-A MOSFET 裸片的預(yù)期成本,顯示了基本、最佳情況和最差情況。

圖 2:PGC Consultancy SiC 成本預(yù)測(cè)模型,基于 2021 年同類最佳 1,200-V/100-A 器件。以上是模型中使用的三個(gè)輸入;以下是預(yù)計(jì)的模具成本。所有數(shù)據(jù)都標(biāo)準(zhǔn)化為 2022 年已知或估計(jì)的 150 毫米值。上限和下限代表最佳/最壞情況。

根據(jù)這些假設(shè),到 2030 年,在 200-mm 基板上制造的 1,200-V/100-A MOSFET 芯片的成本與今天基于 150-mm 基板的成本相比可能降低 54%。

總之,PGC Consultancy 的模型表明,改用 200 毫米基板不太可能立即降低芯片成本。然而,一旦推出 200mm 基板,基板質(zhì)量的持續(xù)改進(jìn),加上器件設(shè)計(jì)的持續(xù)增量收益,將使 SiC 在未來變得更具成本競(jìng)爭(zhēng)力。

審核編輯:郭婷

-

芯片

+關(guān)注

關(guān)注

453文章

50406瀏覽量

421820 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27010瀏覽量

216296 -

SiC

+關(guān)注

關(guān)注

29文章

2765瀏覽量

62454

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

中國(guó)AI企業(yè)創(chuàng)新降低成本打造競(jìng)爭(zhēng)力模型

在飽和狀態(tài)下運(yùn)行UCC2888x離線降壓以降低成本

什么是SiC功率器件?它有哪些應(yīng)用?

CC2340系統(tǒng)降低成本的方案剖析

使用SiC技術(shù)應(yīng)對(duì)能源基礎(chǔ)設(shè)施的挑戰(zhàn)

150度無壓燒結(jié)銀用于功率器件,提升效率降低成本

工業(yè)觸摸顯示屏在提升生產(chǎn)效率、降低成本等方面具有顯著優(yōu)勢(shì)

全面的SiC功率器件行業(yè)概覽

一文解析SiC功率器件互連技術(shù)

ZR機(jī)械手:提高生產(chǎn)效率,降低成本的有效途徑-速程精密

搬運(yùn)機(jī)器人已經(jīng)成為提高效率、降低成本的關(guān)鍵技術(shù)

SiC功率器件中的失效機(jī)制分析

SiC功率器件降低成本以推動(dòng)采用

SiC功率器件降低成本以推動(dòng)采用

評(píng)論