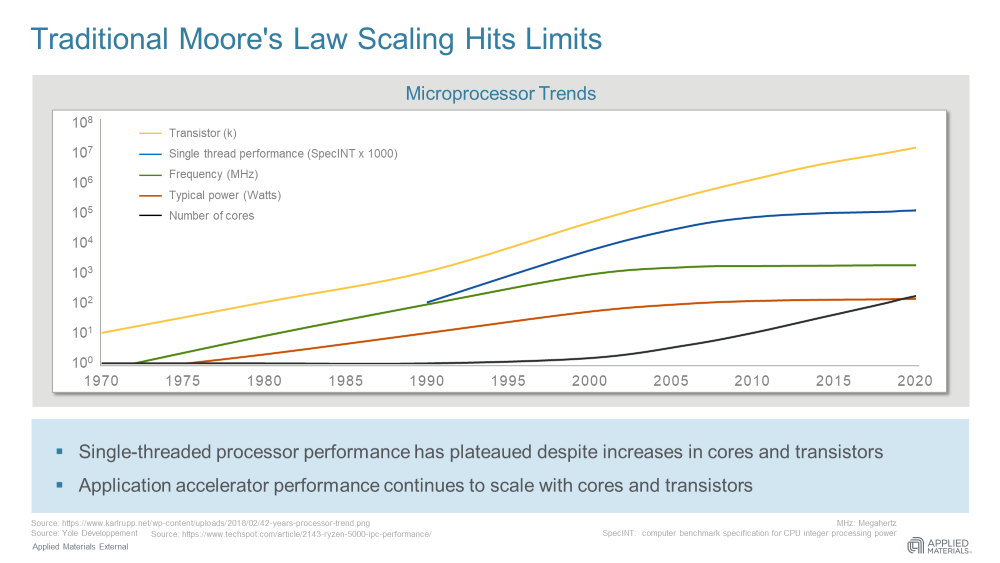

摩爾定律推動半導體行業繼續縮小晶體管的臨界尺寸以提高器件密度。

本世紀初,傳統的擴容開始遇到瓶頸。業界相繼開發出應變Si/Ge、高K/金屬柵、Fin-FET,使摩爾定律得以延續。

現在,場效應晶體管的臨界尺寸已降至7納米,即一個芯片上每平方厘米有近70億個晶體管,這給鰭式結構和納米制造方法帶來了巨大的挑戰。到目前為止,極紫外光刻技術已經在一些關鍵步驟中使用,并且面臨著大批量制造的對準精度和高成本問題。同時,新材料和 3D 復雜結構的引入給自上而下的方法帶來了嚴峻的挑戰。新開發的自下而上制造是一種很好的補充方法,為納米制造提供了技術驅動力。早在 1959 年,費曼教授推測,“底部有足夠的空間”。這個演講啟發了人類操縱原子或分子作為設計結構的構建塊。

原子級沉積是自下而上策略的典型代表。在第一部分中,沉積為垂直方向帶來橫向埃分辨率以及自上而下的蝕刻,例如雙圖案化。接下來,各種模板輔助選擇性沉積方法,包括介電模板、抑制劑和校正步驟,已被用于 3D 復雜結構的對齊。最后,原子級分辨率可以通過固有的選擇性沉積來實現。在本文中,我們討論了低維材料和新興應用,包括二維材料、納米線、納米粒子等。

原子級沉積方法的特點是薄膜的保形性和均勻性。原子級沉積可以為具有高縱橫比的多種結構帶來垂直方向的橫向分辨率,包括側壁、納米線、納米管等。自對準雙圖案是垂直分辨率的典型示例。原子級沉積可以提高納米圖案化的精度,獲得一些特殊的結構,可以進一步減小特征尺寸,提高晶體管的密度,從而在短期內促進摩爾定律的延續。隨著器件變得越來越復雜,薄膜的定向生長被認為是納米制造過程中的一個重要方面。選擇性沉積是實現對準的一種有效且有前途的方法,它可以減少光刻和蝕刻等步驟。通常,使用特殊模板實現高選擇性沉積是有效的。借助模板,芯片制造商不僅可以在三個維度上直接疊加晶體管,還可以將傳感、儲能等多功能集成到芯片中,制造出超級芯片。

通過當前自上而下的方法制備合適的模板用于選擇性沉積低維材料和復雜的 3D 結構是非常具有挑戰性的,已經研究了非模板選擇性沉積。后硅時代,原子級沉積可以制備多種替代納米材料,如二維材料、碳材料、鐵電材料、相變材料等,可以克服硅材料物理極限的限制,拓寬邊界摩爾定律。

陳榮(音譯)教授和她小組的其他研究人員已經確定了原子級沉積領域的一些關鍵挑戰:

“原子級沉積是一種面向未來的多功能沉積技術,必將在微納制造領域發揮越來越重要的作用。芯片制造商對這項技術表現出濃厚的興趣。除了微電子領域,原子級沉積在光電子、儲能、催化、生物醫學等領域也有廣泛的應用。”

“要實現高精度納米制造,需要深入研究原子級沉積的機理。”

“雖然表征技術正在蓬勃發展,但單原子表征和操縱技術仍有很大的改進空間。”

“為了實現復雜的納米結構制造,多種材料的多工藝耦合是必不可少的。但是如何實現流程集成呢?”

“除了以高精度制造薄膜和納米結構外,精度和加工效率也是相互抑制的因素。如何在工業中實現可靠的大批量制造?”

研究人員建議,原子級沉積可用于擴展摩爾定律及其他。原子級沉積正成為一種越來越有前途的技術,用于精確制造復雜的納米結構,能夠創建等效的形貌,更好地控制薄膜厚度,而不會使表面粗糙。它被認為是先進半導體技術節點和其他新興領域的使能技術。

-

半導體

+關注

關注

334文章

27014瀏覽量

216337 -

摩爾定律

+關注

關注

4文章

632瀏覽量

78934 -

晶體管

+關注

關注

77文章

9635瀏覽量

137852

原文標題:原子級沉積,擴展摩爾定律

文章出處:【微信號:cetc45_wet,微信公眾號:半導體工藝與設備】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

擊碎摩爾定律!英偉達和AMD將一年一款新品,均提及HBM和先進封裝

高算力AI芯片主張“超越摩爾”,Chiplet與先進封裝技術迎百家爭鳴時代

“自我實現的預言”摩爾定律,如何繼續引領創新

封裝技術會成為摩爾定律的未來嗎?

半導體行業能否走出低谷,中國影響幾何?

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

原子級沉積可用于擴展摩爾定律及其他

原子級沉積可用于擴展摩爾定律及其他

評論