如今,BittWare的SmartNIC Shell的解析器組件是使用Xilinx HLS C++開發環境構建的。但BittWare的SmartNIC Shell的早期版本雖然使用Xilinx SDNet工具,但使用了P4語言。

使用P4的一個原因是,它是一種新興的標準,受到在商品英特爾服務器上擁抱軟件定義網絡(SDN)的人們的歡迎。然而,Xilinx后來限制了SDNet的可用性。我們對P4的使用是專門針對SmartNIC Shell的終端用戶的,所以這種限制使我們不得不尋找更開放的解決方案。在我們使用HLS成功實現RSS之后,我們被激勵使用同樣的HLS方法(特別是Xilinx HLS C++環境)重新實現SmartNIC Shell解析器。

什么是“Tuple”?

在網絡中,tuple是指從網絡數據包中提取的字段,并組合在一起。最常見的是“5-tuple”,它結合了源和目的IP地址、源和目的IP端口(如果IP協議有這些端口的話)以及IP協議號。

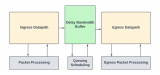

SmartNIC產品中的BittWare解析器會檢查數據包,并在可用的情況下提取最多4個數據包。它將這些數據放入添加到數據包元數據的96位字段中。該字段寬度為IPv4源和目標地址以及源和目標端口提供了足夠的位數。我們的解析器為數據包中不可用的字段提供零。如果一個數據包不包括任何IP有效載荷,那么完整的96位元組字段為零。

一個完整的5-tuple需要額外的8位來適應協議號。使用BittWare解析器的HLS用戶只需稍加修改源代碼就能輕松適應這一變化。

BittWare的RSS是一個可能在數據包流水線中跟隨解析器并消耗96位元組數據的塊的例子。在我們的應用筆記中閱讀關于該塊的內容,比較RTL和HLS C++。

在 BittWare 的 Loopback 示例中,Parser 的使用方式有所不同。Loopback 使用了 Parser 的三個副本,而不是擴展元數據的一個副本。之所以采取這種方法,是因為Parser實際上相當小。

在基本上創建了兩個版本的數據包解析器后,我們注意到使用P4與HLS C++的一些差異。總的來說,HLS流的抽象性不如P4,但工具卻遠比P4成熟。

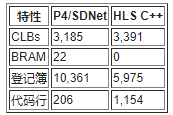

資源使用情況詳見下表。

你可以看到,在所有的FPGA資源中,HLS不是相似就是更好。雖然源代碼確實需要更多的行數,但其中一部分是受注釋和格式的影響。然而,HLS的C++實現確實總是要比P4需要更多的代碼行數。但這是針對數據包解析器/分類器而言的,屬于 P4 所能描述的范圍,而 HLS C++ 可以做得更多。HLS是非常通用的,幾乎可以做任何事情。P4是非常專業的。

更妙的是,既然有了HLS的實現,那么后續修改它以消化以太網協議的變化就和用P4語言修改差不多了。這是因為我們的HLS C++實現的結構是對我們創建的低級解析函數的調用序列。這種方法類似于直接操作位于P4語言下的運行時。

如前所述,回環實例的源代碼,包括它的解析器塊,可以通過BittWare開發者網站免費提供給Ultrascale++的用戶。它很好地說明了如何在HLS C++代碼中使用AXI接口。想看但沒有BittWare FPGA卡?請與我們聯系,了解哪里可以購買。

什么是數據包解析器?

在以太網上使用的協議對硬件來說是一個挑戰,要利用這些協議。這種挑戰的存在是因為協議有許多可選字段。例如,這些選項使查找IP頭的開始變得很復雜。 為什么這么說呢?在IP頭的情況下,前面可以有零、一個或兩個VLAN標簽。 也可以有MPLS標簽。因此硬件需要了解協議,剛好可以找到IP頭。硬件需要IP頭才能找到IP地址,而IP地址經常被用于硬件過濾器和表。類似的問題在下一級也存在,因為IP頭本身有可選的字段。

BittWare的HLS C++包解析器可以處理。

0至2個VLAN標簽(舊的SDNet代碼允許0或1)。

0到5個MPLS標簽(BittWare的舊SDNet代碼不識別MPLS)。

IP碎片

IPv4頭文件(不是IPv6

它假設在這些IP協議中找到端口ID。TCP、UDP、DCCP和STCP。

P4會不會成為FPGA硬件的通用?

P4語言是為了使用軟件定義“包轉發數據平面”(或網絡交換機)而創建的。該語言尤其與硬件廠商Barefoot Networks有關。P4語言與谷歌幫助推廣的名為“P4 Runtime”的東西不同。P4 Runtime提出了一個標準的運行時API,可以操縱由P4編譯的解決方案的控制平面。

P4確實可以很容易的為一個新協議定義一個數據包分類器/解析器。P4還指定了一套完整的表查找功能,它可以重寫流過的數據包,例如消除VLAN標簽。

這是否意味著P4的靈活性將導致FPGA的采用?我們認為有幾個理由反對這種情況發生。

在FPGA硬件上提供P4子集的商業選項是存在的,但是它們目前的范圍有限。此外,如前所述,由于商業條款的限制,BittWare很難利用這些條款來創建一個我們可以隨產品免費提供的示例程序。

需要注意的是,沒有任何真實世界的FPGA應用可以完全用P4編寫。例如,在一些例子中,跟隨我們的解析器的接收端縮放(RSS)塊不能用P4編寫。然而,HLS C++可以用來編寫任何一個塊,甚至是結合兩個功能的單個塊。

另外,P4表查詢函數基本上是用RTL或HLS C++編寫的硬件專用運行庫的封裝器。程序員可以直接從HLS C++中調用這樣的運行庫,而不會受到任何懲罰。

最重要的是,在使用P4和HLS C++兩種方法實現解析器后,我們實際上更傾向于HLS C++的方法。目前還不清楚FPGA上對P4的需求是否會增長到足以支持一個成熟的工具。HLS C++可以做得更多,也更成熟。

HLS的便攜性和結論

我們希望對FPGA上的兩個數據包解析器的實現進行解釋,一個是用P4語言,另一個是用HLS C++,希望對你評估正確的方法有所幫助。

最后一點是關于我們FPGA卡之間的可移植性。在基于Xilinx FPGA的卡之間,HLS提供了一個簡單的方法,幾乎不需要任何改變。如果要移植到基于英特爾的卡上,比如我們的520N-MX,則需要修改源代碼,特別是在兼容器的實用性方面。然而,基本概念是相同的。在這兩種情況下,我們都是基于我們對FPGA翻譯挑戰的了解來構建C++。任意的C++代碼在FPGA內運行效果會很差。然而,經過結構化并涂抹了實用程序的C++代碼卻能很好地運行。Xilinx或Intel所需要的改變非常相似,只是表達方式有些不同。

作為BittWare的SmartNIC Shell的一部分,我們的Parser可以幫助團隊快速上手,在我們的FPGA卡上構建網絡數據包處理應用。了解更多關于我們的卡的SmartNIC的信息,或與我們聯系,討論您的應用需求。

BittWare的Loopback例子重新部署了我們可以免費提供的SmartNIC shell的一個子集。這個子集包括我們的Parser庫。

審核編輯:郭婷

-

Xilinx

+關注

關注

71文章

2163瀏覽量

121012 -

服務器

+關注

關注

12文章

9021瀏覽量

85185 -

C++

+關注

關注

22文章

2104瀏覽量

73497

發布評論請先 登錄

相關推薦

華納云:服務器平均響應時間和數據包大小之間的影響

esp8266怎么做才能每秒發送更多的數據包呢?

使用AT SAVETRANSLINK時UDP數據包丟失怎么解決?

在Iphone4上運行UDP接收器,數據包丟失怎么解決?

能否在ESP結束之前通過串行端口停止傳入的UDP數據包的傳輸以解析下一個UDP數據包?

請問如何使用AT CIPSEND或AT CIPSENDBUF發送多個數據包?

如何在AIROC GUI上獲取良好數據包和總數據包?

請問高端網絡芯片如何處理數據包呢?

STM32H7接收數據包異常,一包接收的數據出現兩包發送的內容怎么解決?

CYUSB3013在ISO模式下配置設備時,最后一個數據包缺少LPF設置,這是為什么?

DPDK在AI驅動的高效數據包處理應用

構建BittWare的數據包解析器

構建BittWare的數據包解析器

評論