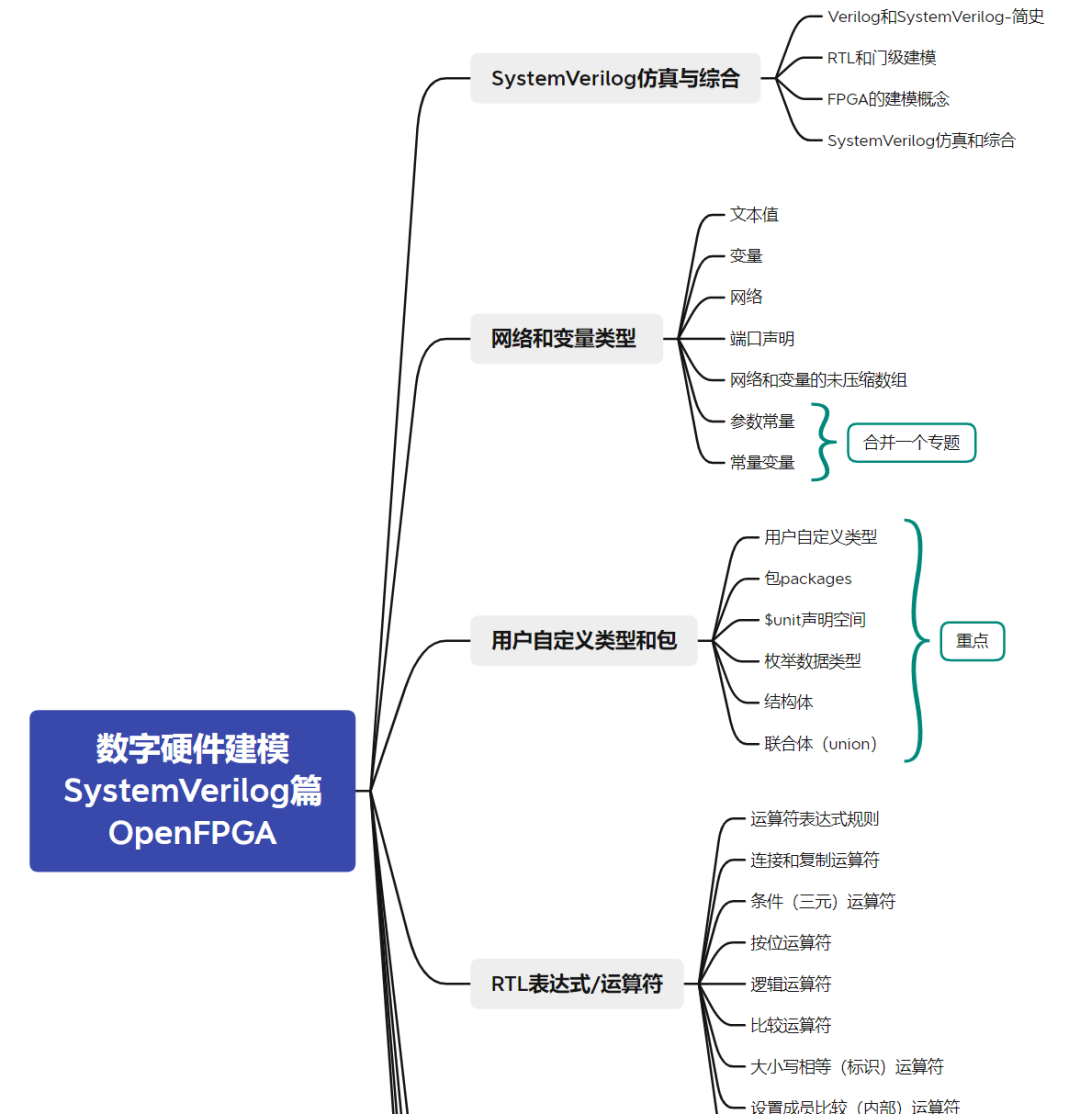

數字硬件建模SystemVerilog-條件(三元)運算符

經過幾周的更新,SV核心部分用戶自定義類型和包內容已更新完畢,接下來就是RTL表達式和運算符。

馬上HDLBits-SystemVerilog版本也開始準備了,基本這一部分完成后就開始更新~

介紹

RTL建模中廣泛使用的運算符是條件運算符,也稱為三元運算符,該運算符用于在兩個表達式之間進行選擇——表5-2列出了用于表示條件運算符的重點。

表5-2:RTL建模的條件(三元)運算符

| 運算符 | 示例用法 | 描述 |

|---|---|---|

| ?: | s?m:n | 如果s為真,則選擇m;如果s為假,則選擇n,否則(s不為真不為假)對m和n進行按位比較 |

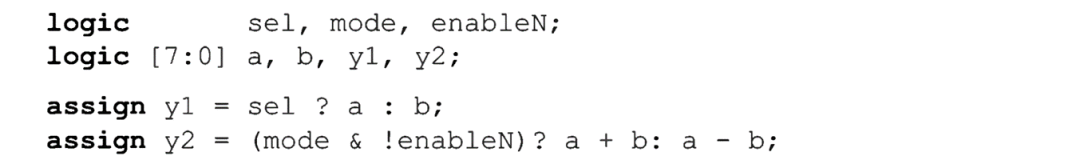

問號(?)前面列出的表達式被稱為控制表達式(control expression),表示它可以是一個簡單的整數值(任何大小的向量,包括1位),也可以是另一個返回整數值的操作的結果。例如:

使用以下規則將控制表達式計算為true或false:

如果所有位為l,則表達式為true。

如果所有位均為0,則表達式為false。

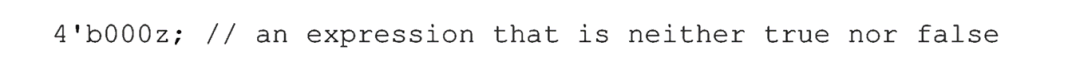

如果未設置任何位且并非所有位均為0,則表達式未知,如果某些位為X或Z,則可能出現這種情況。

對于4-state值,控制表達式可能既不是真的也不是假的。在下面的值中,沒有一個位是l,但不是所有的位都是0。

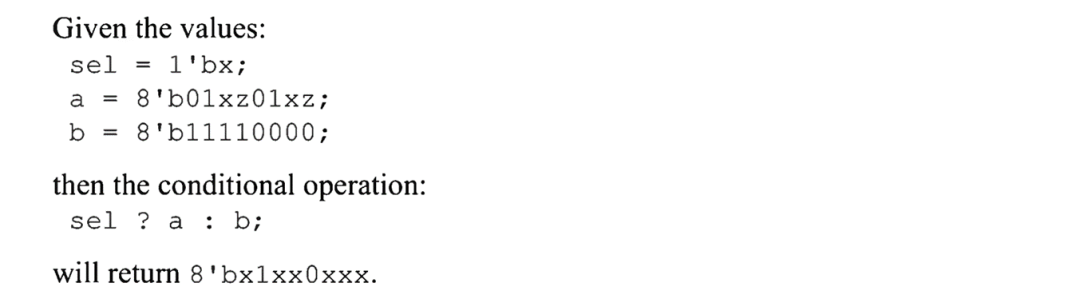

當控制表達式未知時,條件運算符對兩個可能的返回值進行按位比較。如果對應位均為0,則該位位置返回0,如果對應位均為l,則該位位置返回1。如果對應的位不同,或者任一位有X或Z值,則返回該位位置的X。下面的示例演示了這種仿真行為。

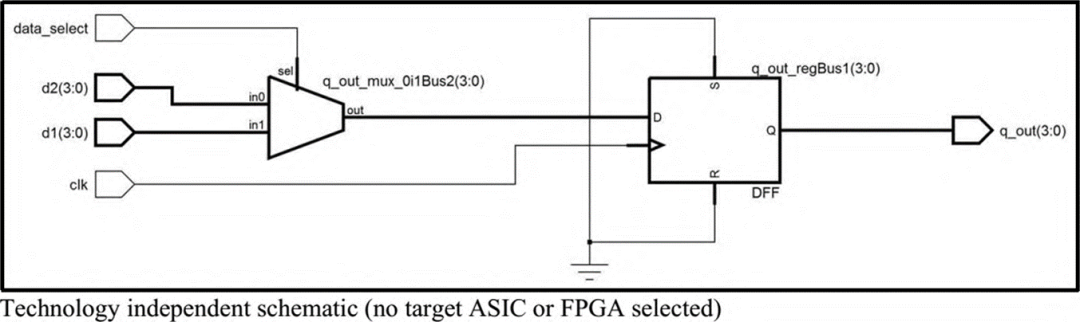

條件運算符的行為通常類似于硬件多路復用器。示例5-3說明了如何使用條件運算符在寄存器的兩個輸入之間進行選擇。圖5-3顯示了綜合該示例的結果。條件運算符映射到四個多路復用器,四位d1和d2輸入的每一位對應一個多路復用器。

示例5-3:使用條件運算符:4位多路復用寄存器D輸入

//4-bitregisterwithmultiplexedDinput,usingconditional //operator. // //`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords modulemuxed_register #(parameterWIDTH=4)//registersize (inputlogicclk,//1-bitinput inputlogicdata_select,//1-bitinput inputlogic[WIDTH-1:0]d1,d2,//scalableinputsize outputlogic[WIDTH-1:0]q_out//scalableoutputsize ); timeunit1ns;timeprecision1ns; always_ff@(posedgeclk) q_out<=?data_select??d1?:?d2;?????//?store?d1?or?d2 endmodule:?muxed_register //`end_keywords圖形5-3:示例5-3的綜合結果:條件運算符(多路復用寄存器)

圖5-3所示的電路是綜合編譯器將電路映射到特定ASIC或FPGA目標實現之前的中間通用綜合結果。用于生成圖5-3的綜合編譯器使用了具有未連接的set和rst輸入的通用觸發器,使用ASIC或FPGA庫的最終實現可能能夠使用沒有這些輸入的觸發器(如果目標設備中可用)。不同的綜合編譯器可能會使用不同的通用型組件來表示這些中間結果。

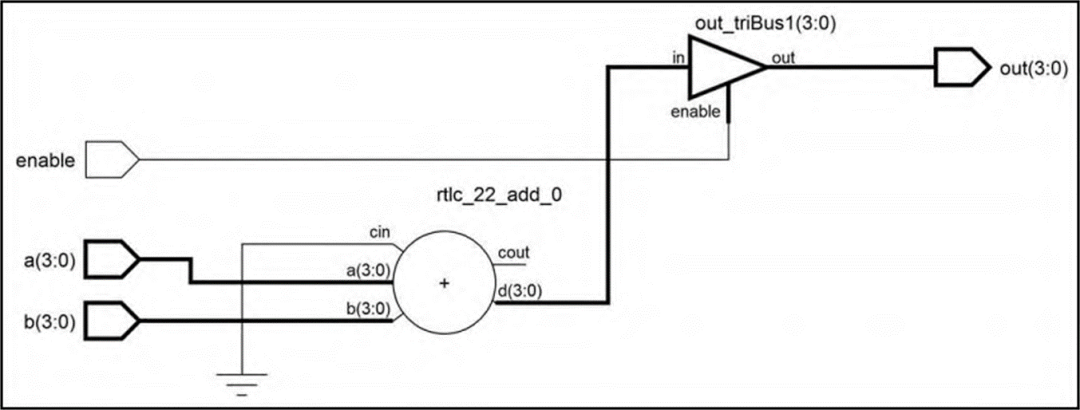

條件運算符并不總是作為多路復用器實現。綜合編譯器可能會根據操作數的類型和運算的上下文,將條件運算符映射并優化為其他類型的門級邏輯。在示例5-4中,條件運算符表示三態緩沖器,而不是多路復用邏輯,圖5-4顯示了綜合該示例的結果,

示例5-4:使用條件運算符:帶三態輸出的4位加法器

//4-bitadderwithtri-stateoutputs,usingconditionaloperator //(nocarry). // //`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords moduletri_state_adder #(parameterN=4)//N-bitaddersize (inputlogicenable,//outputenable inputlogic[N-1:0]a,b,//scalableinputsize outputtrilogic[N-1:0]out//tri-stateoutput,nettype ); timeunit1ns;timeprecision1ns; assignout=enable?(a+b):'z;//tri-statebuffer endmodule:tri_state_adder //`end_keywords

在本例中,條件運算符(?)選擇輸出端口應分配(a+b)或高阻抗。如果en為false,則將out賦值為z。’z標記是一個文字值,用于將表達式的所有位設置為高阻抗,并自動縮放到表達式的向量大小。有關向量填充文字值的更多詳細信息,請參見之前的文章。

在示例5-4中觀察,out三態輸出端口被聲明為3-state logic類型,而不是通常的邏輯類型,logic數據類型只定義端口時可以有四態值,它不定義端口類型是網絡類型或者變量類型。輸出端口默認為變量類型,除非顯式聲明為NET(網絡)類型。(相反,輸入端口將默認為NET類型,除非顯式聲明為變量類型),關鍵字?tri聲明網絡類型。tri類型在各個方面都與wire類型相同,但tri關鍵字可以幫助記錄網絡或端口的預期三態(高阻抗)值。

圖5-4:示例5-4的綜合結果:條件運算符(三態輸出)

SystemVerilog-連接和復制運算符

SystemVerilog-運算符/表達式規則

-

寄存器

+關注

關注

31文章

5250瀏覽量

119187 -

端口

+關注

關注

4文章

915瀏覽量

31856 -

運算符

+關注

關注

0文章

166瀏覽量

11013

原文標題:SystemVerilog-條件(三元)運算符

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

JAVA語言的運算符及表達式

關于C語言的運算符和表達式--筆記1

基于運算符信息的數學表達式檢索技術

SystemVerilog-運算符/表達式規則

SystemVerilog-運算符/表達式規則

評論