以下內容來源于EMC實戰特訓營部分問題解答,希望對大家有一些幫助。

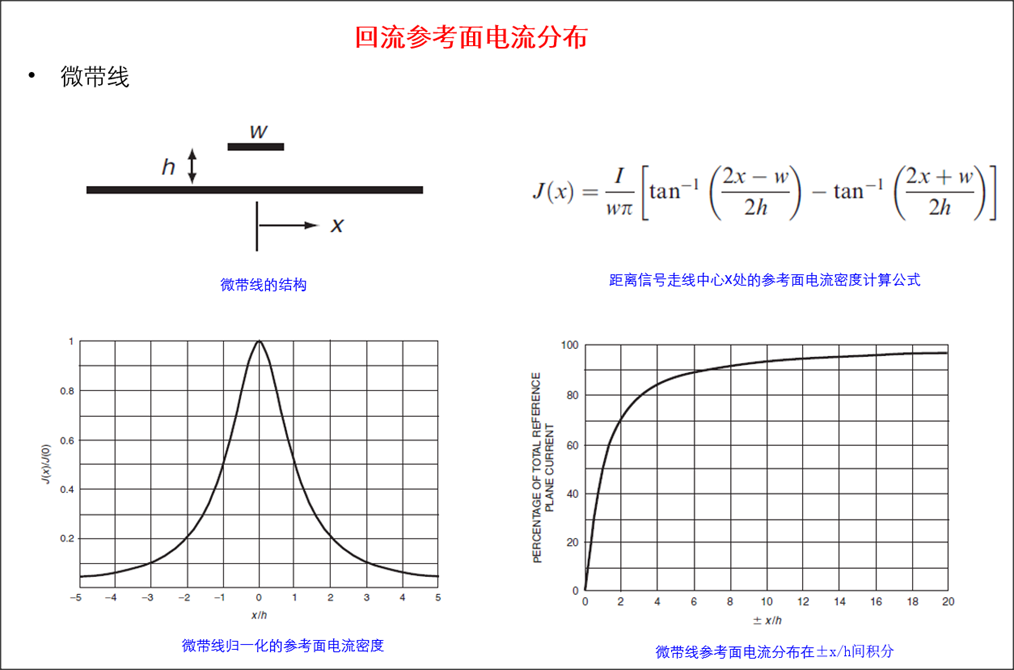

一、距微帶線中心范圍內回流百分比的數據的有理論計算公式嗎?如何凈IO的地-通過螺釘導電材料盡可能的接地,請問這個目的是為了降低接地阻抗嗎?

答:計算公式可以參考下圖所示,J(x)函數是微帶線的電流數值計算公式,公式來源于某技術論文。I/O凈地的方式就是如你所說的,盡可能降低接口區域的接地阻抗值。

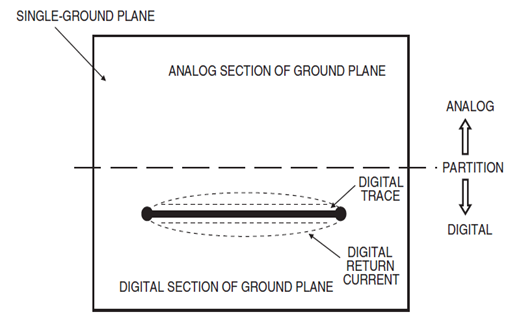

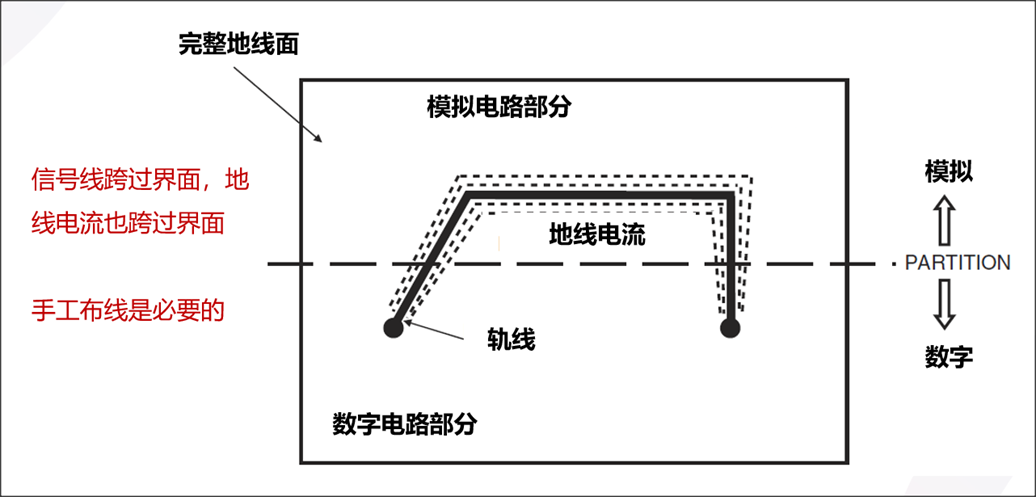

二、對于一些SOC型單片機,封裝很小,但同時處理數字和模擬信號分別有數字地、數字電源和模擬地、模擬電源。這時如何做數字和模擬的布局和走線?

答:這時可以不分地處理,但是在PCB走線時候要特別注意,主要避免數字信號可能對模擬信號的影響;主要參考如下圖所示的高頻信號回流原理,布線嚴格分區處理,這個知識點我們在PCB環節會重點講到。

三、產品設計中,接口部分的機殼地與信號地為什么要用1nF電容和1M電阻鏈接?這樣做有什么好處?

答:如下圖所示,這是我們電磁兼容設計中常用的一種處理方式,主要是針對信號地(GND)是浮地類型的產品。電阻的作用主要是擔心GND上在產品長期應用過程中會有靜電積累,如果沒有泄放通路可能會在薄弱區域形成瞬態擊穿,對電路造成損傷,所以采用大電阻的接地方式,既可以滿足產品的絕緣設計要求,又能避免ESD的積累損壞效應;電容的功能主要從EMI角度考慮,電容的使用,可以在高頻段實現信號地的接地連接,降低信號地與機殼地之間的高頻電勢差(這個電勢差常常是很多輻射問題的共模激勵源(天線知識中的單極子天線模型)),從而從PCB整體上降低電路的對外輻射值(特別是接口電路區域)。

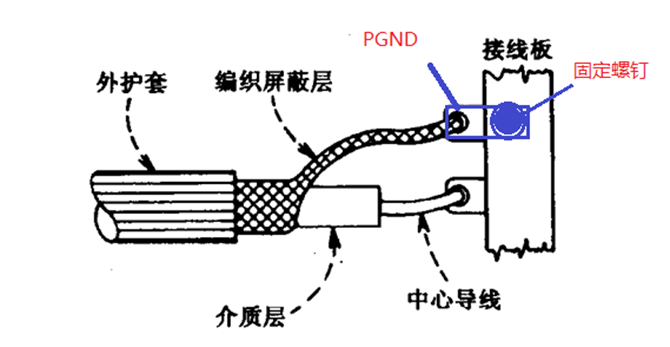

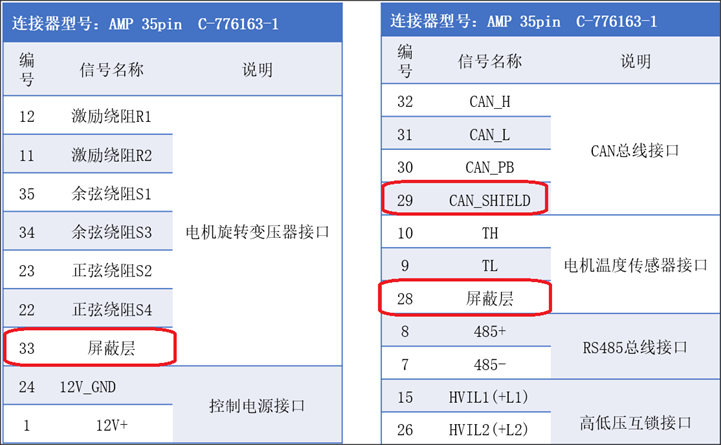

四、如果PCB地和結構地沒有進行濾波隔離,是一個地,這時候還需要將屏蔽層的地和信號地分開,分別接到結構上和PCB上嗎?

答:從EMC設計角度最好還是分開,因為即使是一個地,因為連接阻抗的原因,PCB上的GND和實際的結構體上的噪聲電平還是有差異的,如果屏蔽線連接到GND上,就如同很多資料中提到的豬尾巴效應;當然在一些實際產品的工程設計中,屏蔽層在工藝上很難實現單獨接結構件,那么就折中通過板內來實現接地,如汽車電子產品中常見的CAN。

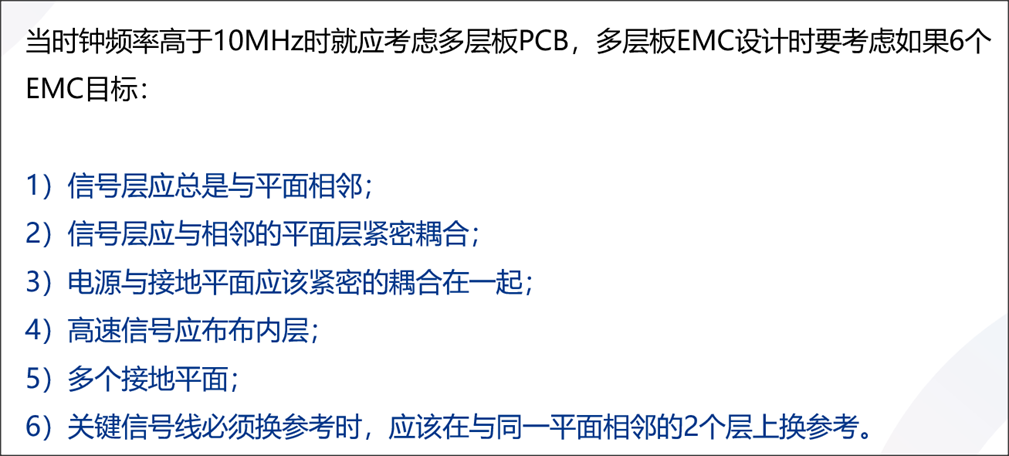

五、設計評估時,PCB層數多肯定好,但增加成本,請教一下從EMC角度,PCB板層數如何選擇,以到達最佳性價比?

答:這個知識點在后續的PCB課程中會有詳細講解,如果單純從EMC角度看層疊,下面六條設計原則都能滿足基本就是最佳的層疊設計方案了。

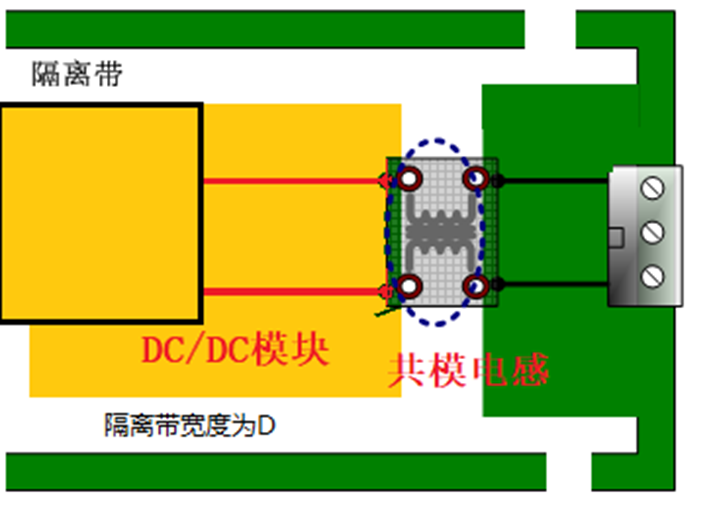

六、共模電感PCB布局時需要把共模電感周邊挖空,以四層板為例,只需要挖空第一層的?還是第二層,第三層,第四層全部挖空???另外如果沒有隔離帶,一般共模電感周邊挖空區域多少距離合適?

答:共模電感PCB設計主要是挖電感正下方區域,全部投影層挖空。目的是物理上減小地平面噪聲通過地與電感初次級(前后級)分布電容,使得干擾耦合,使得共模電感濾波效果打折。

七、能否解釋下共模電感的漏感為什么會對濾波效果有幫助?原理是什么?答:

共模電感是由兩個方向相反匝數相同的線圈按照一定規則繞制而成的特殊電感器,它的作用是濾除電路當中的共模電磁干擾信號,那么在實際當中為什么共模電感也能夠抑制差模信號?

漏感的產生

了解漏感之前先看一下共模電感的結構。共模電感有兩個繞組,而且兩個繞組被設計成使它們所流過的電流沿線圈芯傳導時方向相反,理論上彼此的磁場相互抵消。但是由于線圈繞制的環形有時候不能繞滿一周,或者繞制不夠緊密,那么磁就會泄漏出來。因為電感不可能是理想的電感,線圈繞完后,不可能所有磁通都集中在線圈的中心內。

漏感的利用

這種由于漏磁導致產生的電感我們稱為"漏感",其實這也就是差模電感。因此,共模電感一般也具有一定的差模干擾衰減能力。雖然產生了差模電感,但是也未必有害,在實際使用當中,有時候還特意設計利用漏感。例如在EMI濾波器中,只安裝一個共模電感,利用共模電感的漏感產生適量的差模電感,這樣起到對差模電流的抑制作用,相當于有共模電感也有一個小差模電感存在,從而達到更好的濾波效果。

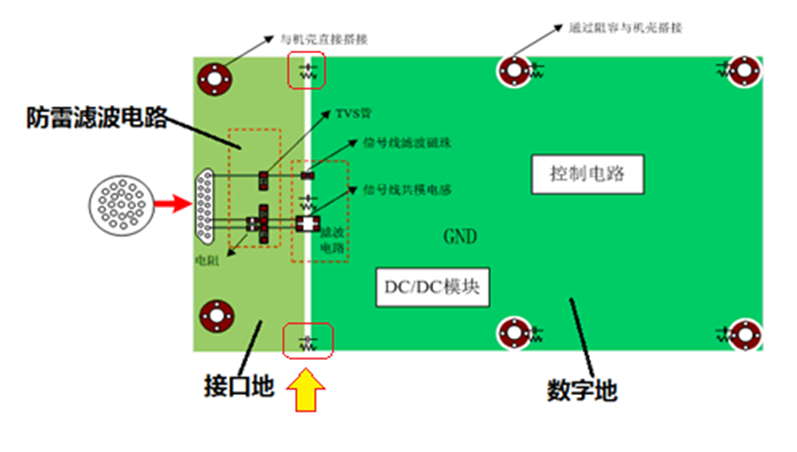

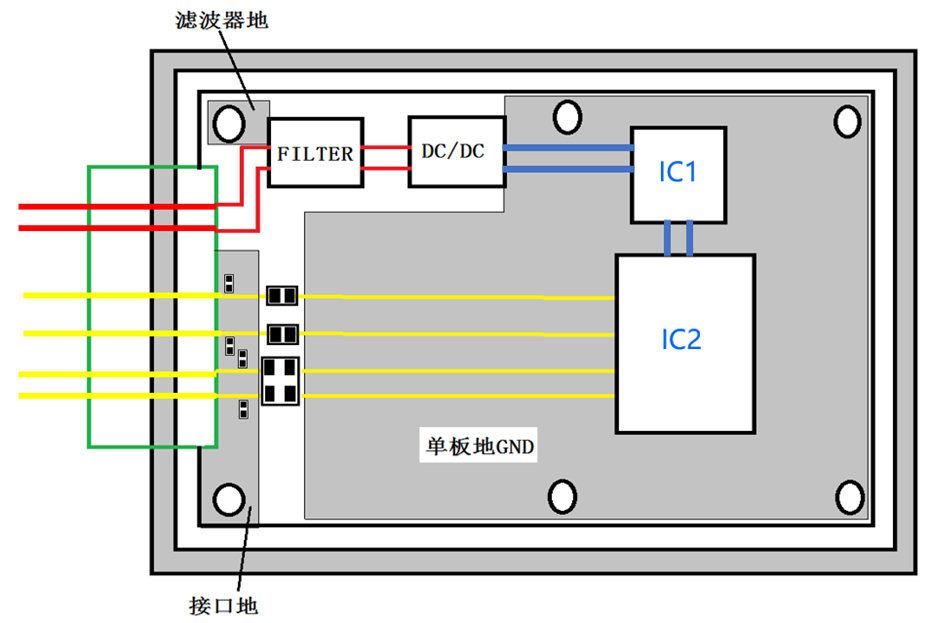

八、個具有金屬殼體的產品,其中有dcdc隔離。機殼地、凈地、電源地,數字地、模擬地。一般情況應該如何布局?需要注意考慮那些問題。

答:這個關于PCB布局設計后續有專門的PCB和接地設計章節會進行詳細描述,因為關于分地設計,接地設計牽涉到很多前提條件。另外還與產品是否是浮地設計、安規絕緣耐壓要求等相關。

下圖給一個類似的設計示意圖給參考:

九、課程里講各種濾波器件都要針對電路可能出現的干擾頻率進行選擇。那么請問老師對一款 DC DC,根據一般經驗,它的干擾頻率一般在那些頻段?我們一般選擇哪些頻段對它進行濾波?

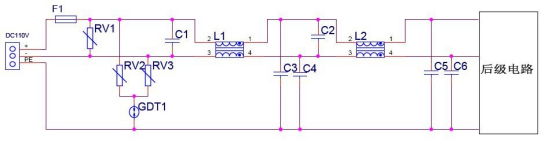

答:首先根據產品測試標準要求的頻段范圍,DC/DC 正常測試 CE,測試頻段范圍為 150KHz-30MHz(汽車電子產品到 108MHz),濾波器和防護設計是一個器件組合實現的過程!

一般電源類產品詳細濾波和防護設計在后續的濾波設計和防護設計專題中還會有詳細的講解,比如常規電源電路設計方案如下:

電路 EMC 設計說明:

電路濾波設計要點

L1、C1、C3、C4 組成第一級濾波電路。C1 為差模濾波電容,主要濾除差模干擾, 其濾波頻段覆蓋 150kHz-500kHz。C3、C4 為共模濾波電容,為共模干擾提供低阻抗回路,其濾波頻段覆蓋10MHz-30MHz。L1 為共模濾波電感,對共模干擾進行抑制,其濾波頻段覆蓋 10MHz-30MHz;L2、C2、C5、C6 組成第二級濾波電路。C2 為差模濾波電容,主要濾除差模干擾其濾波頻段覆蓋150kHz-500kHz。C5、C6 為共模濾波電容,為共模干擾提供低阻抗回路,其濾波頻段覆蓋 10MHz-30MHz。L2 為共模濾波電感,對共模干擾進行抑制,其濾波頻段覆蓋 10MHz-30MHz;L6、C10、C11 組成第二極濾波電路。C10、C11 為差模濾波電容, L6 為差模電感,主要濾除差模干擾;C9、C8 組成輸出端濾波電路。C9 為 4.7uF的電解電容,主要針對低頻噪聲的濾波,其值可根據測試情況進行調整;C8 為 1000pF的小電容,主要針對高頻噪聲的濾波,其值可根據測試情況進行調整;保護地與輸出端負極通過 1000pF 的電容 C16連接,主要為輸出端干擾提供泄流路徑;

電路防護設計要點 RV1、RV2、RV3、GDT1 組成第一級防護電路,其中RV1 進行差模防護、RV2、RV3、GDT1 進行共模防護。RV2、RV3、GDT1 防護器件會導致絕緣耐壓試驗不能通過,當接口需要考慮絕緣耐壓試驗時建議去掉 RV2、RV3、GDT1 三個元器件。

特殊要求 電路中所有的電容要符合安規的要求,差模電容選取耐壓值AC275V,共模電容選取 Y電容;保險絲 F1 位置要靠近接口放置。因壓敏電阻失效模式為短路,可能會造成大電流,因此需要增加保險絲。

器件選型要點 電路中Y 電容(C3、C4和 C5、C6)容值選取范圍為 100pF~4700pF,典型值選取 2200pF;電路中 X 電容容值取值范圍為 0.1μF ~10μF,C1 典型值為 0.22μF;C10 和 C11 典型值選取 0.68μF ;L1 為共模電感,感值取值范圍為100μH~30mH,典型值選取 15mH;L6 為差模電感,感值取值范圍為10μH~1mH,典型取值選取 47μH;RV1、RV2、RV3 壓敏電阻選擇壓敏電壓范圍466V~616V,典型值選取550V,壓敏電阻 RV1 的通流量(10 次沖擊)選擇大于等于 167A,壓敏電阻RV2、RV3 的通流量(10次沖擊) 選擇大于等于 167A;GDT1 氣體放電管選擇直流擊穿電壓為466V~616V,典型值選取 550V,通流量選擇大于等于 167A。以上元器件的取值后續可以根據實際的測試情況進行調整。

十、在案例講解中,老師憑借工程實踐經驗直接鎖定了干擾源頭;那對于沒有很豐富的工程實踐經驗的人來說,該怎么排查干擾源呢?一般排查感染源頭有什么方法呢?(非經驗方式的排查干擾源方法)

答:建議1:借助頻譜儀定位源頭,另外有特征的超標頻點;2:可以計算基頻,從而對應單板上的時鐘等周期信號;3:對于多系統組成,可以采取斷電方式排除分析出干擾源;

審核編輯:湯梓紅

-

單片機

+關注

關注

6032文章

44514瀏覽量

632962 -

pcb

+關注

關注

4317文章

23002瀏覽量

396236 -

emc

+關注

關注

169文章

3872瀏覽量

182864

原文標題:EMC工程問題解答(一)

文章出處:【微信號:EMCjishufuwu,微信公眾號:深圳市賽盛技術有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

新手-iPhone/touch常見問題解答

EMC工程問題解答(八)

關于EMC的問題解答

關于EMC的問題解答

評論