盡管數字技術占主導地位,但我們生活在一個模擬世界中。在域之間移動會引入量化誤差;這是不可避免的。工程師的工作是使這種轉換盡可能無縫,這就是 ADC 和 DAC 的用武之地。

模數轉換 (ADC) 可以采用多種形式并有許多折衷方案。從根本上說,關鍵的品質因數是準確性和速度。更復雜的是,這兩個參數通常是相反的。更高的精度需要更多的位,但增加更多的位會降低采樣率。更快的轉換通常以有效位數為代價。廣義而言,選擇是通過 Delta-Sigma 轉換拓撲(高分辨率、長延遲)或閃存轉換器(高速,但以功耗和面積為代價)。位于這兩個極端之間的是逐次逼近寄存器或 SAR 轉換器。這種“金發姑娘”技術在分辨率和速度之間提供了一個很好的折衷方案,但它也有其局限性。

一般來說,SAR 轉換器是無線通信中使用的模擬前端 (AFE) 的不錯選擇,這要歸功于它們兼具準確性和速度。隨著物聯網的范圍從核心進一步延伸,將邊緣永遠向外推,對能夠以更高頻率(因此更高采樣率)處理更復雜協議但功耗更低的 AFE 的需求不斷增長。讓我們不要將此稱為問題,而是將其稱為機會,在無線連接需要放入小到足以戴在耳朵里的東西中的時代,找到一種能夠實現更小、更快和更低功耗的 AFE 的技術,并且有可能成為由從其操作環境中收集的能量提供動力。

特區的一點背景

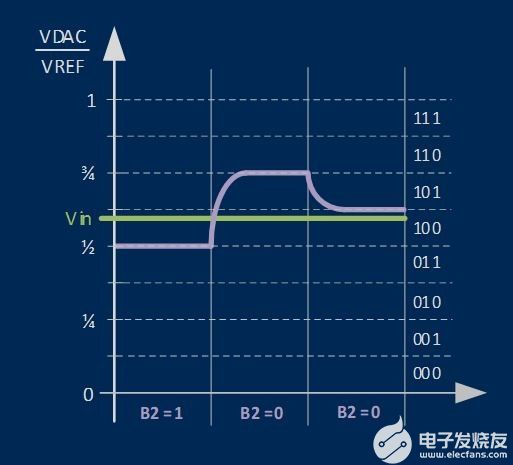

顧名思義,SAR 通過連續逼近模擬輸入的值來運行,迭代地將輸入電壓與重復減半的參考電壓進行比較,直到參考電壓和源之間的差異無法區分或滿足設計要求。每次比較都會產生一個“更高”或“更低”的結果,在數字輸出中形成一個位,從最高有效位開始。這種情況一直持續到轉換器以足夠的精度生成足夠的位來表示模擬輸入。

圖 1:3 位 SAR ADC 示例

由于所有步驟都需要在采樣周期內完成,因此可能的位數主要取決于電路中需要更改的元件的響應時間。這包括用于與輸入電壓(通常存儲在包含開關和電容器的采樣保持電路中)進行比較的參考電壓。反過來,該參考電壓(通常)由數模轉換器或 DAC 生成。因此,SAR 轉換器的采樣率將在一定程度上由用于生成參考電壓的 DAC 和控制邏輯決定,但通常 SAR 性能實際上受到比較器速度的限制。輸入端的開關電容實際上是一個低通濾波器,它引入了一個上限頻率閾值,但由于開關電阻低且電容小,這意味著轉換器通常可以處理數百 MHz 或更高的信號;特區的另一個積極特征。

就整體精度而不僅僅是分辨率而言,重要的是生成供 DAC 使用的參考電壓(而不是 DAC 生成的用于比較器的電壓)也要盡可能準確,因為所有其他測量都與這個。盡可能多地集成整個解決方案的 SAR,包括開關電容器 S&H 和 DAC 參考電壓發生器,將提供最佳性能。

克服 SAR 轉換器的限制

流水線 ADC 具有多個階段,每個階段都處理部分轉換過程。隨著每個階段完成其操作,它可以自由地接受下一個樣本。流水線 ADC 的主要優勢之一是它的速度。一旦管道完全準備好,它就可以隨著新樣本“推動”數據而產生新的輸出。雖然 SAR 的架構通常基于多次使用的單級,但流水線轉換器使用并行性來加快速度。

將 SAR 和流水線方法相結合產生了所謂的 SAR 輔助流水線 ADC。Adesto 的工程師已經實施了這種方法來創建一個 ADC,該 ADC 可以在高帶寬下以最高速度和精度運行,但需要最小的功率和面積。

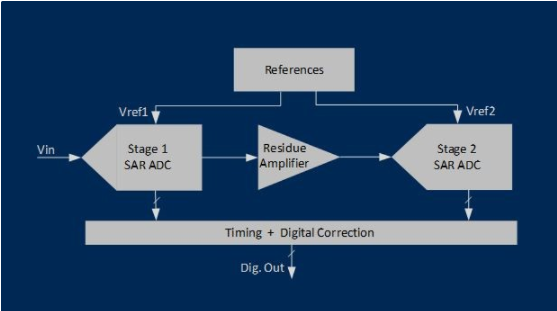

Adesto 開發的轉換器使用兩個 SAR 級;第一階段處理輸出的最高有效位,而第二階段處理最低有效位。通過添加一個數字模塊來處理定時和校正(參見圖 2),SAR 輔助流水線轉換器可以在不到同類 SAR 轉換器一半的時間內生成結果,而不會產生與傳統流水線 ADC(包括物理尺寸和功耗)。

圖 2:SAR 輔助流水線 ADC 架構

簡單來說,只要第一個 SAR 階段完成轉換,它就可以接受一個新樣本,而第二個 SAR 階段完成第一個樣本的轉換。級之間放大器的增益放寬了對第二個 SAR 的要求,從而產生了比 SAR 本身更節能的解決方案。

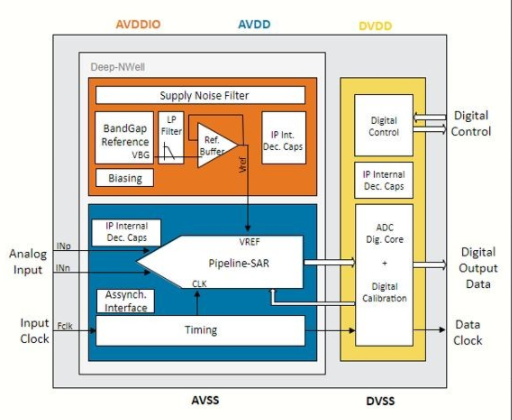

圖 3 顯示了 Adesto 的 SAR 輔助管道 ADC 的框圖。

圖 3:Adesto 的單通道 SAR 輔助管道 ADC

如圖 3 所示,Adesto 開發的 IP 包含所有關鍵功能,包括參考電壓發生器、定時和控制邏輯、數字校準以及去耦電容器。對所有模擬模塊使用深 n 阱技術可提供對襯底噪聲的抗擾度,當客戶在可能沒有專用模擬電源可用的設計中授權使用 IP 時,這一點尤為重要。該設計真正全面,因為它不需要外部電壓基準或穩壓器。

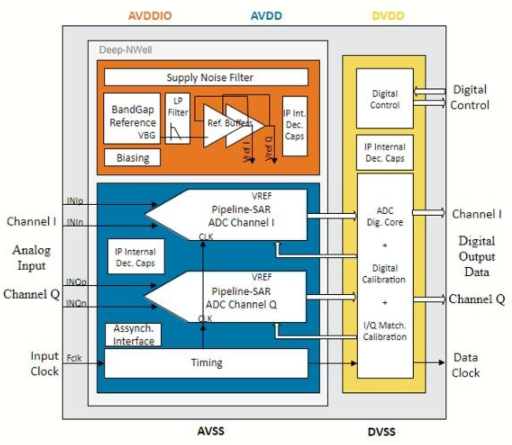

相同的內核 IP 已用于開發針對正交 I/Q 調制架構的雙通道解決方案(圖 4)。可以看出,一些功能可以在兩個通道之間共享,同時包括單獨的參考緩沖器和時鐘樹,以最大限度地減少通道之間的串擾。

圖 4:Adesto 的雙通道 SAR 輔助管道 ADC

這種方法提供的主要優勢之一是其低功耗運行。Adesto 部署在現已上市的批量 IP 中,包括采用 28nm 工藝的雙通道解決方案,在每個通道上提供 160Msamples/s,總功耗僅為 18mW。該 ADC 的總芯片面積僅為 0.055mm2,因此具有極高的面積效率。盡管具有這種集成度,但它可以提供 63.1dB 的 SNDR,并且通道之間的串擾低于 -80.0dB。

同一轉換器的八通道版本可以同時處理四個 I/Q 通道,以 122.88Msamples/s 的速度運行,同時仍僅耗散 45mW。它的有效位數 (ENOB) 為 10.2 位,但仍只需要 0.3 平方毫米的芯片面積。Adesto 還可以提供 12 位 SAR 輔助流水線 ADC,在僅 0.05mm2 的裸片面積上實現 200Msamples/s 的采樣率、10mW 的功耗。

AFE 嚴重依賴 ADC 的性能,而不起眼的 SAR 是工程師可用的最可靠和最通用的架構之一。這只是 Adesto 提供的 IP 的一個示例,該 IP 已經過優化以滿足最新應用程序的需求。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8627瀏覽量

146869 -

SAR

+關注

關注

3文章

414瀏覽量

45899 -

adc

+關注

關注

98文章

6438瀏覽量

544098

發布評論請先 登錄

相關推薦

低功耗毫米波雷達解決方案使電池供電類接近感應產品實現新功能

適合低功耗 HMI 按鈕應用的 LDC2112/LDC2114 電感應觸控解決方案數據表

ADS7813低功耗、16位采樣模數轉換器(ADC)數據表

華普微低功耗藍牙技術及解決方案

功耗優化的片上系統(SoC)解決方案,引領低功耗藍牙與2.4GHz應用新潮流

芯原低功耗藍牙整體IP解決方案已通過LE Audio全部功能認證

芯原低功耗藍牙整體IP解決方案已通過LE Audio全部功能認證

新思科技VC LP Advanced靜態低功耗驗證解決方案

低功耗嵌入式計算解決方案:選擇處理器的幾個關鍵因素

低功耗快速采樣的解決方案

低功耗快速采樣的解決方案

評論