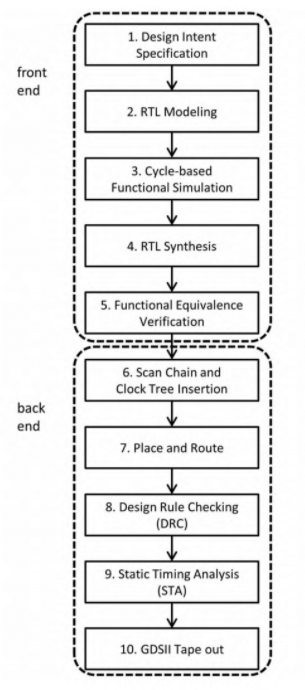

1、ASIC設計流程

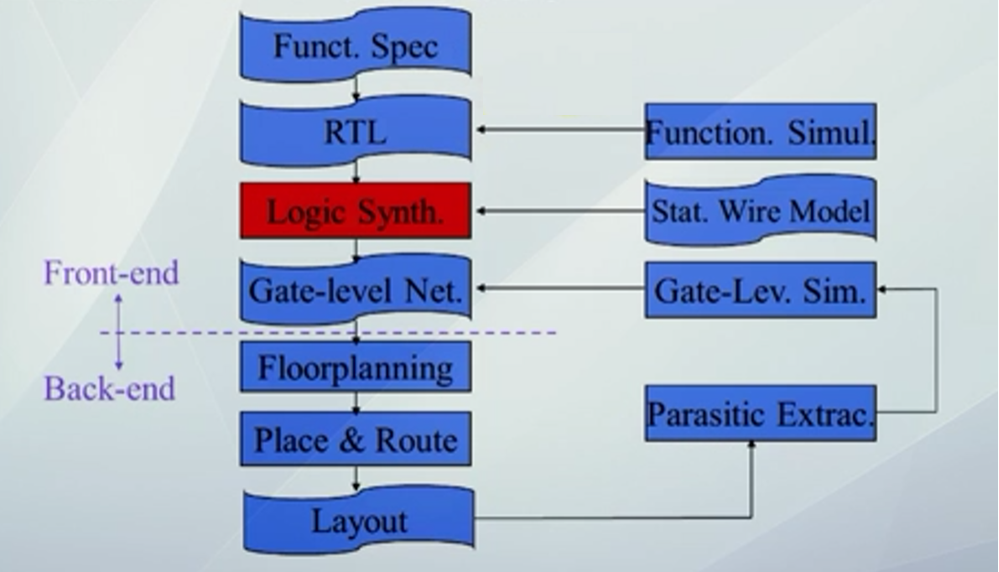

ASIC(專用集成電路)的設計如下,Front-end部分是前端設計,Back-end部分是后端設計。

圖片來源:學堂在線《IC設計與方法》

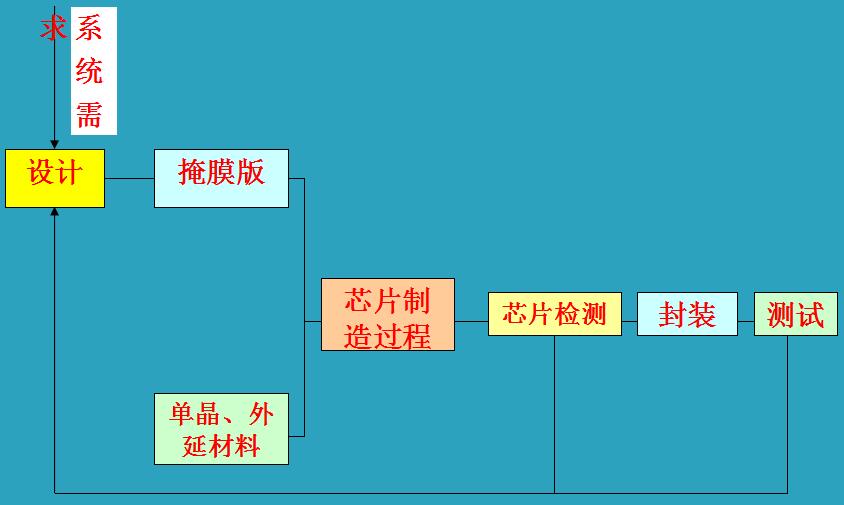

Funct.Spec代表設計需求,在具體設計需求提出后,編寫RTL代碼(Verilog代碼設計電路的一種設計類別);RTL代碼編譯完成,進行Function.Simul,即仿真;仿真結束后,進行邏輯綜合(Logic Synth.),將Verilog代碼轉化為電路,術語稱該電路為門級網單(Gate-Level Net.)。

邏輯綜合(Logic Synth.)過程需要約束(Stat. Wire Model)以產生規定條件下的電路。具體電路設計完成后,需進行門級仿真(Gate-Lev.Sim),以檢查電路設計是否出現失誤。

門級網單確定后,進入后端設計。首先是布局規劃(Floorplanning),擺放門級網單中的各個元器件位置。然后是布局和布線(Place&Route),將各個元器件連接。最后產生電路的版圖(Layout)。

在將電路的版圖加工制造前,為防止后端設計失誤,需要進行驗證。驗證前需提取版圖的寄生參數(Parasitic Extrac.),寄生參數包括導線的寄生電容、寄生電感、寄生電阻,寄生參數會造成信號傳輸延時、失真、干擾。驗證中,將寄生參數反標到門級網單上,再次做門級仿真(Gate-Lev.Sim)。最終的仿真結果沒有問題后,電路版圖可以用于加工制造。

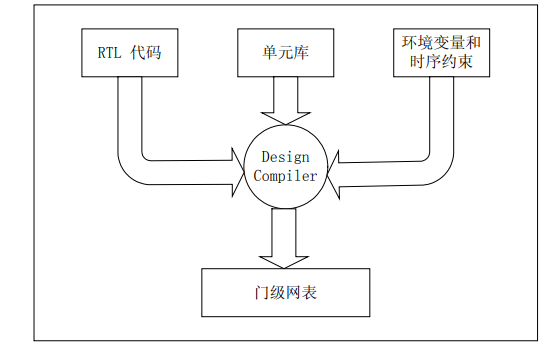

2、邏輯綜合

芯片代碼仿真的下一步是邏輯綜合,邏輯綜合將Verilog代碼轉化為電路圖。邏輯綜合的目的是決定門級結構,尋求時序、面積、功耗的平衡。尋求平衡的方式有兩種:約束驅動和路徑驅動。

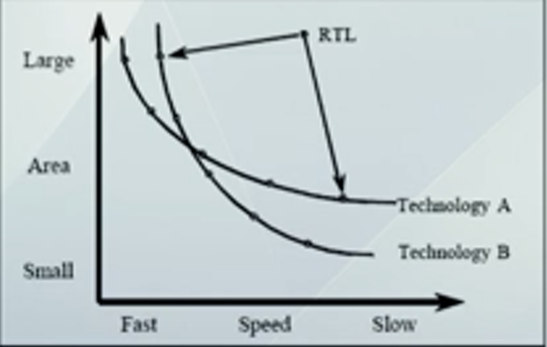

約束驅動是平衡面積和速度的方式。一個廠家(如TSMC)的一種工藝條件(如0.18um工藝)下,芯片的速度快和面積小相互制約,速度更快的芯片需要更大的面積,面積更小的芯片速度更慢。不同廠家的同種工藝面積和速度的制約程度不一定相同,有經驗的設計人員可以選擇合適的廠家尋求最優的面積和速度。

圖片來源:學堂在線《IC設計與方法》

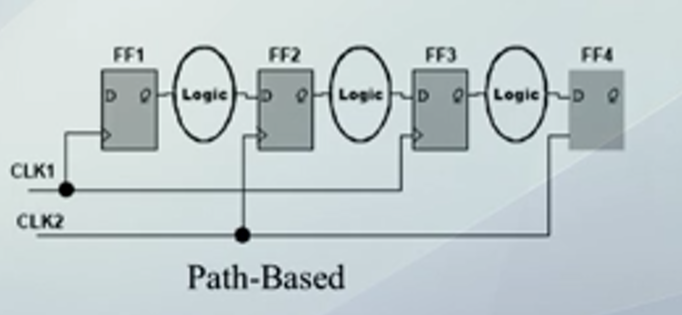

路徑驅動是將電路中的元器件以最優的方式連接。

圖片來源:學堂在線《IC設計與方法》

邏輯綜合過程可運用預先設計完成的邏輯單元,提高設計效率。邏輯單元包括標準單元和宏單元。標準單元的尺寸有一定的標準,包括基本門電路、寄存器等。宏單元功能相對復雜,難以在固定高度內安裝,包括RAM存儲器、ROM存儲器、數值運算單元等。

標準單元的名稱詳細,如ARM UMC L180GⅡ 1.8V標準單元庫表示:由ARM公司(個人理解:設計公司)提供的,針對UMC(聯華電子公司,個人理解:制造公司)廠家的,針對邏輯工藝的,180nm(0.18um)的,GⅡ工藝的,1.8V的標準單元庫。

標準單元包括元器件數量多,ARM UMC L180GⅡ 1.8V標準單元庫包含124種元器件,數量為470個。

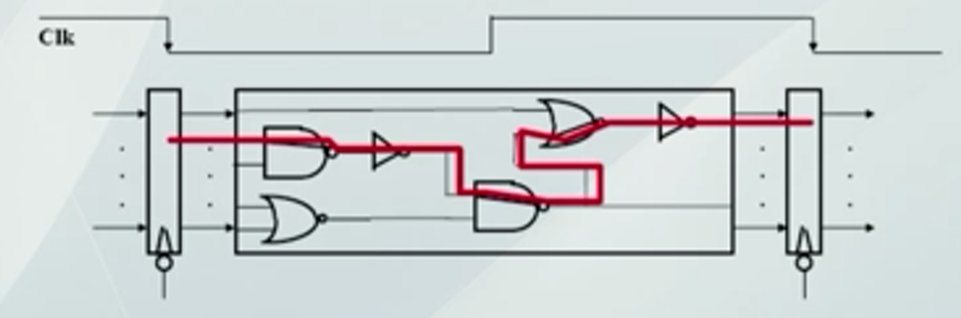

邏輯綜合過程還需進行靜態時序分析。靜態時序分析的前提是觸發器使用同一時鐘,即全同步電路。靜態時序分析的準則為:

時鐘周期>Clockto Q+穿越組合邏輯電路的最長延時+Set up

其中Clock to Q是時鐘沿出現到觸發器輸出信號的延時,Set up時間是下一級觸發器輸入信號穩定建立的延時。

圖片來源:學堂在線《IC設計與方法》

當靜態時序分析的準則成立時,時序邏輯電路可以穩定工作。

審核編輯 :李倩

-

集成電路

+關注

關注

5382文章

11396瀏覽量

360953 -

asic

+關注

關注

34文章

1195瀏覽量

120347 -

仿真

+關注

關注

50文章

4048瀏覽量

133431

原文標題:芯片設計相關介紹(23)——ASIC設計流程和邏輯綜合

文章出處:【微信號:行業學習與研究,微信公眾號:行業學習與研究】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

典型的基于RTL的ASIC設計流程分析

ASIC邏輯綜合及Synopsys Design Compi

ASIC與大型邏輯設計實習教程

面向ASIC和FPGA設計的多點綜合技術

ASIC邏輯綜合及Synopsys Design Compiler 的使用資料說明

芯片設計之ASIC設計流程和邏輯綜合

芯片設計之ASIC設計流程和邏輯綜合

評論