寫文字之前,兩個(gè)背景交代一下:

1.前文講過(guò)USB3.0 的基礎(chǔ)知識(shí),可以先了解一下。

2.關(guān)于知識(shí)體系框架圖(設(shè)計(jì),仿真,測(cè)試),先有個(gè)概念。

言歸正傳。

1、Pre-Layout(先期布局

需要信號(hào)完整性工程師評(píng)估USB 接口擺放位置是否符合。是否符合取決于鏈路的情況,也就是鏈路評(píng)估。

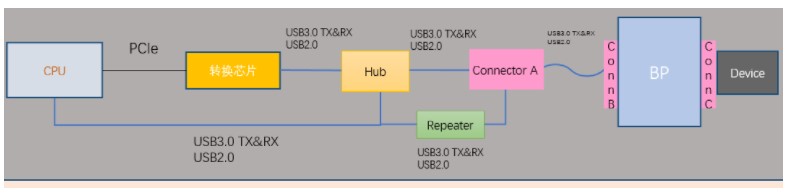

關(guān)于USB的鏈路,先要搞清楚USB 的拓?fù)浣Y(jié)構(gòu),一般來(lái)自于前文中所說(shuō)的4種拓?fù)浣Y(jié)構(gòu)之一。下圖為一個(gè)綜合的鏈路形式:

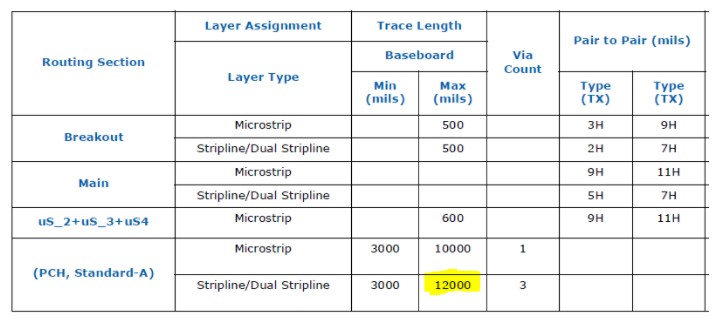

舉個(gè)例子,選用簡(jiǎn)單的一種拓?fù)浣Y(jié)構(gòu)來(lái)做一種推算:

1.根據(jù)USB接口位置,預(yù)估線長(zhǎng)為Y。

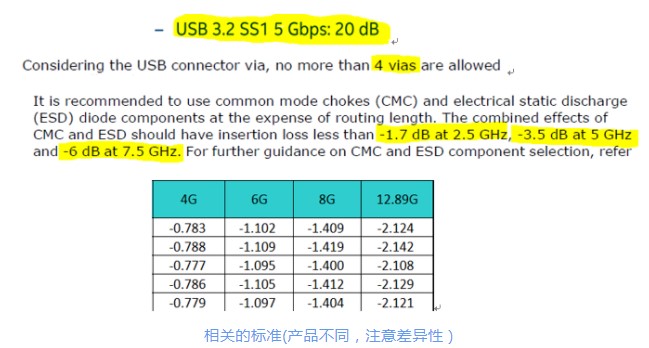

2.鏈路閾量。

4 dB (Package)+ 2 dB (PTH Connector)+ 0.3 x 4 (Via) + 3.5 dB (CMC&ESD) = 10.7 dB

(20-10.7)/0.9 =10.33 inches

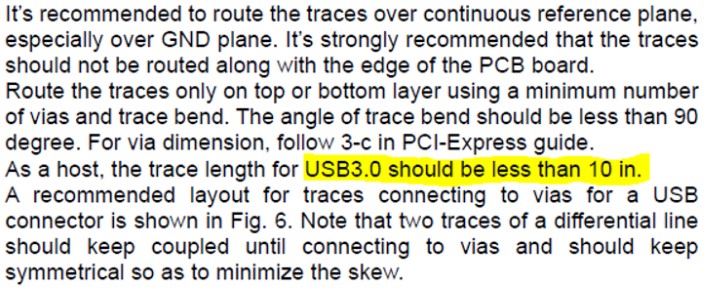

所以有些芯片DG給出的參考值 10 in。

有的小伙伴立馬舉手,說(shuō):我看到有些DG給出的是12 in。

這個(gè)是因?yàn)榘宀牡膮^(qū)別(FR4 & Mid Loss)。

線長(zhǎng)的最大長(zhǎng)度除了受板材因素的影響,還有疊層和銅箔,都會(huì)影響。

2、版圖檢查

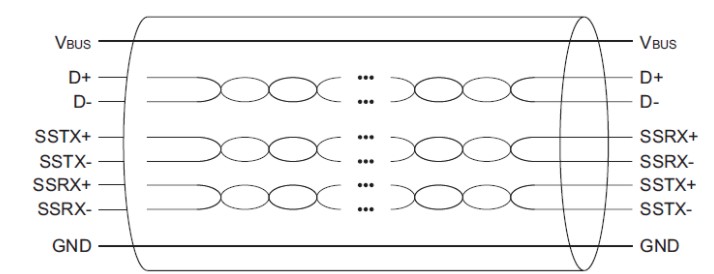

1.我們需要關(guān)注的信號(hào)是哪些,USB3.0信號(hào)圖:

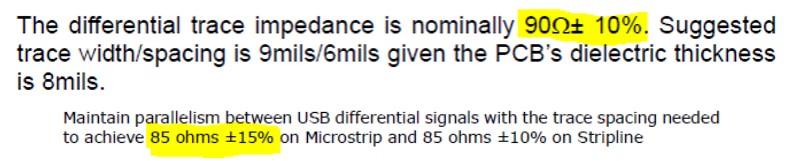

2.信號(hào)的阻抗:

阻抗的值根據(jù)產(chǎn)品鏈路的實(shí)際情況,做好阻抗匹配。

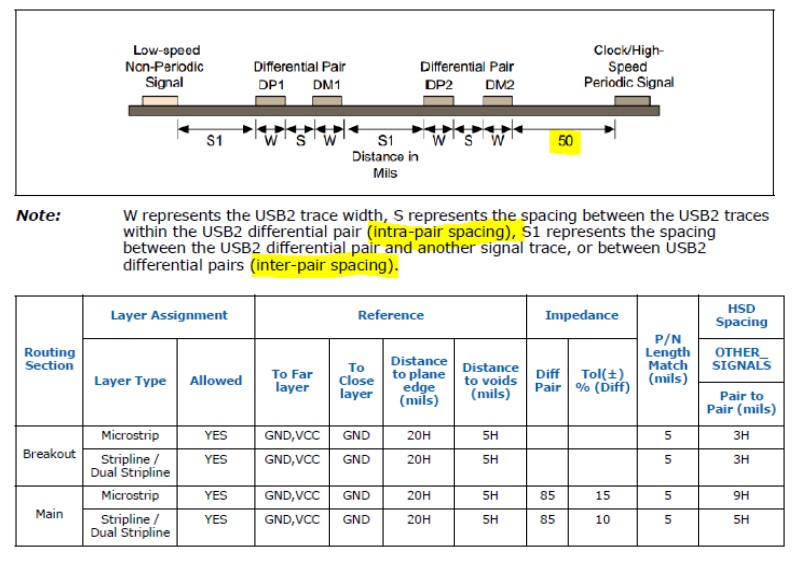

3.Layout

列舉部分,以產(chǎn)品設(shè)計(jì)的checklist為準(zhǔn)。

分清楚 Intra-pair spacing & Inter-pair spacing

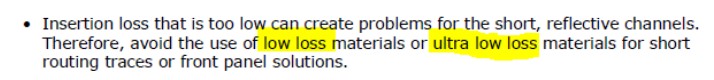

重讀Design guide 發(fā)現(xiàn)有意思的一點(diǎn):

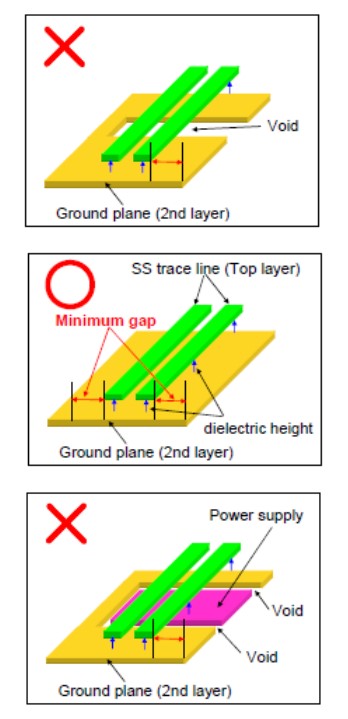

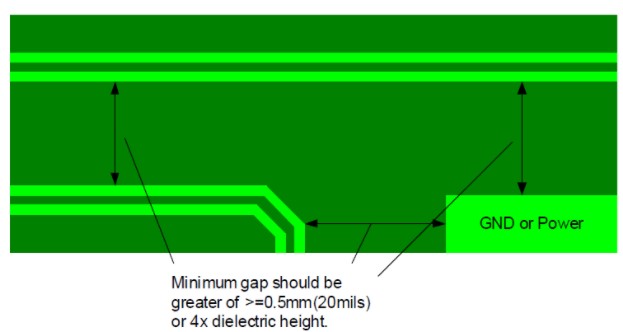

參考層完整性:

注:參考平面的改變,要加stiching via

避免串?dāng)_(Crosstalk)

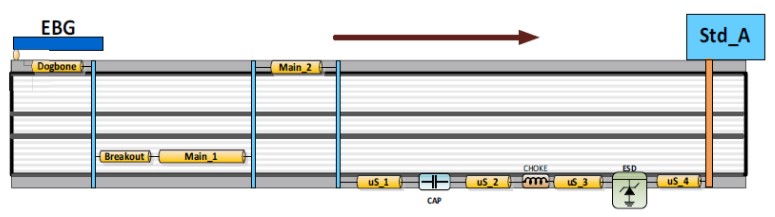

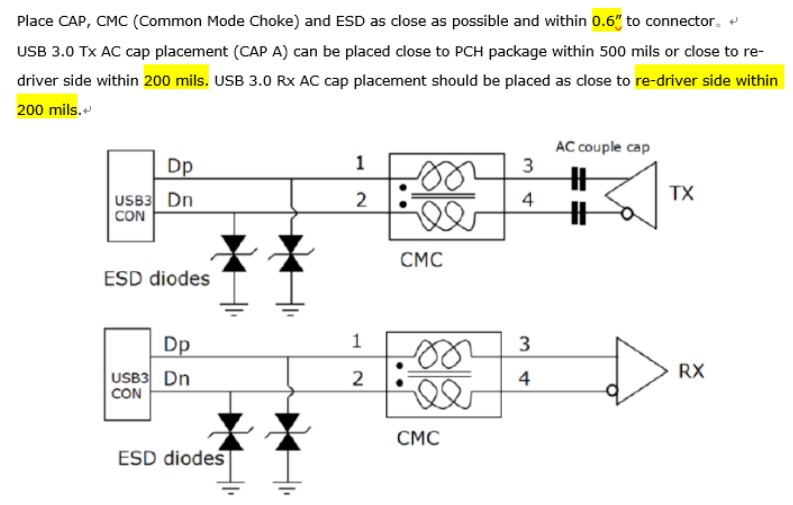

4.鏈路上器件的擺放:

關(guān)于CAP位置擺放標(biāo)準(zhǔn),之前有做過(guò)相關(guān)的仿真,只要不擺放在鏈路的中間位置,盡量靠近發(fā)送端或接收端擺放都可以。

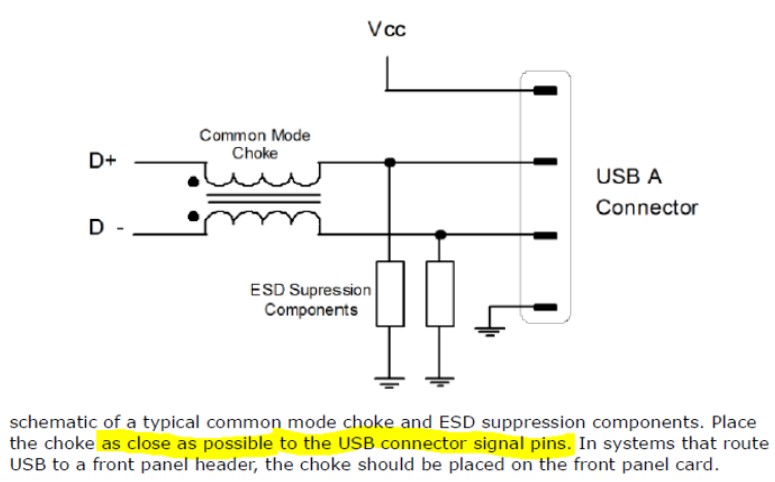

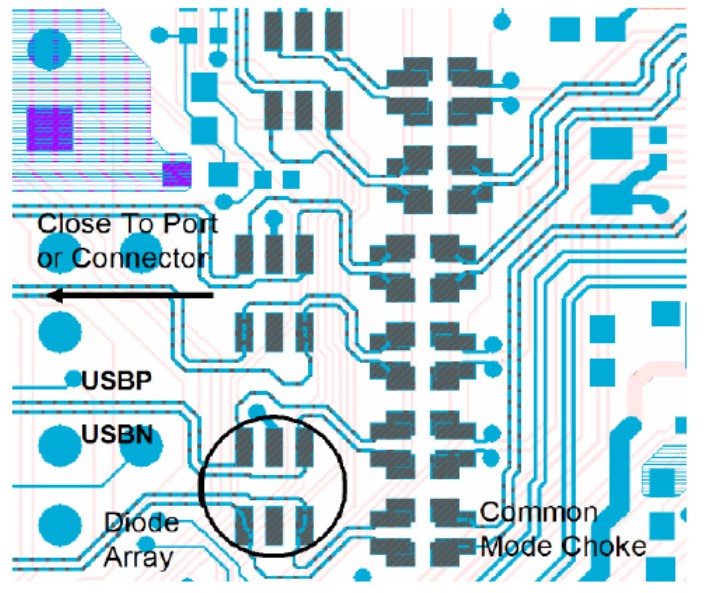

CMC(Common mode chokes)

ESD diode加在USB 信號(hào)路徑,增大了寄生電容,影響了信號(hào)質(zhì)量。版圖設(shè)計(jì)可以參考如下優(yōu)化。同時(shí)注意器件擺放層,減小stub。

5.電源部分:

電源部分的Power fill按照1.5 A 的閾量預(yù)估。電源部分牽扯到USB droop和IR drop的測(cè)試。還有電源路徑的PDN的知識(shí)點(diǎn)。這里面就不做展開。

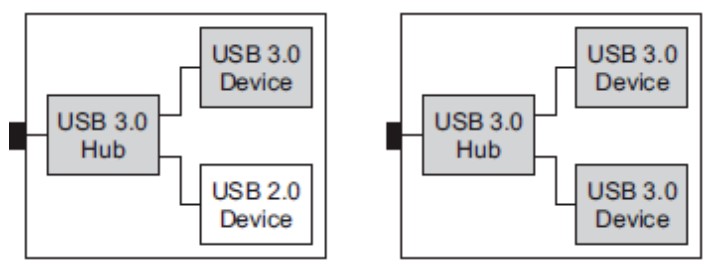

6.Hub部分:

Hub有USB3.0&USB2.0之分

7.Repeater(Re-driver&Re-timer)

擺放位置也沒(méi)有明確說(shuō)明,也是盡量靠近終端。

一般來(lái)說(shuō),就是調(diào)節(jié)均衡的設(shè)置,改善信號(hào)的上升時(shí)間和眼高的幅值,就不展開說(shuō)了,參照使用手冊(cè)。

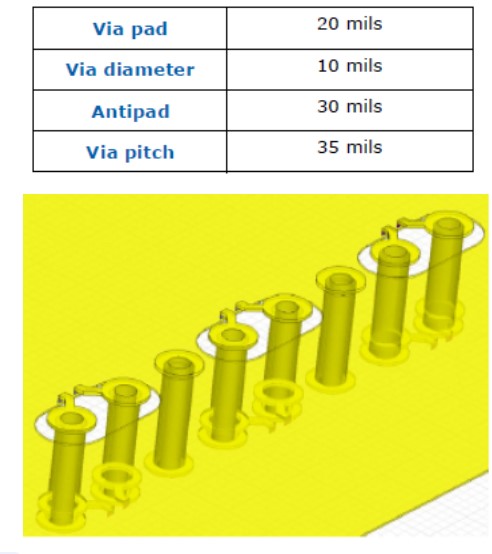

8.Differential Via

阻抗突變,注意優(yōu)化。

3、總結(jié)

這邊只拿一個(gè)簡(jiǎn)單的拓?fù)浣Y(jié)構(gòu)進(jìn)行梳理,其他的鏈路中有redriver ,經(jīng)過(guò)Hub轉(zhuǎn)換,有Cable連接等各種的情況,不同的拓?fù)浣Y(jié)構(gòu),具體情況分別評(píng)估,這里只做個(gè)拋磚引玉,就不一一展開了。

審核編輯:劉清

-

ESD

+關(guān)注

關(guān)注

48文章

2012瀏覽量

172733 -

USB接口

+關(guān)注

關(guān)注

9文章

699瀏覽量

55574 -

寄生電容

+關(guān)注

關(guān)注

1文章

291瀏覽量

19192 -

USB信號(hào)

+關(guān)注

關(guān)注

0文章

6瀏覽量

6506 -

CAP

+關(guān)注

關(guān)注

0文章

16瀏覽量

2077

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

構(gòu)建系統(tǒng)思維:信號(hào)完整性,看這一篇就夠了!

信號(hào)完整性仿真應(yīng)用

【信號(hào)完整性工程師】和【硬件測(cè)試工程師】

分享資深硬件工程師視頻講解信號(hào)完整性原理

信號(hào)完整性為什么寫電源完整性?

28小時(shí)從數(shù)字電路工程師到信號(hào)完整性工程師

什么是信號(hào)完整性

ESD保護(hù)時(shí)怎樣維持USB信號(hào)完整性

信號(hào)完整性SI工程師必須具備什么條件

信號(hào)完整性工程師工作職責(zé)

信號(hào)完整性工程師的最佳伴侶_圖書推薦

信號(hào)完整性工程師總結(jié)的精華100例

信號(hào)完整性為什么寫電源完整性?

什么是信號(hào)完整性?

信號(hào)完整性工程師眼里的USB信號(hào)該做什么?

信號(hào)完整性工程師眼里的USB信號(hào)該做什么?

評(píng)論