前面講過反射,講過損耗。接下來講串擾(Crosstalk)。

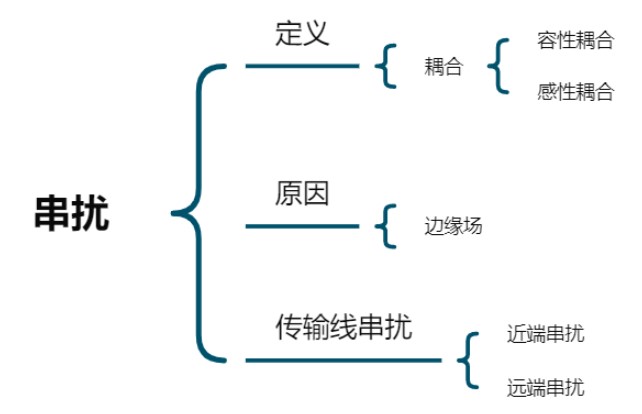

話不多說,直接上圖,串擾的分類:

一個網絡傳遞信號,有些電壓和電流通過網絡之間的耦合(容性耦合和感性耦合),傳遞到相鄰網絡,這就是串擾。

對于相鄰網絡而言,不管給什么,不是想要的,都會以噪聲的形式耦合過來。

串擾與網絡的信號路徑及返回路徑與另一個網絡的信號路徑及返回路徑都有關系。

這里面有概念的東西:動態線網&靜態線網;攻擊線網&受害網絡。

既然說是網絡之間的耦合(Coupling),那什么是耦合?

耦合簡單來說就是能量從一個介質(PCB板,金屬導線等)傳播到另一種介質。

耦合分為容性耦合和感性耦合。

實際的工作中,該怎么考慮?或者說哪一種耦合更要注意,也分兩種情況:

均勻傳輸線且有均勻很寬的返回路徑,容性耦合和感性耦合相當;

非均勻傳輸線,比如接插件或封裝的場合,感性耦合占主導地位。這里面要注意開關噪聲(SSN):開關噪聲大多發生在插件、封裝和過孔處,耦合電感很大。

地彈就是返回電流重疊出現的一種特殊情況。

導線中有電流產生,就會有圍繞在信號路徑和返回路徑導體周圍的磁力線圈。由于信號路徑和返回路徑之間的空間是不封閉的,所以會延伸到周圍的空間,這個延伸出去的空間稱之為邊緣場。

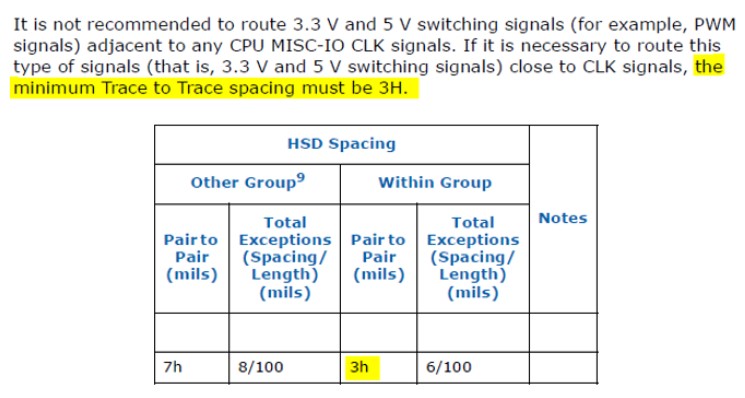

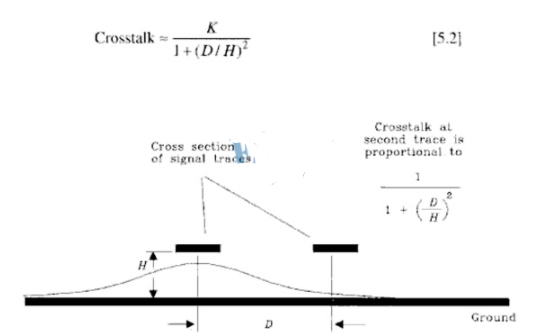

既然是所謂的邊緣場引起的串擾,那么越遠,受的影響就越小。惹不起還躲不起嘛,離它們遠遠的,簡單粗暴。話是這樣說,實際工作中,PCB板走線的密度限制,不可能給你想要的空間。怎么辦?

Intel的規范給出了一個HSD組內的間距還有普通線之間的間距,都是3H。

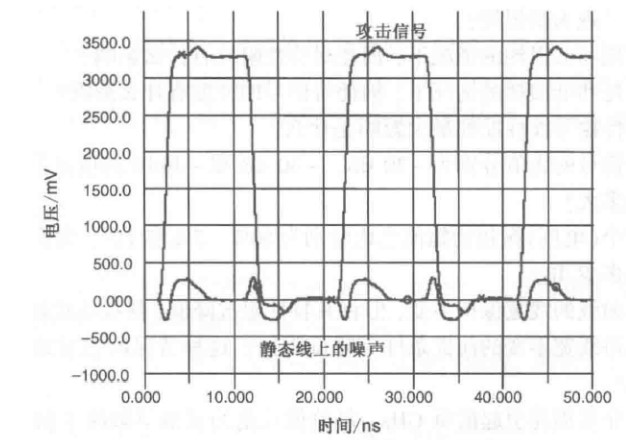

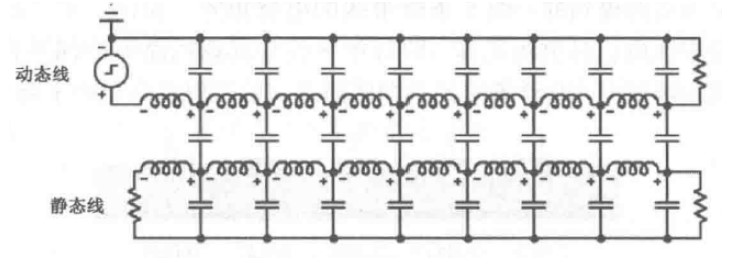

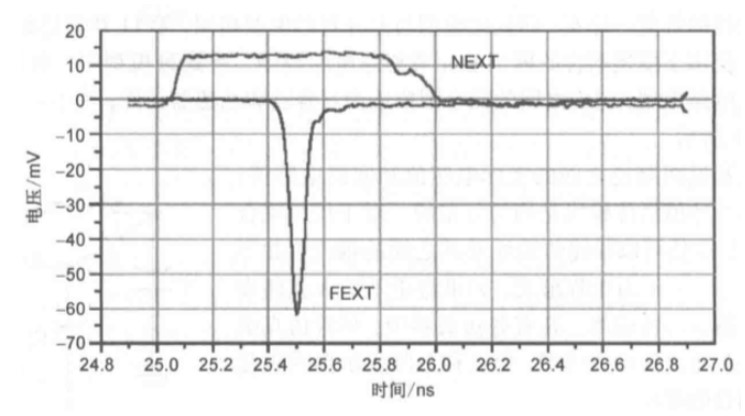

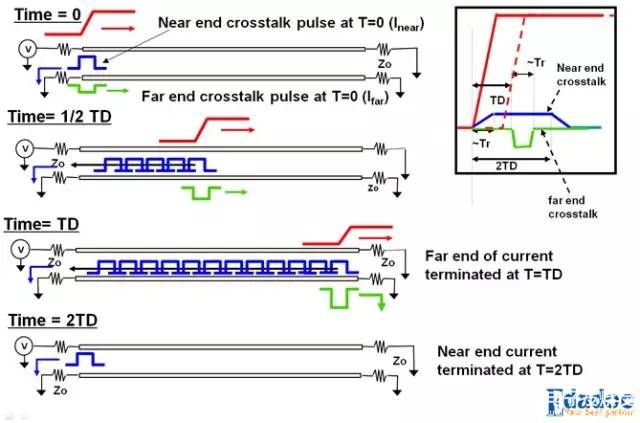

講到傳輸線串擾,下圖是一張必須知道的圖:

NEXT:近端串擾 FEXT:遠端串擾

兩根傳輸線,信號從其中一根傳輸線的一端輸入,遠端放端接消除末端反射。如果不放端接,那就會有反射,至于反射的能量消耗,前文有講過。

噪聲電壓在靜態線的兩端進行測量。為了區分兩個末端,把距離源端最近的一端稱為“近端”,也成為信號傳輸方向的“后方”,而把距離源端最遠的一端稱為“遠端”,遠端信號傳輸方向的“前方”。

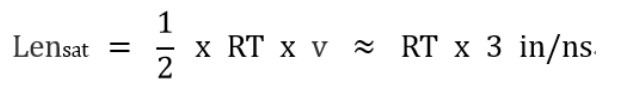

一對傳輸線,耦合區域的總時長為TD,當信號的上升邊RT 是2xTD時,或者說耦合長度是上升邊空間延伸的一半,那這個長度為飽和長度。

Lensat 表示近端串擾的飽和長度(單位為in),RT表示信號上升邊(單位為ns),V表示信號在動態線上的傳播速度(單位為in/ns)。

噪聲電壓即近端串擾幅值(NEXT)達到一個穩定值,當耦合長度大于飽和長度。

當耦合長度小于飽和長度,則電壓峰值將小于NEXT。

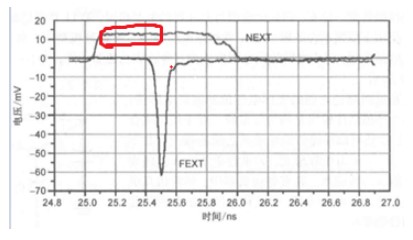

遠端噪聲以脈沖形式出現,信號進入算起,一直要經過TD 時延之后才會出現噪聲。噪聲在靜態線上的傳播速度與信號的速度相等。

FEXT遠端噪聲幅值除了跟遠端噪聲峰值電壓與信號電壓比值有關,還與另兩個外在參數(耦合長度和上升邊)呈比例變化。

這里需要強調一點:

因為感性耦合電流的方向是從返回路徑到信號路徑,呈逆時針方向,這與容性耦合電流的方向相反。所以,在遠端的凈噪聲是容性耦合噪聲與感性耦合噪聲之差。

產品的更新換代,版圖的密集性以及速率的提升,通過調整耦合長度和上升時間(RT)來管控的情況已經很少了,所以我們能做的大多數就是調整線距來控制串擾,而調整線距確實可以減小串擾。

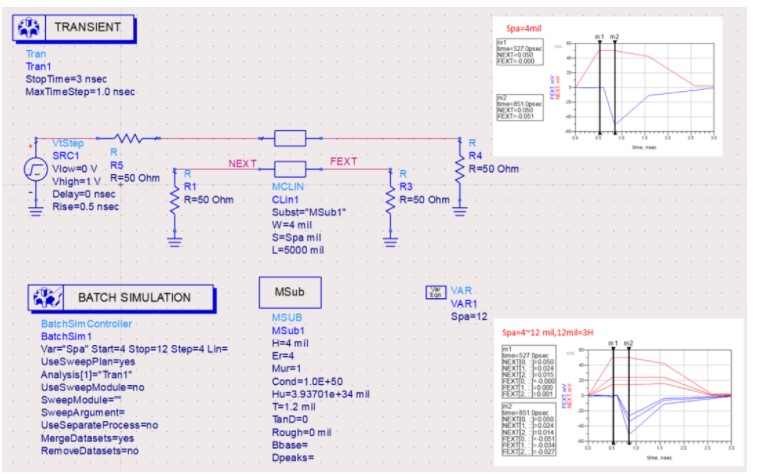

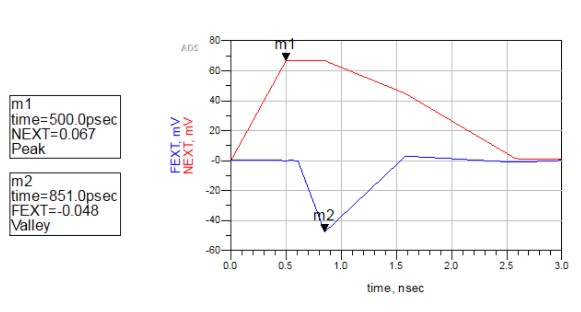

下圖為調整Spa的鏈路以及仿真結果:

Spa=4 mil,噪聲的幅值最大。

需要說明的是,想用的是3H原則,只不過很不巧,竟然也是3W原則。

實際工作中,串擾的管控除了重點關注線間距,返回路徑也需要注意。至于帶狀線層布線,使用介電常數較低的材料等,這些深入且細節的知識,后面有機會再講。

審核編輯:劉清

-

傳輸線

+關注

關注

0文章

375瀏覽量

23998 -

串擾

+關注

關注

4文章

189瀏覽量

26932 -

耦合電感

+關注

關注

0文章

77瀏覽量

20075 -

PCB

+關注

關注

1文章

1777瀏覽量

13204

發布評論請先 登錄

相關推薦

串擾是什么?如何去減小串擾

串擾是什么?如何去減小串擾

評論