當一項創新顛覆了市場時,它便會得到市場的認可

網卡( NIC )自 20 世紀 80 年代便已出現,到本世紀初,許多公司開始投身該領域進行創新。他們最初的重點是高性能計算( HPC )。盡管業務都在以太網上運行,但是,最強大的 HPC 集群是使用 Myrinet 或 Infiniband 創建的。這些網絡的網卡被設計為可以繞過操作系統( OS )內核,直接與 HPC 應用通信,從而顯著提升性能。為了實現這一點,這些網卡在網絡邊緣應用了廣泛的計算資源,使其能夠從主機 CPU 上卸載常見通信任務。

這些HPC 網卡為后來的以太網網卡奠定了基礎,后者內置內核旁路,適用于全球所有股票市場的電子交易。隨著時間推移,這些平臺進一步演進為 SmartNIC (智能網卡)或數據處理單元( DPU )。伴隨超大規模用戶( Hyperscaler )和云服務提供商( CSP )的出現,賽靈思發現了阻礙 SmartNIC 普及的三大因素:

1.可編程性

2.可組合性

3.可移植性

賽靈思提供了一種軟件定義、硬件加速平臺的方法,可以高效解決這三大問題。

可編程性

過去十年里,人們做了各種嘗試來為 SmartNIC 提供一個完全可編程的接口,但沒有一種取得絕對成功。同時,該行業缺乏標準化語言和業經驗證的軟件開發及部署環境。幾年前,賽靈思成為 P4 語言聯盟的活躍成員,作為工業貢獻者,開發了一種跨多類硬件管理網絡數據包的語言。P4 語言迅速發展起來,如今大部分 SmartNIC 和 DPU 都將其用作默認編程語言。賽靈思全新 SN1000 SmartNIC 系列中所有獨特的邏輯塊都是用 P4 編寫的。

可組合性

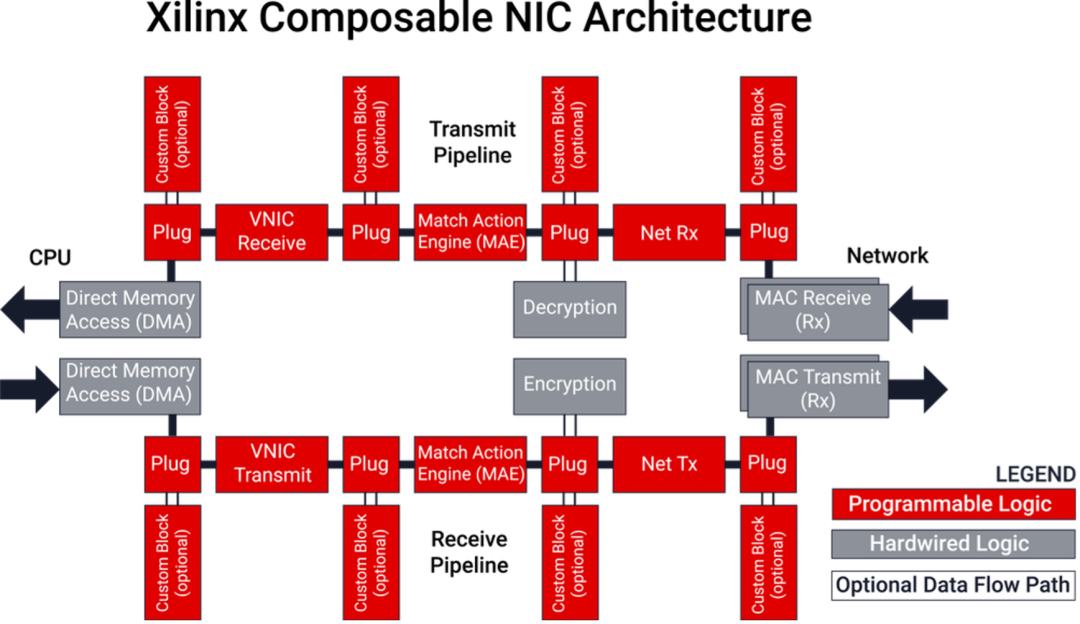

超大規模用戶和 CSP 的第二個要求是可組合性。這是一種將新功能塊動態插入到收發包處理流水線中的功能。這兩條直接管理網絡數據包的流水線構成了 SmartNIC 的數據平面。網卡上的第二個平面稱為控制平面,作用是管理數據平面內的可編程塊。如上所示,賽靈思充分利用了我們在可編程邏輯方面的領先優勢,設計出一款完全可組合的網卡架構。

構成數據平面的收發流水線都有數個可編程入口點,客戶可以在這些入口點上使用我們的 Vitis 軟件開發平臺連接其使用 P4、C/C++、HDL 或 HLS 編寫的代碼塊。然后,Vitis 會將此代碼編譯成邏輯,幫助工程師在適當的數據包處理流水線中插入他們認為合適的模塊。這可以讓數據包以極快的速度通過數據平面,從而使賽靈思能夠支持線速包處理。

其他未在其數據平面中使用可編程邏輯的供應商,必須在其 DPU 上部署大量典型的 CPU 核(通常為 Arm)來處理這些網絡數據包。隨著數據包速率攀升至每秒數億個數據包,這種方法(使用 DPU 上的 CPU 核來處理數據平面上的數據包)將受到影響。我們的軟件定義、硬件加速的方法將令賽靈思的 SN1000 系列明顯優于競爭對手。

大型數據中心客戶(如超大規模用戶和 CSP)通常會要求供應商展示其產品路線圖。該路線圖將向客戶展示供應商對其架構的承諾,以及在未來幾代中推進該架構的計劃。通常需要每一代都是新款芯片,在先前芯片的基礎上有所改進。

可移植性

多年前,Solarflare 開始開發一種用 P4 編寫的完全可移植的 SoftNIC 架構,本次成果最終被賽靈思收購。SoftNIC 是一種將所有核心 NIC 功能全部表示為代碼的網卡,使得 NIC 可以在 FPGA硬件平臺之間輕松移植。SoftNIC 利用直接存儲器訪問( DMA )引擎等標準硬件塊與主機 CPU 進行通信,利用可以具有特定的芯片幾何結構且通常使用了加密塊的介質訪問控制( MAC )塊進行以太網通信。最終結果是,SoftNIC 的漏洞和新增功能無需創建新的芯片,客戶只需安裝軟件更新即可。

構成 SN1000 可移植網卡架構的各種重要組件是 DMA 引擎、加密、MAC 塊、虛擬化網卡 ( VNIC )和匹配操作引擎( MAE )的接口。VNIC 不僅是傳統 OS 設備驅動程序查看網卡的方式,還可以處理校驗和卸載及數據包控制。收發流水線中的 MAE 是處理虛擬網絡請求的地方。在這里,Open vSwitch ( OvS )函數可用于管理主機上運行的虛擬機和容器的流量。MAE 可以顯著減輕主機 CPU 處理 OS 或程序管理器網絡調用的負擔,有時會為 CSP 工作負載返回多達 30% 的主機 CPU 周期。MAE 的設計旨在輕松與 tc-flower 和 DPDK 通用流 API (rte_flow)進行連接,以便處理這些函數。插件入口點、VNIC、MAE 和 NET 引擎均是用軟件編寫并編譯到邏輯門中。這就是賽靈思所謂的軟件定義和硬件加速。

隨著 SN1000 SmartNIC 的發布,賽靈思將提供幾個可選的插件模塊,在接下來的幾個月還將提供更多模塊。借助 SN1000,賽靈思展示了首個完全可組合且可移植的 SmartNIC,這是我們身處業屆競爭最激烈的領域之一而帶來的一項重大創新。

審核編輯 :李倩

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601914 -

cpu

+關注

關注

68文章

10826瀏覽量

211162 -

編程語言

+關注

關注

10文章

1939瀏覽量

34602

原文標題:解決三大痛點,加速SmartNIC普及

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

思爾芯賽題正式發布,邀你共戰EDA精英挑戰賽!

賽思快訊 | 發展新質生產力問道賽思?賽思如何下好“創新棋”?

NucleiStudio_IDE下調試一直報all ones錯誤怎么解決?

安賽思半導體和三福半導體簽署戰略合作協議

安賽思半導體與新加坡三福半導體達成戰略合作

給我一個FPGA,可以撬起所有顯示的接口和面板

CYUSB3014如何實現OTG的功能?

解析FPGA競爭格局背后的驅動因素

第五屆EDA挑戰賽賽果公布!思爾芯“戰隊”成績斐然

易靈思RAM使用--Update3

賽靈思發現了阻礙SmartNIC普及的三大因素

賽靈思發現了阻礙SmartNIC普及的三大因素

評論