差分信號

(Differential signal)

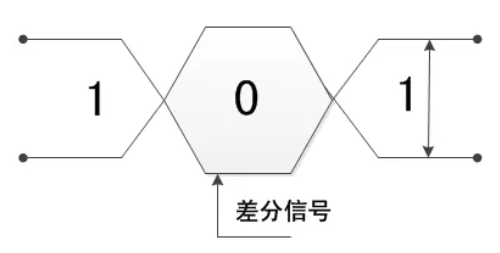

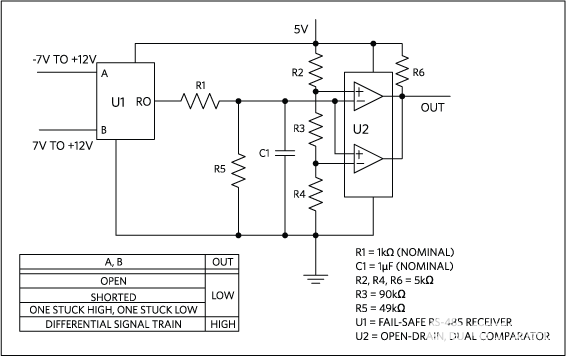

差分傳輸是一種信號傳輸的技術,區別于傳統的一根信號線一根地線的做法,差分傳輸在這兩根線上都傳輸信號,這兩個信號的振幅相等、相位相反。在這兩根線上傳輸的信號就是差分信號。差分信號又稱差模信號,是相對共模信號而言的。

我們用一個方法對差分信號做一下比喻,差分信號就好比是蹺蹺板上的兩個人,當一個人被蹺上去的時候,另一個人被蹺下來了 —— 但是他們的平均位置是不變的。繼續蹺蹺板的類推,正值可以表示左邊的人比右邊的人高,而負值表示右邊的人比左邊的人高。0表示兩個人都是同一水平。應用到電學上,這兩個蹺蹺板用一對標識為V+和V-的導線來表示。

特點

從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,“系統地”被用作電壓基準點。當‘地’當作電壓測量基準時,這種信號規劃被稱之為單端的。我們使用該術語是因為信號是用單個導體上的電壓來表示的。 另一方面,一個差分信號作用在兩個導體上。信號值是兩個導體間的電壓差。盡管不是非常必要,這兩個電壓的平均值還是會經常保持一致。

可以想象,這兩個導體上被同時加入的一個相等的電壓,也就是所謂共模信號,對一個差分放大系統來說是沒有作用的,也就是說,盡管一個差分放大器的輸入有效信號幅度只需要幾毫伏,但它卻可以對一個高達幾伏特的共模信號無動于衷。這個指標叫做差分放大器的共模抑制比(CMRR),一般的運算放大器可以達到90db以上,高精度運放甚至達到120db。因為干擾信號一般是以共模信號的形式存在,所以差分信號的應用極大地提高了放大器系統的信噪比。

優點

抗干擾能力強:干擾噪聲一般會等值、同時的被加載到兩根信號線上,而其差值為0,即噪聲對信號的邏輯意義不產生影響。

能有效抑制電磁干擾(EMI):由于兩根線靠得很近且信號幅值相等,這兩根線與地線之間的耦合電磁場的幅值也相等,同時他們的信號極性相反,其電磁場將相互抵消。因此對外界的電磁干擾也小。

時序定位準確:差分信號的接受端是兩根線上的信號幅值之差發生正負跳變的點,作為判斷邏輯0/1跳變的點的。而普通單端信號以閾值電壓作為信號邏輯0/1的跳變點,受閾值電壓與信號幅值電壓之比的影響較大,不適合低幅度的信號。

缺點

若電路板的面積非常緊張,單端信號可以只有一根信號線,地線走地平面,而差分信號一定要走兩根等長、等寬、緊密靠近、且在同一層面的線。這樣的情況常常發生在芯片的管腳間距很小,以至于只能穿過一根走線的情況下。

時鐘數據恢復

(CDR:clock data recovery)

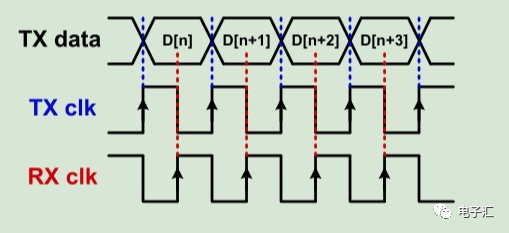

時鐘恢復作為高速串行通信必須具有的核心功能得到越來越廣泛的應用,在以太網、PCI-Express、Aurora中都有時鐘恢復模塊。相對的,傳統的時鐘與數據同時傳輸的并行傳輸方式無法達到1Gb/s以上帶寬。

簡單的來說,所謂時鐘恢復就是:根據參考時鐘,從數據信號把時鐘信號提取出來。相對應的,在信道上只傳輸串行數據,在信道上并沒有時鐘信號。數據接收端接收串行數據并進行時鐘恢復。

SERDES中,時鐘數據恢復的基礎。通常CDR協議運行在較高的數據速率和較長的傳送距離,因此帶來很大的設計挑戰。

在SERDES(Serializer-Deserializer)應用中,顧名思義,CDR接收器必須從數據中恢復嵌入的時鐘。更準確地說,是從數據信號的交換中獲取時鐘。

CDR發送器首先串行發送數據,然后將數據轉換成8b/10b編碼方案。編碼處理獲得8位數據并將其轉換成10位符號。8b/10b編碼方式可以在數據線上傳送相等數目的0和1,從而減少碼間干擾,并提供足夠多的數據邊沿,以便接收器在收到的數據流上鎖定相位。發送器將系統時鐘倍頻至傳送比特率,并以該速率在TX差分對上發送8b/10b數據。

CDR接收器的任務首先是在RX差分位流上鎖定相位,然后接收器按照恢復的時鐘進行數據位對齊,接著用接收器的參考時鐘進行字對齊。最后,將數據進行8b/10b解碼,供系統使用。

在CDR系統中,發送和接收系統通常擁有完全獨立的系統時鐘。這兩個時鐘在一個特定的變化范圍內非常關鍵,這個范圍大約是數百個PPM。

CDR電路與抖動

CDR接口的主要設計挑戰是抖動,即實際數據傳送位置相對于所期望位置的偏移。總抖動(TJ)由確定性抖動和隨機抖動組成。大多數抖動是確定的,其分量包括碼間干擾、串擾、占空失真和周期抖動(例如來自開關電源的干擾)。而通常隨機抖動是半導體發熱問題的副產品,且很難預測。

傳送參考時鐘、傳送PLL、串化器和高速輸出緩沖器都對會傳送抖動造成影響。對于給定的比特周期或者數據眼,傳送抖動通常用單位間隔的百分比或UI(單位間隔)來說明。例如,.2 UI的傳送抖動表示抖動由比特周期的20%組成。對于傳送抖動而言,UI數值越低越好,因為它們代表較少的抖動。

同樣地,CDR接收器將指定在給定比特率時所能容忍的最大抖動量。典型的比特誤碼率(BET)標準是1e-12。接收抖動仍然用UI來指定。較大的UI表明接收器可以容忍更多的抖動。典型的接收器規格是.8 UI,這意味著80%的比特周期可以是噪聲,此時接收器將仍然能夠可靠地接收數據。抖動通常用統計鐘形分布來量化,該分布在其定點處有理想的邊沿位置。

信道均衡

(Channel equalization)

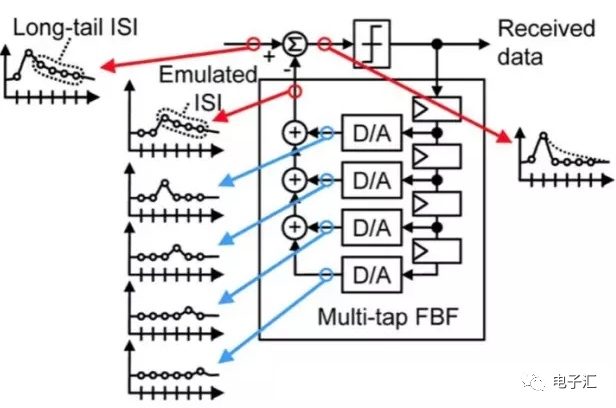

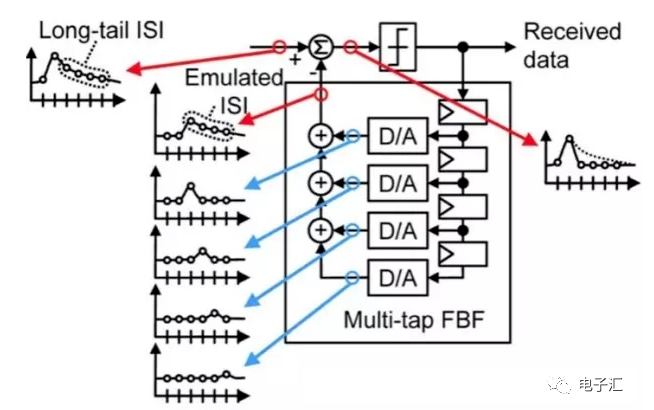

信道均衡(Channel equalization)是指為了提高衰落信道中的通信系統的傳輸性能而采取的一種抗衰落措施。它主要是為了消除或者是減弱寬帶通信時的多徑時延帶來的碼間串擾(ISI)問題。

其機理是對信道或整個傳輸系統特性進行補償,針對信道恒參或變參特性,數據速率大小不同,均衡有多種結構方式。大體上分為兩大類:線性與非線性均衡。線性均衡器和非線性均衡器的主要差別在于自適應均衡器的輸出被用于反饋控制的方法。對于帶通信道的均衡較為困難,一般都是待接收端解調后在基帶進行均衡,因此基帶均衡技術有廣泛應用。

在實際中一般是加入自適應濾波器來實現信道均衡。使用濾波器來補償失真的脈沖,判決器得到的解調輸出樣本,是經過均衡器修正過的或者清除了碼間干擾之后的樣本。自適應均衡器直接從傳輸的實際數字信號中根據某種算法不斷調整增益,因而能適應信道的隨機變化,使均衡器總是保持最佳的狀態,從而有更好的失真補償性能。

審核編輯:湯梓紅

-

濾波器

+關注

關注

160文章

7728瀏覽量

177685 -

差分信號

+關注

關注

3文章

367瀏覽量

27653 -

時鐘數據

+關注

關注

0文章

4瀏覽量

6592

原文標題:高速電路工程師的三大法寶:差分信號、時鐘數據恢復、均衡

文章出處:【微信號:電子匯,微信公眾號:電子匯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

詳解差分信號及PCB差分信號設計中幾個常見的誤區

【微信精選】模電工程師的三大法寶:差分信號、時鐘數據恢復、信道均衡

差分信號的優缺點

基于盲均衡的水聲信號波形恢復

差分信號的優缺點有哪些

差分信號的優缺點及布線要求

詳解差分信號、時鐘數據恢復、信道均衡

詳解差分信號、時鐘數據恢復、信道均衡

評論