來源:半導體芯科技編譯

SEMI最近與PowerAmerica聯盟的執行董事兼首席技術官Victor Veliadis合作,舉辦了一次題為SiC-碳化硅材料特性、制造基礎知識和關鍵應用的在線研討會。在接受《半導體工程》采訪時,Veliadis詳細介紹了SiC制造工藝和Si工藝的差異的一些要點。

Etch蝕刻工藝。SiC在化學溶劑中呈現惰性,只有干法蝕刻可行。掩膜材料、掩膜蝕刻的選擇、混合氣體、側壁斜率的控制、蝕刻速率、側壁粗糙度等都需要重新開發。

Substrate thinning襯底減薄。對于SiC低電阻或厚外延處理(材料硬度要求特殊配方)。CMP用于精細平整度控制。

Doping摻雜工藝。由于碳化硅熔點高,摻雜劑擴散常數低,傳統的熱擴散在碳化硅中并不實用。評估注入種類、劑量、能量、溫度、掩蔽材料等。SiC注入后再結晶和注入物激活退火方法(爐內、RTA等)、溫度、升溫速率、持續時間、氣體流量等。選擇退火保護層,最大限度地減少SiC晶片表面退化。CMP可用于壓平硅片,減輕高溫退火的影響。

Metallization關于金屬化。針對SiC需要評估CTE匹配的金屬,選擇抗蝕劑類型,開發底部剝離輪廓,金屬蒸發和剝離,濺射金屬沉積和干法蝕刻。

Ohmic contact formation歐姆觸的形成。SiC/金屬阻隔層的高值導致了整流接觸。對于歐姆接觸,需要進行金屬沉積后退火。優化退火溫度、升溫速率、持續時間、氣體流量,保持表面質量。

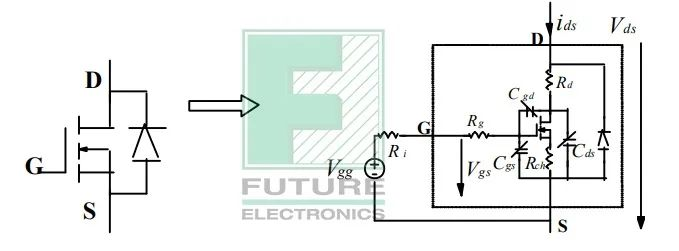

Gate oxides柵極氧化物。較差的SiC/SiO2界面質量會降低MOS反轉層的遷移率。開發鈍化技術,以提高SiC/SiO2界面質量。

Transparent wafers透明晶圓。這使得CD-SEM和計量測量變得復雜,因為焦平面是通過使用光學顯微鏡來確定的。其他工具需要軟件/增益/硬件調整,以轉移到SiC不透明的波長。需要SiC計量/校驗工具。

Relative lack of flatness in SiC wafers SiC晶圓相對缺乏的平整度。這可能會使光刻和其他加工復雜化,特別是高壓器件(厚漂移外延層)。高溫工藝會進一步降低晶圓的平整度。CMP可以在制造的不同的制造階段使晶圓變平。

Insulation dielectrics 絕緣電介質。厚的電介質被沉積在SiC中。評估沉積的介質缺陷對邊緣終端和器件可靠性的影響。

Veliadis認為,傳統IDM通過調整現有工藝,針對SiC的材料特性進行特定的工藝開發和優化,并達到合格標準后,另需購買一些關鍵的新設備,現有成熟的Si產線可轉化為SiC產線。比如,一條150mm的硅制造生產線轉化為SiC生產線,費用大約為2000萬美元。

審核編輯 黃昊宇

-

工藝

+關注

關注

4文章

575瀏覽量

28752 -

SiC

+關注

關注

29文章

2760瀏覽量

62451

發布評論請先 登錄

相關推薦

SiC MOSFET和SiC SBD的區別

產線AGV和倉儲AGV到底有什么不同?

聯合電子400V SiC(碳化硅)電橋在太倉工廠迎來首次批產

Wolfspeed 8英寸SiC襯底產線一期工程!總投資超350億

CClinkie轉Profinet 在包裝機產線應用

CClinkie轉Profinet 在包裝機產線應用

加固平板電腦在工廠產線測試上的應用

益中封裝擴建車規Si/SiC產線

功率電子器件從硅(Si)到碳化硅(SiC)的過渡

為什么SiC在功率應用中戰勝了Si?

SiC和Si產線差異和轉換

SiC和Si產線差異和轉換

評論