電子發燒友網報道(文/周凱揚)進入AI和云時代以來,顯而易見的趨勢之一就是FPGA出現的頻率開始降低了,且不說曾經的兩大FPGA巨頭均已被x86廠商收購,就連FPGA引以為豪的多樣化和靈活性,也被專注于特定應用但全定制化、成本低的ASIC壓得有些抬不起頭來。FPGA廠商們也沒法維系那么多的應用,去和不斷涌現的ASIC初創公司在各個領域去一一硬碰硬。

與此同時,FPGA大廠在被收購后,也開始順應他們的技術路線,可以看到他們的產品方向開始往數據中心、通信基建這些平均產品單價更高的應用上發展,尤其是智能網卡、IPU、DPU這類產品。雖然說中端FPGA產品并沒有就此消失,但明顯競爭力已經大不如前了,過去的那些產品連滿足現代計算處理的標準和需求都有些勉強,更不用說未來了。FPGA需要一陣令其重獲新生的新風,而基于RISC-V打造的SoC FPGA或許就能充當這樣的角色。

FPGA上的RISC-V

RISC-V和FPGA的關系打從一開始就非常密切,不少RISC-V核心、處理器都是在FPGA上實現或驗證的。與此同時,RISC-V從IP、架構和指令上帶來的創新也被FPGA廠商們看在眼里,諸如Microchip、易靈思、安路科技等廠商都開始基于RISC-V打造全新的FPGA產品,英特爾也開發了為其FPGA打造的RISC-V軟核,Xilinx也成了RISC-V國際基金會的戰略會員,RISC-V在FPGA上的普及速度可能遠超你的想象。

以Microchip的PolarFire為例,作為首個支持RISC-V ISA的SoC FPGA系列,終于在今年6月正式進入量產階段了,具體包括MPFS250T和MPFS025T這兩款產品。PolarFire系列采用了4輸入LUT+DFF的設計,最大規模的MPFS460T可以做到461K邏輯單元。

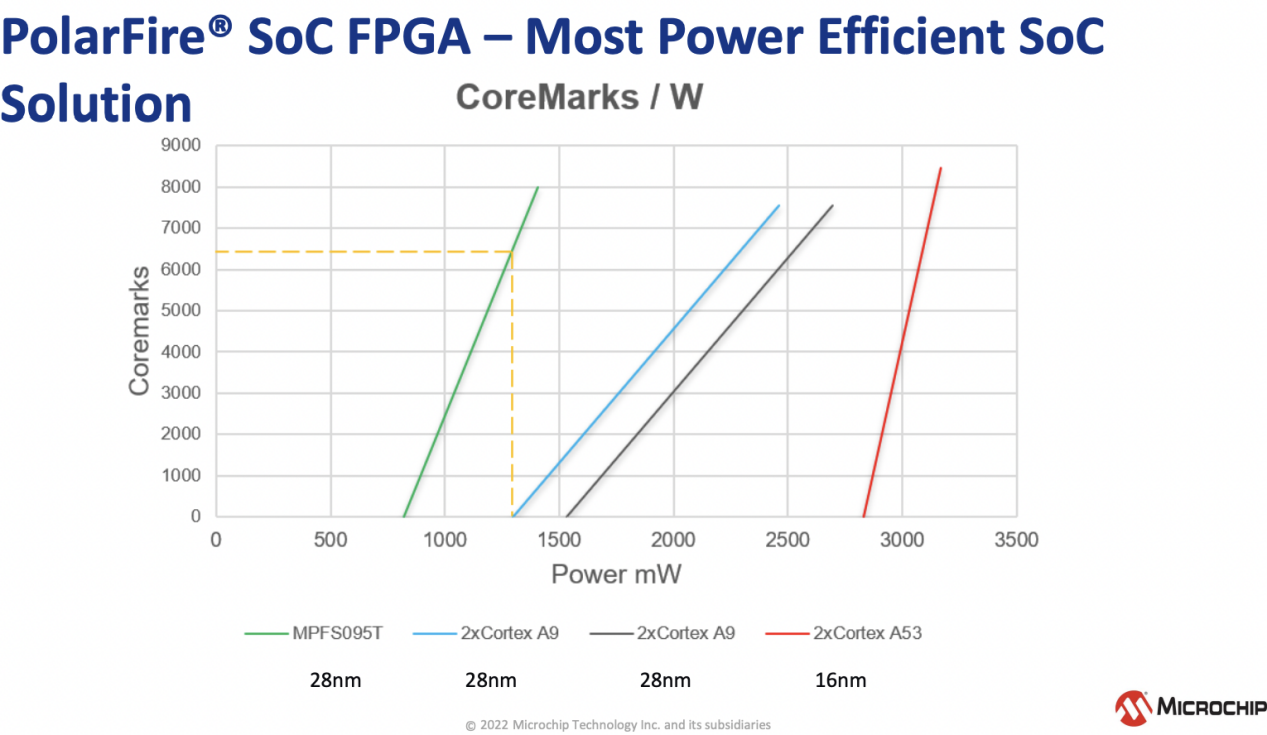

PolarFire CoreMark跑分 / Microchip

而在SoC方面,PolarFire采用了5個64位RISC-V核心的設計,E51作為monitor單核,負責啟動和配置處理器子系統,另外四個U54核心則主要用于負責運行Linux之類的操作系統。至于為何選擇RISC-V而不是像旗下另一SoC FPGA系列SmartFusion一樣選擇ARM,Microchip也給出了同等邏輯單元密度下CoreMark跑分的對比,可以看出即便是在工藝落后(28nm對比16nm)的情況下,基于RISC-V的PolarFire SoC依然是最高效的那個,Microchip指出與其他中端FPGA相比,可以將能耗降低最多50%。

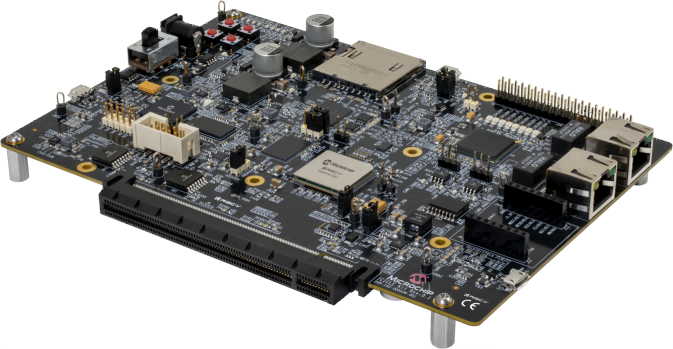

PolarFire FPGA開發套件 / Microchip

為了方便開發者完成不同SoC之間的嵌入式應用程序移植,Microchip也專門打造了MI-V這一面向RISC-V的生態系統,在本身提供RISC-V軟核IP的同時,也和IAR Systems、SiFive、Zephyr等第三方公司合作,提供開發工具、CPU IP和RTOS等支持。

擁抱開源生態

Rapid Silicon是一家專注于打造AI FPGA的初創公司,從他們的董事長兼首席執行官Naveed Sherwani博士的公開發言中,可以看出Rapid Silicon作為開源FPGA基金會的創始成員之一,計劃利用FPGA開拓邊緣AI應用,比如智能家居、安防監控和汽車傳感器管理和智能座艙等市場,而他們手里的王牌既有專用AI技術,也有開源EDA軟件。

Rapid Silicon在近期推出了Gemini,一個基于臺積電16nmFF工藝的FPGA,采用了常見的FPGA設計,比如6輸入的可分割LUT、DSP區塊和真雙端口的Block RAM。最大規模為250K邏輯單元、1250個DSP區塊和9.5Mb的片上Block RAM,4個輸出PLL支持生成高達1GHz的時鐘信號。作為中端FPGA,其規模不算太大,但完成邊緣AI的應用還是綽綽有余的。

Gemini框架 / Rapid Silicon

對于硬件資源充裕的FPGA來說,RISC-V和Arm未必就是不能共存的死對頭,這點在Gemini也能體現出來。Gemini集成了單核32位的RISC-V處理器和雙核的ARM A53處理器。32位的RISC-V處理器作為支持自定義指令的實時應用處理器,最高頻率可達533MHz,同時擁有16KB的I/D cache和64KB的程序內存。

Gemini上的64位Arm處理器浮點單元頻率可達1.6GHz,此外還集成了支持最高2166Mbps DDR內存的DRAM控制器、PCIe 4.0的PCIe控制器、10G以太網控制器等,均由高性能低延遲的FlexNoC互聯在一起。

更重要的是,Gemini的誕生還是利用他們自己的開源FPGA EDA套件Raptor打造出來的,這也證明了依靠開源工作流打造FPGA系統是完全可行的。2021年10月,Rapid Silicon獲得了來自成為資本領投的1500萬美元種子資金,考慮到成為資本是RISC-V國際基金會的高級會員,創始人李世默也是RISC-V國際基金會理事,愿意對Rapid Silicon投資也就不足為奇了。

結語

與傳統的ASIC方案相比,SoC FPGA還是有著不少優勢的,比如沒有昂貴的NRE成本或是最小采購量的需求。再者,FPGA最大的優勢還是在可編程上,即便是已經出貨的產品也能重新編程,進一步降低設計風險。而RISC-V的出現,則為這類SoC FPGA帶來了一個全新而開放的ISA選擇。

-

ASIC芯片

+關注

關注

2文章

91瀏覽量

23722 -

FPGA芯片

+關注

關注

3文章

246瀏覽量

39780 -

RISC-V

+關注

關注

44文章

2229瀏覽量

46032

發布評論請先 登錄

相關推薦

RISC-V發展及FPGA廠商為什么選擇RISC-V

RISC-V近期市場情況調研

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

risc-v的發展歷史

rIsc-v的缺的是什么?

為什么要有RISC-V

解鎖RISC-V技術力量丨曹英杰:RISC-V與大模型探索

玄鐵RISC-V生態大會深圳召開,達摩院引領RISC-V創新應用

RISC-V能讓FPGA從ASIC時代崛起嗎?

RISC-V能讓FPGA從ASIC時代崛起嗎?

評論