系統仿真工具(System Level Simulator)的作用是對電子系統進行高層次的建模及仿真,以減少系統從設計到實現所需迭代優化的次數,降低在系統實現中后期出現問題的風險。

系統仿真工具可對系統建模提供靈活的支持,利用內建或外接的各種預估算法、實現算法和仿真算法對系統的功能與性能做出合理的評估和驗證。

系統仿真工具使用建模語言描述系統,建模語言具有如下特性:

(1)建立系統各功能模塊的模型,允許用不同層次的模型來描述不同的模塊以及模塊相互間的信息交換;

(2)對模塊提供不同實現方法的選擇,例如用硬件或嵌入式軟件實現,使用何種架構實現等;

(3)提供各種模型庫,支持用已有的設計模型或IP核來實現一部分特定的功能模塊。

C/C++和System C是當前常用的建模語言。針對系統描述和仿真的多樣化需求,新型的系統建模語言還在不斷涌現。其中一些以更抽象的形式來描述系統,適合一般性的系統設計,如UML、SysML等語言;另一些則在嵌入式系統設計方面提供更多定制化的支持,如系統設計工具Teraptor所支持的SMDL和SSDL等建模語言。

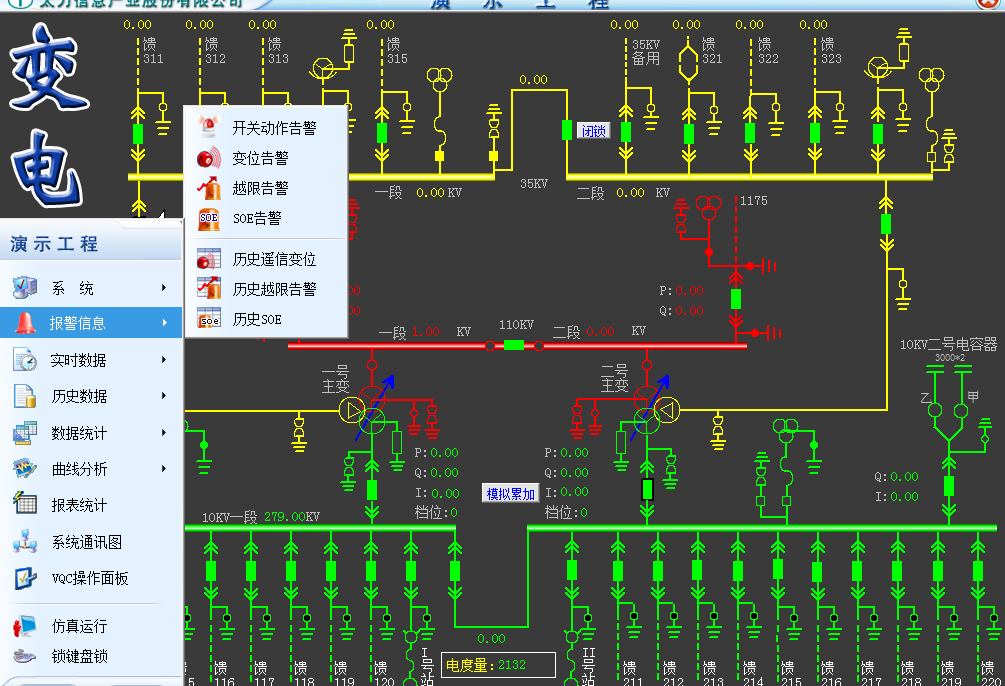

許多系統仿真工具都是基于模型并利用圖形化界面進行仿真的,如LabVIEW、MATLAB、SystemVue、VisualSim Architect和Simulink等。

系統仿真工具已經被設計公司廣泛地應用在系統和芯片設計中,在嵌入式系統、SoC軟硬件系統的設計、驗證和調試過程中扮演著愈加重要的角色。

審核編輯:劉清

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42580 -

可編程

+關注

關注

2文章

844瀏覽量

39784 -

電子系統

+關注

關注

0文章

399瀏覽量

31130

原文標題:可編程邏輯電路設計—系統仿真工具

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Matlab/Simulink/Stateflow建模開發及仿真測試

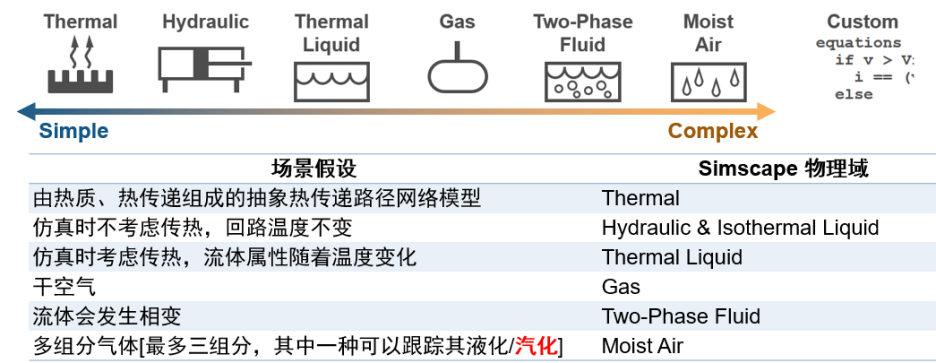

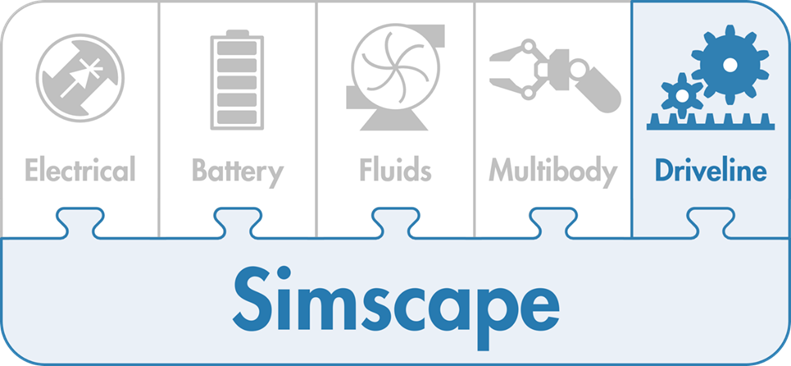

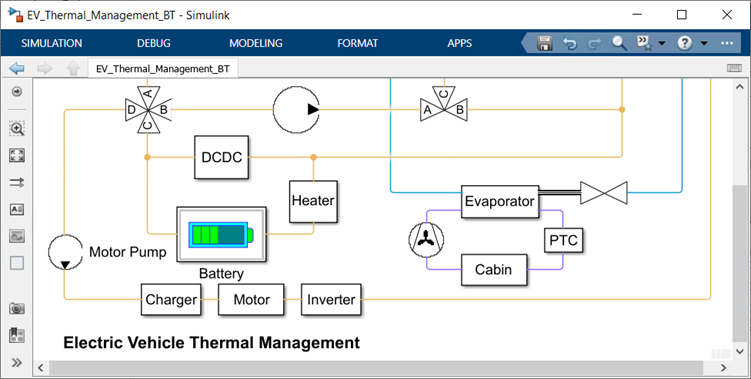

基于Simscape Fluids模型的環控系統建模與仿真

基于Simscape Driveline模型的傳動系統建模與仿真

基于Simscape Battery模型的電池系統建模與仿真

康謀分享 | 自動駕駛聯合仿真——功能模型接口FMI(二)

電磁信號模擬系統

從MATLAB到MWORKS,科學計算與系統建模仿真平臺的中國選項

如何使用 ModelSim 進行設計仿真

射頻和微波系統的系統級表征和建模方案

Stimulus—需求形式化建模和驗證工具

系統仿真工具使用建模語言描述系統

系統仿真工具使用建模語言描述系統

評論