電子發(fā)燒友網(wǎng)報道(文/周凱揚(yáng))當(dāng)下服務(wù)器市場在內(nèi)存上面臨的一大挑戰(zhàn)就是成本,截至今日,我們在選擇云服務(wù)容器時,內(nèi)存依然占了很大一部分,往往內(nèi)存用量擴(kuò)大一倍后,價格也隨之上漲了一倍。這其實與內(nèi)存本身的擴(kuò)展性有關(guān),目前服務(wù)器上更大的存儲已經(jīng)成為常態(tài),但要想實現(xiàn)更大的內(nèi)存始終存在瓶頸。因此,從2013年開始,每bit內(nèi)存的價格基本趨于平緩了。

但服務(wù)器CPU的核心數(shù)增加的速度可沒有因此減緩下來,加上AI等新型工作負(fù)載的引入,更大的內(nèi)存容量、更大的內(nèi)存帶寬,都成了當(dāng)下服務(wù)器內(nèi)存面臨的痛點(diǎn)。為此,業(yè)界開始考慮從系統(tǒng)層級上來解決這些問題,比如為CPU增加DDR通道,好讓其支持更大的帶寬和容量。

但這就又引入了一系列新問題,為了滿足新增的DDR通道,需要更多的引腳,也提高了成本降低了可靠性,PCB的層數(shù)也開始增加。這也造就了整個服務(wù)器主板的尺寸變得異常大,甚至難以放進(jìn)1U標(biāo)準(zhǔn)尺寸的機(jī)柜里。

CXL的靈活性和延遲這時對于內(nèi)存媒介無限制的CXL,就提供了一個靈活的內(nèi)存接口,讓設(shè)計者可以從持久性、延遲、帶寬等各個參數(shù)特性上靈活選擇,讓服務(wù)器CPU不止可以使用常用的DDR內(nèi)存,也能支持LPDDR5和持久內(nèi)存等等。我們此前已經(jīng)多次介紹過CXL了,這次就來講下作為內(nèi)存擴(kuò)展,CXL有哪些優(yōu)勢。

比如一個80核的CPU,應(yīng)用要求每個核心配置2GB的DDR5內(nèi)存,也就是需要160GB的DDR5內(nèi)存。如果采用16GB DIMM x8的配置明顯滿足不了,32GB x 8多出了96GB內(nèi)存,徒增了近乎500美元的成本,使用32GB x 5這樣不跑滿通道的配置雖然容量對了,但是會降低帶寬和性能。

而這時我們反觀CXL,CXL可以在配置了原生DDR通道配置了8個16GB DIMM的情況下,再加入32GB的CXL內(nèi)存,如此一來不僅滿足了內(nèi)存容量的需求,還增加了額外的帶寬,況且我們已經(jīng)提到了CXL并沒有內(nèi)存媒介的限制,所以可以用上LPDDR5之類的CXL擴(kuò)展內(nèi)存進(jìn)一步降低成本。

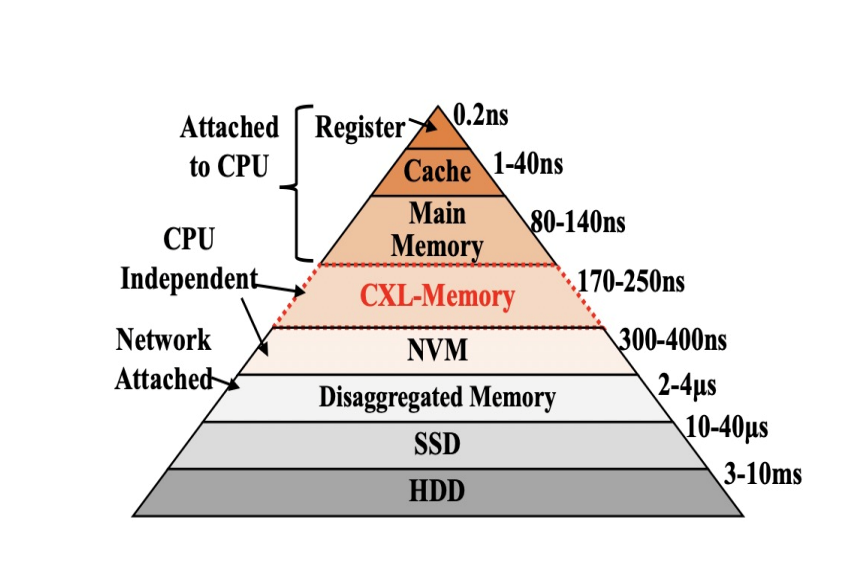

各種緩存、內(nèi)存和存儲的延遲對比 / CXL聯(lián)盟

作為一個分布式內(nèi)存,盡管CXL主打的是低延遲,但要說與CPU的內(nèi)存、緩存和寄存器比起來,延遲還是有一定差距的。今年的Hot Chips上,CXL聯(lián)盟就給出了CXL在延遲上的具體數(shù)字。獨(dú)立于CPU外的CXL內(nèi)存延遲在170-250ns左右,高過獨(dú)立于CPU的NVM、網(wǎng)絡(luò)連接的解構(gòu)內(nèi)存、SSD和HDD等。

雖然在我們看來這個數(shù)字已經(jīng)很小了,但相較原生的主要內(nèi)存,還是把延遲擴(kuò)大了兩倍。來自Meta和AMD的兩位專家提出了一個概念,也就是對內(nèi)存進(jìn)行分層,分為用于實時分析等關(guān)鍵任務(wù)的“熱”內(nèi)存、訪問不那么頻繁的“暖”內(nèi)存和用于龐大數(shù)據(jù)的“冷”內(nèi)存。“熱”內(nèi)存頁面放在原生DDR內(nèi)存里,而“冷”內(nèi)存頁面則交給CXL內(nèi)存。

然而在當(dāng)前的軟件眼里,它們才分不清楚什么是“熱”內(nèi)存和“冷”內(nèi)存,原生內(nèi)存用完后,就開始去占用CXL內(nèi)存,如此一來原本作為“冷”內(nèi)存的CXL,也開始變成“熱”內(nèi)存。所以目前最大的挑戰(zhàn)就是在操作系統(tǒng)和軟件層面,如何檢測到“冷”內(nèi)存頁面,將其主動轉(zhuǎn)入CXL內(nèi)存里,為原生內(nèi)存留出空間。Meta和AMD的兩位專家表示,他們已經(jīng)在開發(fā)相應(yīng)的軟硬件技術(shù)。

CXL或許不會成為HPC和AI應(yīng)用的寵兒固然CXL對于云服務(wù)廠商和諸多數(shù)據(jù)中心擁有不錯的吸引力,然而這種形式的內(nèi)存可能并不適用于HPC與超算應(yīng)用。“富岳之父”松岡聰教授表示CXL這種內(nèi)存解構(gòu)方案還存在不少技術(shù)問題,使其不能在主流的HPC甚至是AI負(fù)載中物盡其用。松岡聰教授并沒有給出具體的細(xì)節(jié),但他給出了一個例子,那就是多年前SGI的NUMALINK系統(tǒng)也是采用了分布式內(nèi)存解構(gòu)的方式,但我們也都知道如今市面上的NUMALINK產(chǎn)品基本已經(jīng)銷聲匿跡了。

但他并沒有徹底否認(rèn)內(nèi)存解構(gòu)這種思路,就連富岳超算本身也用這一技術(shù),從而將MPI進(jìn)行put/get運(yùn)算時的遠(yuǎn)程內(nèi)存訪問延遲降低至亞微秒級。但加入一個單獨(dú)的UMA內(nèi)存池,已經(jīng)在歷史中證明了這對HPC來說收效甚微。

首先,這需要更高硬件交換機(jī)成本,再者,在超算這種大型配置規(guī)模的系統(tǒng)上,缺乏對應(yīng)的編程標(biāo)準(zhǔn)。因此,對于目前的HPC大型系統(tǒng)來說,CXL內(nèi)存或許會先出現(xiàn)在一小部分節(jié)點(diǎn)上,比如一些需要近存或存內(nèi)計算AI負(fù)載,而不會普及到整個系統(tǒng)。

寫在最后其實對于CXL的擔(dān)心也沒必要那么多,對于服務(wù)器市場來說,低核心數(shù)的CPU依然會繼續(xù)使用原生DDR通道來配置DIMM內(nèi)存。到了高核心數(shù)CPU上,再根據(jù)系統(tǒng)成本、容量、功耗和帶寬等參數(shù)來靈活應(yīng)用CXL內(nèi)存,而這才是CXL帶來的最大優(yōu)勢,靈活性。況且目前CXL內(nèi)存還沒有大規(guī)模量產(chǎn)出來,自然也沒有普及開來,大家對其實際性能表現(xiàn)還沒有個大致了解,也許引入CXL的延遲后,對性能的損失不會那么糟糕。

-

pcb

+關(guān)注

關(guān)注

4317文章

23006瀏覽量

396298 -

帶寬

+關(guān)注

關(guān)注

3文章

908瀏覽量

40845 -

服務(wù)器

+關(guān)注

關(guān)注

12文章

9021瀏覽量

85184

原文標(biāo)題:救場服務(wù)器內(nèi)存的CXL

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

美國多IP服務(wù)器和美國多服務(wù)器有什么區(qū)別

GPU服務(wù)器和傳統(tǒng)的服務(wù)器有什么區(qū)別

云服務(wù)器主要應(yīng)用行業(yè)及優(yōu)勢

美國硅谷RAKsmart服務(wù)器的優(yōu)勢

就服務(wù)器而言,ARM架構(gòu)與X86架構(gòu)有什么區(qū)別?各自的優(yōu)勢在哪里?

硅谷物理服務(wù)器有哪些關(guān)鍵優(yōu)勢和特點(diǎn)

韓國裸機(jī)云站群服務(wù)器是什么?有什么優(yōu)勢

IaaS云服務(wù)器的優(yōu)勢是什么?

洛杉磯裸機(jī)云大寬帶服務(wù)器的特性和優(yōu)勢

美國云服務(wù)器的優(yōu)勢

linux服務(wù)器和windows服務(wù)器

美國硅谷服務(wù)器的優(yōu)勢

什么是CXL技術(shù)?CXL的三種模式、類型、應(yīng)用

CXL服務(wù)器有哪些優(yōu)勢

CXL服務(wù)器有哪些優(yōu)勢

評論