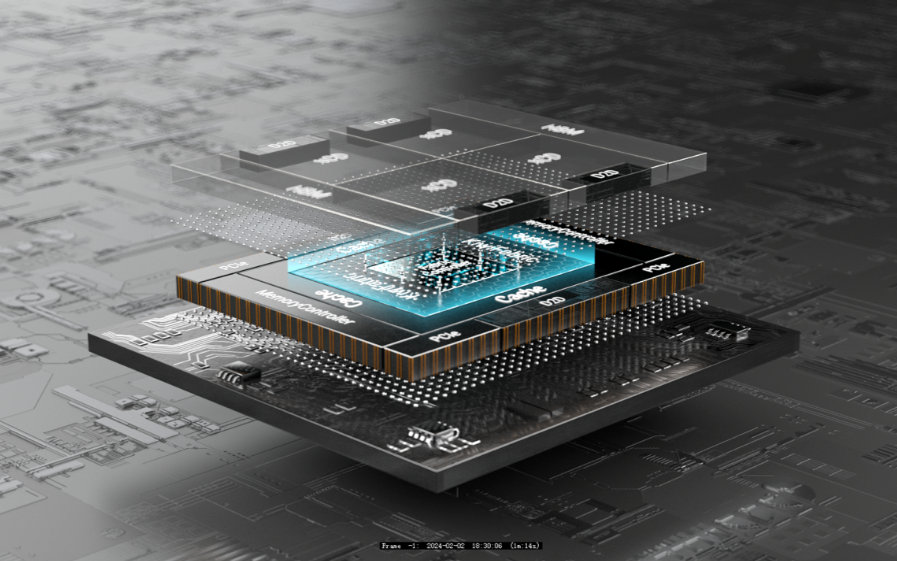

芯片設計可謂是人類歷史上最細微也是最宏大的工程。它要求把上千億的晶體管集成到不到指甲蓋大小的面積上,這其中 EDA 工具的作用不可或缺。它于芯片設計就如同編輯文檔需要的 Office 軟件,是電子工程師設計電路、分析電路和生成電路的重要途徑。

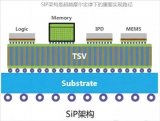

如今,在電子產品愈發小型化、集成化的趨勢下,芯片正在從系統芯片(SoC)向系統級封裝(SiP)的設計方法過渡,以往只在消費電子中應用的封裝技術,現已逐漸滲透拓展至工業控制、智能汽車、云計算、醫療電子等諸多新興領域。對于 SiP 市場的迅速崛起,Cadence 公司產品市場總監孫自君在接受《半導體行業觀察》采訪的時候發表了自己的觀點。

SiP是趨勢也是挑戰

采用 SiP 的封裝形式,固然滿足了廠商對于產品集成化、開發成本以及研發周期之間的權衡,但同時也給芯片設計帶來了全新的挑戰。在這種情況下,如何簡化 SiP 的設計過程將成為推動對系統級封裝(SiP)芯片技術需求的關鍵能力。

從整體流程來看,SiP 于 EDA 而言,其最重要的影響是設計方法的改變。一個完整的設計流程與工具支持是簡化產品開發工作的重要條件。因此,工具對于未來技術可擴展性、向下兼容性以及數據交換的標準化都是必要的考量點。

由于電子產品小型化、緊湊化需求迫切,工程師在進行芯片設計時,不再僅需要考慮電性設計,電與熱的交互設計也要被重視,這包括了熱感知設計方法,E-T Co-simulation 工具的使用。Cadence 針對目前 SiP 設計方式所存在的固有局限性,提供了一套自動化、整合的、可信賴并可反復采用的工藝以滿足無線和消費產品不斷提升的性能需求。

標準化的商業模型是SiP發展的前提

SiP的封裝形式對標準化提出了新的要求。SiP 的封裝形式對標準化提出了新的要求。與傳統的硬 Hard IP layout 或 Soft IP netlist 相比,Chiplet 憑借更高的靈活度、更高性能以及更低的成本成為集成封裝的最佳選擇。然而在設計方案中采用多個 Chiplet 進行布局和驗證,這對于 IC 設計團隊和封裝設計人員來說都是不可忽視的難題。在這種情況下,擴展以支持多個 Chiplet 的設計工具和方法對于項目的成敗變得舉足輕重。

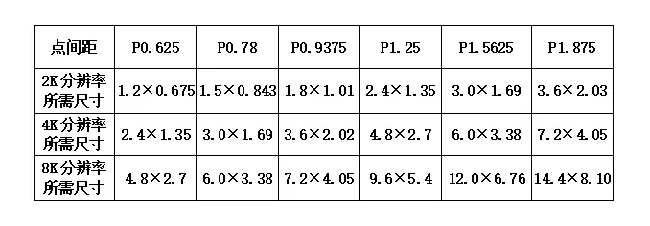

目前雖然已經有許多用 Chiplet 來構建和設計的產品,但是其中的大部分工作還是要依靠人工完成。也就是說在現在的條件下,幾乎所有基于 Chiplet 的設計還都需要在垂直集成 IDM (垂直整合制造)的公司中完成。而若想讓基于 Chiplet 的架構向主流市場擴展,使 Chiplet 變得廣泛可用,業界還需要制定一個標準化的商業模型,并且建立 Chiplet 標準的開發技術和設計文檔編制。包括 I-O 間距、通信接口和相應的產業技術標準的適用性、low power/low BER、low latency 還有 Tool kit 與設計參考 PDK。

當設計一個系統級芯片時,傳統的方法需要通過從不同的 IP 供應商中購買一些 IP,軟核(代碼)或硬核(版圖),然后結合自研的模塊,集成為一個 SoC,最后在某個芯片工藝節點上完成芯片設計和生產的完整流程。而未來,這種基于標準化的 Chiplet 架構允許設計人員直接應用 IP,而無需考慮其不同的工藝節點或技術,如模擬、數字或混合信號。這意味著設計師可以專注于設計所帶來的功能實現或價值提升。

EDA—SiP產業的關鍵一環

設計與仿真流程的進一步融合將是產業抓住市場機會的重要先機。一套經過多個業界領先的廠商共同探討的完整設計流程,將從數字 IC、模擬和混合信號設計、先進封裝三個方向切入的設計體系。

目前在整個 IC 封裝生態系統方面,幾乎所有大型半導體代工廠都提供了先進封裝的版本。這種通過采用參考流程和 PDK 的新方式可以用合理的成本推動新的產業的升級,為芯片封裝市場打開了新的思路。Cadence 自 2007 就已洞察到這一趨勢,并推出了業界第一套完整的 3D IC 全流程設計工具,協助業界進行 3D IC 設計。當前已經有許多知名廠商借助 Cadence 所提供的 EDA 工具設計和制造的產品被廣泛應用于消費電子領域。

隨著全球電子化進程的開展,市場對于 SiP 封裝需求必將呈現爆發式增長,而 EDA 工具作為芯片設計的重要工具,其在功能支持方面也亟待創新與迭代。

具體而言,Cadence 認為未來 EDA 工具的升級將圍繞三個方面展開:

一、系統架構:設計規劃,局部優化,全局最佳化、功能管理

二、設計互連:頂層 Netlist、布局規劃、RDL、Interposer、Die Stackplanning and Layout

三、功能驗證:On/off chip SI、PI、EM、IR、Electrical-Thermal、CMP、Step Height、Local Planarity、Physical Verificationand Test,and DRC

當然,作為業界領先的 EDA 企業,Cadence 也將順應主流趨勢,從產品性能出發,進一步幫助客戶解決在芯片設計方面的難題,以加速產品上市時間。

審核編輯 黃昊宇

-

芯片

+關注

關注

454文章

50438瀏覽量

421904 -

SiP

+關注

關注

5文章

499瀏覽量

105264 -

封裝

+關注

關注

126文章

7789瀏覽量

142734 -

芯片設計

+關注

關注

15文章

1003瀏覽量

54814 -

eda

+關注

關注

71文章

2711瀏覽量

172916

發布評論請先 登錄

相關推薦

低空經濟時代來臨,激光技術如何借東風?

系統級封裝(SiP)技術介紹

COB超微小間距LED顯示屏是什么,它的性價比怎么樣,市場大有可為

電科金倉:數智未來,國產數據庫大有可為

STM32如何詮釋電機控制創新 如何更高效更智能

Scale out成高性能計算更優解,通用互聯技術大有可為

薩科微總經理宋仕強:華強北貿易商來賣國產品牌大有可為

不只專攻國內市場,RISC-V芯片出海大有可為

Sip技術是什么?Sip封裝技術優缺點

這些傳感器,大有可為

金航標kinghelm薩科微slkor

SV-8003VP對講廣播SIP協議網絡SIP話筒主機

SIP-8003V sip網絡話筒主機SIP桌面式對講廣播主機

向SiP過渡,EDA大有可為

向SiP過渡,EDA大有可為

評論