前言

復(fù)雜的設(shè)計(jì)和競(jìng)爭(zhēng)的壓力促使著電子開發(fā)者尋找新的具有競(jìng)爭(zhēng)力的解決辦法。其中一個(gè)重要的方面是把云計(jì)算的能力用于 EDA (電子設(shè)計(jì)自動(dòng)化)工具,從而顯著地增加了生產(chǎn)率。經(jīng)過(guò)十余年的發(fā)展,芯和電子系統(tǒng)設(shè)計(jì)仿真“云平臺(tái)”已經(jīng)成功地應(yīng)用云計(jì)算技術(shù),幫助不同的芯片、封裝、系統(tǒng)用戶應(yīng)對(duì)各種場(chǎng)景的仿真挑戰(zhàn)。

市場(chǎng)概況由于近十年來(lái)的一系列革新,IC設(shè)計(jì)的規(guī)模、復(fù)雜性和種類不斷增加。同時(shí),激烈的競(jìng)爭(zhēng)壓力也促使企業(yè)將所有的資金投入到最大程度,并把所有優(yōu)秀的工程師都投入到生產(chǎn)中去。IT與CAD團(tuán)隊(duì)在有限的場(chǎng)地和條件下,不論企業(yè)的規(guī)模和資源如何,都很難滿足工程師團(tuán)隊(duì)對(duì)仿真的要求。

一個(gè)解決工程效率受限的辦法是把更多的工程師和工具集中在最重要的項(xiàng)目上,但是這樣做會(huì)加劇計(jì)算能力上的不足。如果更多的工程師在同一規(guī)模的基礎(chǔ)設(shè)施上運(yùn)行更多的工具,那么將會(huì)造成更多的計(jì)算資源爭(zhēng)奪,最后會(huì)降低工程效率。即便是在確認(rèn)了基礎(chǔ)架構(gòu)存在問題的情況下,也沒有幾家公司有足夠的資源來(lái)升級(jí)和開發(fā)其硬件環(huán)境,以應(yīng)對(duì)日益增長(zhǎng)的計(jì)算資源需求。即便是擁有大量資源的企業(yè),也無(wú)法在短時(shí)間內(nèi)得到新的硬件來(lái)滿足市場(chǎng)的需求。

為了解決仿真計(jì)算資源的不足,行業(yè)內(nèi)推崇的新解決方案是利用具備云計(jì)算能力的仿真工具。

芯片、封裝、系統(tǒng)大規(guī)模仿真挑戰(zhàn)

1. On-chip電磁仿真

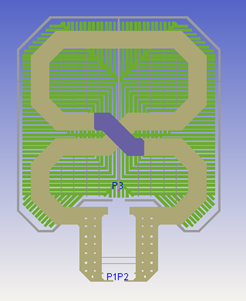

以光芯片為例,當(dāng)前主流的光芯片接口速率為單通道56Gbps,業(yè)界最先進(jìn)的可達(dá)到112Gbps,相信隨著工藝的進(jìn)步和終端用戶對(duì)數(shù)據(jù)吞吐的進(jìn)一步需求,速率會(huì)更高。從無(wú)源參數(shù)提取的角度,這是個(gè)寬頻的應(yīng)用,最高的頻率已經(jīng)達(dá)到毫米波。在如此復(fù)雜的電磁環(huán)境下,寄生參數(shù)的特性具有頻變的特性,同時(shí)為了滿足仿真精度必須要包含空間的電磁耦合。這些需求給電磁仿真器提出了更高的要求。

更重要的是光芯片集成度越來(lái)越高,都在往SOC的方向去實(shí)現(xiàn)。根據(jù)我們實(shí)際項(xiàng)目的經(jīng)驗(yàn),四通道光芯片版圖的尺寸為1至2平方毫米,隨著通道數(shù)增多,則版圖尺寸會(huì)進(jìn)一步的增大。除了必要的電感和互聯(lián)外,版圖還包括了大量的高密度電容結(jié)構(gòu),這些結(jié)構(gòu)將仿真的規(guī)模提高了一個(gè)數(shù)量級(jí)。在端口方面,普通版圖的電磁仿真通常需要50個(gè)左右的端口,而光芯片需要應(yīng)對(duì)的端口數(shù)量翻了幾倍,最高甚至可以達(dá)到500個(gè),求解未知量達(dá)幾百萬(wàn)。這使得設(shè)計(jì)者在有限的硬件資源下很難快速得到精確的仿真數(shù)據(jù)。

圖1. 片上版圖示例

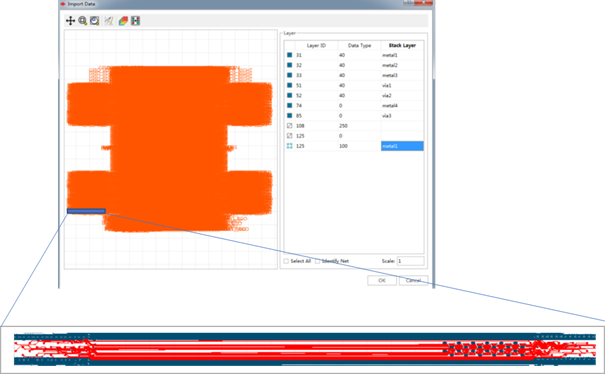

2. 2.5D/3D 先進(jìn)封裝仿真

近年來(lái),隨著HPC、大數(shù)據(jù)、云計(jì)算、物聯(lián)網(wǎng)、3D顯示、網(wǎng)絡(luò)交換等信息技術(shù)的發(fā)展,仿真對(duì)計(jì)算機(jī)性能的要求越來(lái)越高,比如高帶寬,低延遲通信。

為了實(shí)現(xiàn)更高的帶寬,DRAM的每個(gè)I/O引腳數(shù)據(jù)速率逐年都在增加。但由于DRAM晶體管技術(shù)的限制和高靜態(tài)功耗,DRAM的每I/O引腳的數(shù)據(jù)速率不可能提高到10Gb/s以上。因此,需要一種新的解決方案來(lái)實(shí)現(xiàn)terabyte/s帶寬的計(jì)算模塊。

高密度片外存儲(chǔ)器,如高帶寬存儲(chǔ)器(HBM)是最有前途的解決方案之一,它可以由4層DRAM組成,1024個(gè)硅通孔(TSV)I/O和底部的基本邏輯芯片組成。

另外,CPU的封裝從早期的QPF、FCBGA到現(xiàn)在的先進(jìn)封裝,有了更多的變化。對(duì)于CPU芯片來(lái)說(shuō),隨著工藝的發(fā)展,工程師大量利用硅載板或者TSV結(jié)構(gòu)設(shè)計(jì)封裝,如何能夠準(zhǔn)確高效的處理好多個(gè)信號(hào)之間的串?dāng)_問題,也是設(shè)計(jì)的重要一環(huán)。

以鯤鵬920為例,三顆裸芯組成的64核芯片,其中兩顆為計(jì)算DIE,每顆含32個(gè)TSv110核,由4個(gè)核組成一個(gè)簇,8個(gè)簇掛在一個(gè)環(huán)狀總線上,32MB的L3作為一個(gè)節(jié)點(diǎn)也掛在環(huán)上,同樣的存控也作為一個(gè)節(jié)點(diǎn)掛在環(huán)上。三顆裸芯之間由 chip間總線實(shí)現(xiàn)互連。復(fù)雜的工藝以及眾多的信號(hào)線需要一個(gè)強(qiáng)大計(jì)算能力的仿真工具,完成對(duì)信號(hào)和串?dāng)_的評(píng)估。

圖2. 先進(jìn)封裝硅載板的“冰山一角”

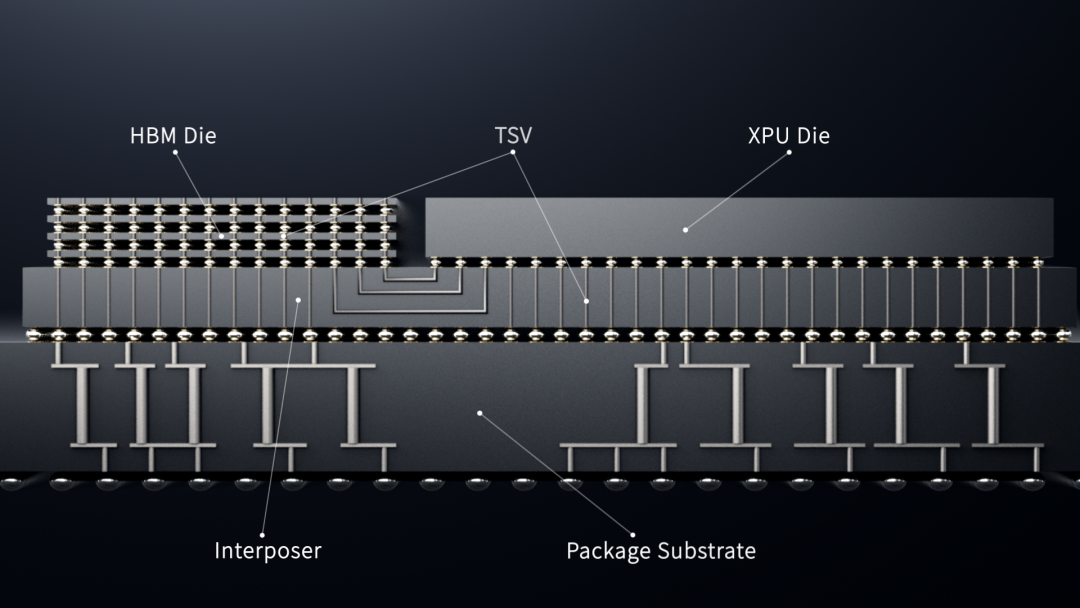

3. Die-Interposer-Package聯(lián)合仿真

隨著摩爾定律逐漸接近物理極限,升級(jí)工藝技術(shù)所帶來(lái)持續(xù)的產(chǎn)品PPA收益日漸受到挑戰(zhàn),從而驅(qū)使系統(tǒng)設(shè)計(jì)人員尋找異構(gòu)集成技術(shù)。通過(guò)異構(gòu)集成來(lái)實(shí)現(xiàn)3DIC和Chiplet的方案,為系統(tǒng)級(jí)功能集成和封裝成本優(yōu)化提供了額外機(jī)會(huì),并開始在HPC、數(shù)據(jù)中心和高端路由器等領(lǐng)域廣泛采用。但是,異構(gòu)集成對(duì)設(shè)計(jì)人員提出了更高的技術(shù)挑戰(zhàn):大量高速SerDes和Memory互連線需要強(qiáng)大的全波三維電磁仿真引擎進(jìn)行快速分析。傳統(tǒng)RC提取工具無(wú)法滿足精度要求,主流電磁仿真引擎工具又無(wú)法解決芯片納米級(jí)別到封裝厘米級(jí)別的跨尺度仿真問題以及異構(gòu)集成超大規(guī)模問題。

如Chiplets包括多個(gè)芯片、硅通道、硅中介層、封裝介質(zhì),芯片中的導(dǎo)體和硅通道之間的相互作用對(duì)電磁場(chǎng)求解器提出來(lái)更高的要求,它必須能夠做超大規(guī)模的全波一體化分析。隨著三維系統(tǒng)集成中I/O數(shù)目的增加,必須要考慮高密度集成在一起的TSV內(nèi)部、TSV與有源電路之間以及TSV與TSV之間的串?dāng)_。高密度也使噪聲耦合加劇。

圖3. 先進(jìn)封裝架構(gòu)圖

在超大規(guī)模一體化分析中,不可避免的問題是如何有效的分析不同尺度的結(jié)構(gòu),芯片-芯片或芯片-硅中介層的互聯(lián)在10微米量級(jí),芯片-封裝的互聯(lián)在100微米量級(jí),而封裝-母板之間在幾百微米或毫米量級(jí),這就對(duì)一體化的電磁場(chǎng)仿真提出來(lái)更多的計(jì)算能力要求。

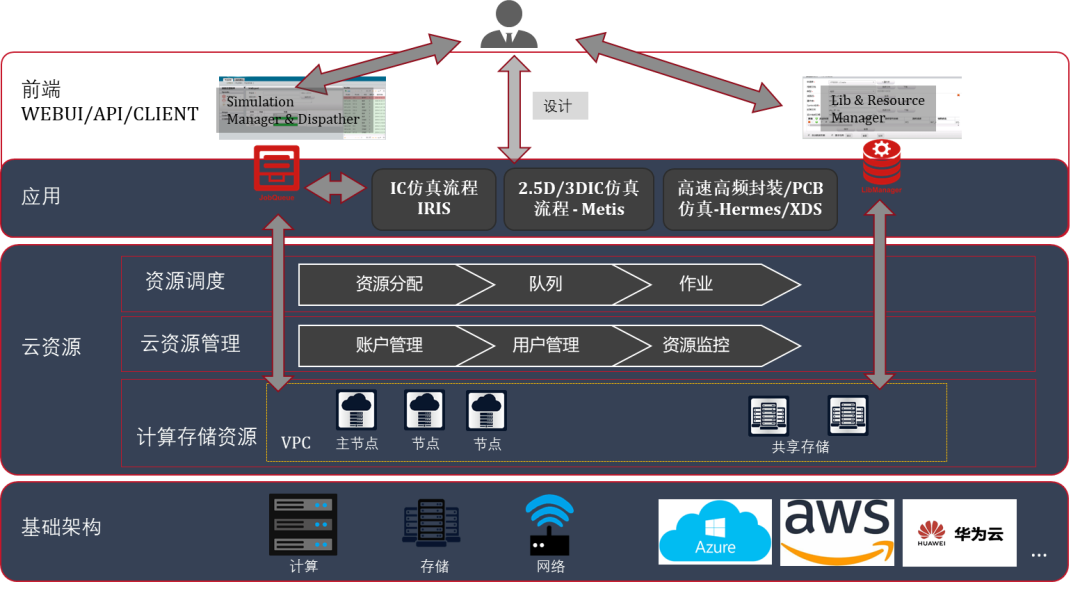

芯片電子系統(tǒng)設(shè)計(jì)仿真“云平臺(tái)”解決方案

圖4. Xpeedic EDA 云平臺(tái)架構(gòu)

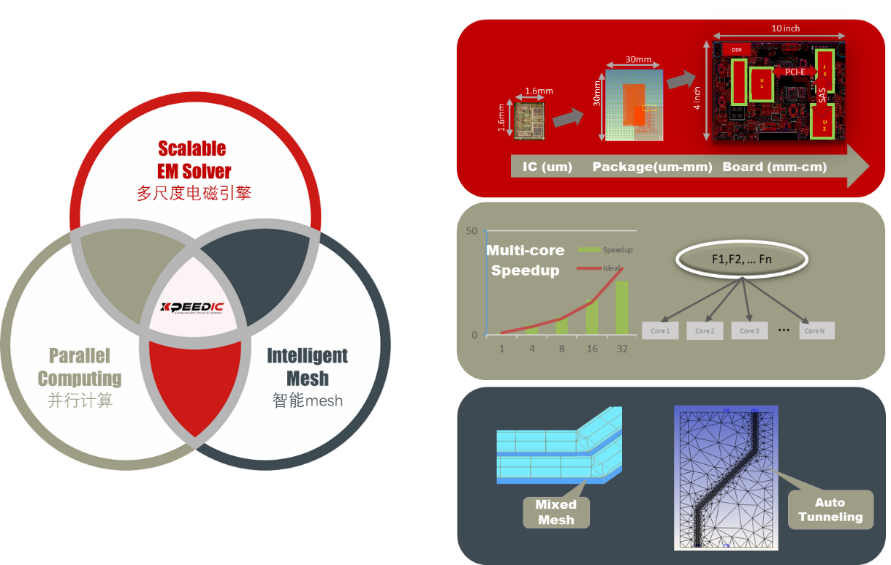

芯和電子系統(tǒng)設(shè)計(jì)仿真“云平臺(tái)”解決方案集成核心差異化的電磁場(chǎng)仿真技術(shù)與軟件、本地集群仿真技術(shù)、MPI仿真技術(shù)、云計(jì)算技術(shù)和分布式集群管理技術(shù),使芯片、封裝、系統(tǒng)設(shè)計(jì)大規(guī)模電磁仿真EDA的資源管理和資源統(tǒng)一調(diào)度使用成為了可能,通過(guò)使用優(yōu)秀的管理系統(tǒng)和管理策略,達(dá)到資源統(tǒng)一分配和管理,不僅增加了各計(jì)算中的資源利用率,降低了計(jì)算中心的維護(hù)和部署成本,同時(shí)發(fā)揮芯和仿真軟件的Intelligent Mesh智能mesh、Scalable EM Solver多尺度電磁引擎、Parallel Computing并行計(jì)算能力,為電子系統(tǒng)設(shè)計(jì)中的芯片,封裝,PCB,系統(tǒng)進(jìn)行大規(guī)模復(fù)雜電磁場(chǎng)仿真提供了可能。

芯和電子系統(tǒng)設(shè)計(jì)仿真“云平臺(tái)”解決方案主要具有以下特點(diǎn):

1.核心競(jìng)爭(zhēng)力-差異化的電磁場(chǎng)仿真工具

圖5. 核心技術(shù)

集成自主產(chǎn)權(quán)的多種尖端電磁場(chǎng)和電路仿真求解技術(shù),提供從數(shù)字、模擬、射頻領(lǐng)域,覆蓋IC、封裝到系統(tǒng)的仿真EDA解決方案:

芯片設(shè)計(jì)仿真產(chǎn)品線:為晶圓廠提供了精準(zhǔn)的PDK設(shè)計(jì)解決方案, 為芯片設(shè)計(jì)公司提供了片上高頻寄生參數(shù)提取與建模的解決方案;

先進(jìn)封裝設(shè)計(jì)仿真產(chǎn)品線:為傳統(tǒng)型封裝和先進(jìn)封裝提供了高速高頻電磁場(chǎng)仿真的解決方案;

高速系統(tǒng)設(shè)計(jì)仿真產(chǎn)品線:為PCB板、組件、系統(tǒng)的互連結(jié)構(gòu)提供了快速建模與無(wú)源參數(shù)抽取的仿真平臺(tái),解決了高速高頻系統(tǒng)中的信號(hào)、電源完整性問題。

該平臺(tái)提供了MOM和FEM兩種電磁仿真求解器技術(shù)。首創(chuàng)革命性的電磁場(chǎng)仿真平臺(tái),突破了傳統(tǒng)矩量法只能做電小尺寸如片上和封裝的局限,解決了電小電大尺寸要不同技術(shù)的問題,用一個(gè)算法既能做芯片仿真,又能做PCB板級(jí)仿真,有效地提升電子產(chǎn)品的設(shè)計(jì)效率,縮短產(chǎn)品上市周期。

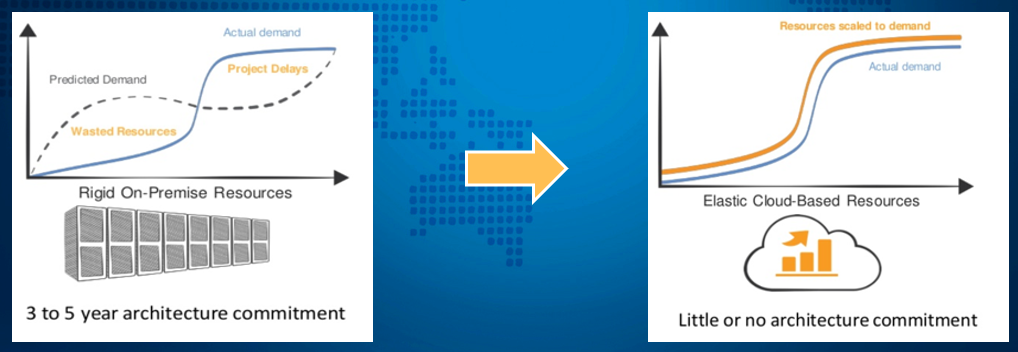

2.云計(jì)算

該平臺(tái)集成了先進(jìn)的多核多機(jī)分布式并行計(jì)算技術(shù),能夠最大程度地利用用戶的硬件計(jì)算資源。同時(shí)該技術(shù)也很好地匹配了云計(jì)算平臺(tái),能利用云端的計(jì)算資源,幫助客戶最大化地提升仿真效率。目前芯和已在亞馬遜AWS和微軟Azure云上建立了EDA仿真平臺(tái)。 具備以下特點(diǎn):1,云的彈性為計(jì)算資源的可變需求提供了完美的適應(yīng);

圖6. 彈性伸縮

2,基于云的 EDA 環(huán)境通過(guò)適應(yīng)計(jì)算資源的按需使用模型來(lái)確保優(yōu)化的業(yè)務(wù)敏捷性;

圖7. 按需計(jì)算

3,更低的IT總支出

內(nèi)部HPC:前期資本支出高,剛性

基于云的HPC:隨用隨付,靈活,需要資源的時(shí)候增加,不需要的時(shí)候減少

圖8. IT維護(hù)靈活

總結(jié)芯和電子系統(tǒng)設(shè)計(jì)仿真“云平臺(tái)”解決方案集成了差異化的電磁場(chǎng)仿真技術(shù)與軟件、本地集群仿真技術(shù)、MPI仿真技術(shù)、云計(jì)算技術(shù)和分布式集群管理技術(shù),使芯片、封裝、系統(tǒng)設(shè)計(jì)大規(guī)模電磁仿真EDA的資源管理和資源統(tǒng)一調(diào)度成為可能。“云平臺(tái)”通過(guò)使用優(yōu)秀的管理系統(tǒng)和管理策略,達(dá)到資源統(tǒng)一分配和管理,不僅增加了各計(jì)算中的資源利用率,降低了計(jì)算中心的維護(hù)和部署成本,同時(shí)發(fā)揮芯和仿真軟件的智能mesh、多尺度電磁引擎、并行計(jì)算能力,加速電子系統(tǒng)設(shè)計(jì)中的大規(guī)模電磁場(chǎng)仿真。

-

云計(jì)算

+關(guān)注

關(guān)注

39文章

7735瀏覽量

137202 -

電子系統(tǒng)

+關(guān)注

關(guān)注

0文章

399瀏覽量

31130 -

芯和半導(dǎo)體

+關(guān)注

關(guān)注

0文章

99瀏覽量

31405

原文標(biāo)題:【解決方案】芯和電子系統(tǒng)設(shè)計(jì)仿真“云平臺(tái)”解決方案

文章出處:【微信號(hào):Xpeedic,微信公眾號(hào):Xpeedic】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

元器件建模與仿真挑戰(zhàn)

modelsim電子系統(tǒng)分析及仿真(第二版)配套光盤

電子系統(tǒng)仿真與MATLAB

ModelSim 電子系統(tǒng)分析及仿真

宇宙射線對(duì)汽車電子系統(tǒng)有什么影響

FPGA在車載電子系統(tǒng)的應(yīng)用

汽車電子系統(tǒng)面臨的狀況

基于Multisim的電子系統(tǒng)設(shè)計(jì)、仿真與綜合應(yīng)用(第2版)

電子系統(tǒng)設(shè)計(jì)所面臨的挑戰(zhàn)是什么

關(guān)于LED驅(qū)動(dòng)解決方案在汽車電子系統(tǒng)的應(yīng)用

電子系統(tǒng)模型分析與SYSTEMVIEW

基于Matlab/Simulink的電力電子系統(tǒng)的建模與仿真

芯和電子系統(tǒng)設(shè)計(jì)仿真云平臺(tái)應(yīng)對(duì)各種仿真挑戰(zhàn)

ECG子系統(tǒng)設(shè)計(jì)主要挑戰(zhàn)及應(yīng)對(duì)方案

芯和電子系統(tǒng)設(shè)計(jì)仿真“云平臺(tái)”解決方案應(yīng)對(duì)各種場(chǎng)景的仿真挑戰(zhàn)

芯和電子系統(tǒng)設(shè)計(jì)仿真“云平臺(tái)”解決方案應(yīng)對(duì)各種場(chǎng)景的仿真挑戰(zhàn)

評(píng)論