瑞薩將目光鎖定在數(shù)據(jù)中心和新的 PCIe Gen6 標準上,創(chuàng)造了“業(yè)界首個 PCIe Gen6 時序解決方案”。

不久之前,瑞薩電子發(fā)布了一系列創(chuàng)新的時鐘緩沖器和多路復用器解決方案,聲稱可為 (IoT)、機器學習 (ML)、云計算、人工智能 (AI) 和數(shù)據(jù)中心等多種應用提供改進的功能。

該系列的一個亮點是這些符合 PCIe 6 標準的解決方案的低附加抖動能力,瑞薩表示,這使得它們無噪音,是數(shù)據(jù)中心應用的理想選擇。考慮到這一點,本文探討了最新的 PCIe 標準版本、瑞薩電子的創(chuàng)新時序解決方案及其對數(shù)據(jù)密集型解決方案的影響。

什么是 PCle 6?PCle 6 與 PCle 3

在深入研究瑞薩的新器件系列之前,讓我們先來看看 PCI-SIG 最近發(fā)布的PCle 6 規(guī)范。該規(guī)范承諾對廣泛的數(shù)據(jù)密集型應用程序進行重大改進,提供新一代的高級功能,使其能夠超越老一代,包括PCle 3。PCle 3 規(guī)范通過 128b/130b 編碼機制展示了高達 8 GT/s 的數(shù)據(jù)速率。

此外,PCI-SIG在這一代中引入了反向通道均衡以減輕通道損耗影響,并且除了編碼機制之外,均衡還允許 PCle 3 維持隨后幾代的速度提升。

總體而言,PCle 3 標準還支持 I/O 虛擬化、設備共享和加速器性能特性,例如原子、緩存提示和事務繞過語義——增強低延遲訪問。為了促進 2010 年智能手機的發(fā)展,PCle 3 提供了低功耗狀態(tài),可實現(xiàn)快速的流量響應、快速的轉(zhuǎn)換時間以及高達 5 pJ/bit 的相對較高的功率效率。

另一方面,PCle 6 規(guī)范通過 x16 配置提供高達 64 GT/s 和高達 256 GB/s 的數(shù)據(jù)速率,超過 PCle 3 的 8 倍。該規(guī)范利用 PCIe 優(yōu)先脈沖幅度調(diào)制和4 級 ( PAM4 ) 信令和基于 Flit(流控制單元)的編碼提供超過兩倍的帶寬增益。

PAM4 信令和編碼 (a) 和 PAM4 錯誤 (b)。圖片由PCI-SIG提供

上圖顯示 PAM4 使用 4 個電壓電平對 2 位數(shù)據(jù)進行編碼。盡管信令技術表現(xiàn)出更高的誤碼率 (BER),但它可以顯著提高信道的覆蓋范圍。

此外,與 PCle 3 不同,PCle 6 提供輕量級的前向糾錯 (FEC) 和循環(huán)冗余校驗 (CRC)功能,可顯著減少與 PAM4 信令相關的 BER 增加。雖然 PCle 6 通過在 Flit 模式下利用更新的數(shù)據(jù)包布局提供附加功能和簡化處理,但它可以通過保持與現(xiàn)有 PCIe 技術一代的互操作性和向后兼容性來保護客戶投資并支持與現(xiàn)有產(chǎn)品的連接。

符合 PCle 6 的時鐘緩沖器和多路復用器的意義

瑞薩電子最近發(fā)布了符合 PCle 6 標準的時鐘緩沖器和多路復用器,以滿足對數(shù)據(jù)中心/云計算和網(wǎng)絡等高數(shù)據(jù)密集型和高速工業(yè)應用日益增長的需求。除了滿足嚴格的 PCIe 6 規(guī)范外,這些新的時鐘緩沖器和多路復用器還為 PCIe 5 實施提供了額外的余量。

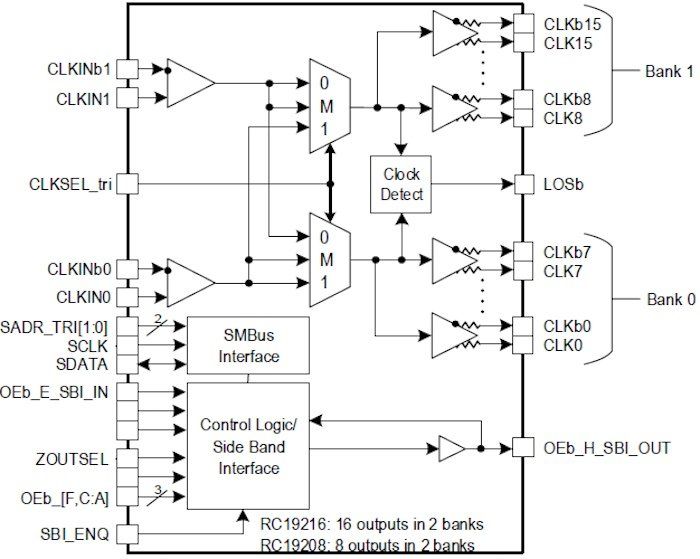

Renesas 的 RC19208A 多路復用器的框圖。圖片由瑞薩電子提供

由于 PCIe 6 標準在最高 100 fs RMS 的低時鐘抖動性能下支持高達 64 GT/s 的更高數(shù)據(jù)速率,因此該標準可用于瑞薩電子的這些最新 RC190xx 時鐘緩沖器和 RC192xx 多路復用器。

此外,這些符合 PCIe 6 標準的時鐘緩沖器和多路復用器具有低至 4 fs RMS 的超低附加抖動規(guī)格,這說明了它們的無噪聲,并根據(jù)下一代行業(yè)標準為面向未來的客戶設計創(chuàng)造了可能的選擇。此外,符合 PCIe 6 標準的時鐘提供多項低功耗特性,例如替代傳統(tǒng) HCSL 的超低功耗高速電流控制邏輯 (LP-HCSL),可節(jié)省高達 85% 的功耗和多鎖相具有省電和節(jié)省電路板功能的環(huán)路 (PLL)。

數(shù)據(jù)中心的低附加抖動能力

如前所述,該系列的一個關鍵特性是低附加抖動能力。總體而言,抖動包括周期信號根據(jù)參考時鐘信號的真實周期的變化或偏差。互連系統(tǒng)設計中的這一重要因素是廣泛不受歡迎的,因為它會導致顯示監(jiān)視器閃爍,影響處理器性能,并對網(wǎng)絡設備之間的無線電信號和傳輸數(shù)據(jù)損失產(chǎn)生不利影響。

一個關鍵的例子是計算機網(wǎng)絡中的數(shù)據(jù)包抖動,它包括延遲變化或與網(wǎng)絡平均延遲的偏差。抖動對各種數(shù)據(jù)密集型應用的負面影響導致對低抖動組件的需求不斷增長。

因此,該系列的超低 4fs PCIe 6 附加抖動能力使符合 PCIe 6 的時序解決方案成為數(shù)據(jù)中心應用的解決方案。此外,低時鐘抖動性能使這些最近發(fā)布的解決方案幾乎無噪音,適合替代傳統(tǒng)嘈雜的數(shù)據(jù)中心計算組件。

審核編輯 黃昊宇

-

時鐘緩沖器

+關注

關注

2文章

92瀏覽量

50835 -

數(shù)據(jù)中心

+關注

關注

16文章

4688瀏覽量

71956 -

PCIe

+關注

關注

15文章

1217瀏覽量

82445 -

多路復用器

+關注

關注

9文章

869瀏覽量

65283

發(fā)布評論請先 登錄

相關推薦

東芝推出最新多路復用器/解復用器開關

TS3DV642 12通道1:2多路復用器/多路解復用器數(shù)據(jù)表

DS100MB201雙通道2:1/1:2多路復用器/緩沖器數(shù)據(jù)表

DS100MB203 10.3125 Gbps雙通道2:1/1:2多路復用器/緩沖器數(shù)據(jù)表

DS42MB100 4.25 Gbps 2:1/1:2 CML多路復用器/緩沖器數(shù)據(jù)表

DS64MB201雙通道2:1/1:2多路復用器/緩沖器數(shù)據(jù)表

DS42MB200雙通道4.25 Gbps 2:1/1:2 CML多路復用器/緩沖器數(shù)據(jù)表

DS40MB200雙通道4 Gbps 2:1/1:2 CML多路復用器/緩沖器數(shù)據(jù)表

DS25MB200雙通道信號調(diào)理多路復用器和扇出緩沖器數(shù)據(jù)表

DS25MB100 2.5 Gbps 2:1/1:2 CML多路復用器/緩沖器數(shù)據(jù)表

SCAN15MB200雙通道1.5 Gbps 2:1/1:2 LVDS多路復用器/緩沖器數(shù)據(jù)表

第一個 PCle 6 時鐘緩沖器和多路復用器“靜音”數(shù)據(jù)中心

第一個 PCle 6 時鐘緩沖器和多路復用器“靜音”數(shù)據(jù)中心

評論