物理設計工具的作用是采用自動布局布線技術或人工編輯的方法實現集成電路的版圖設計。

自動布局布線通常分為布局規劃(Floor Planning)、物理布局(Placement)、時鐘樹綜合(Clock Tree Synthesis,CTS)、物理布線(Routing)等幾個步驟。

布局規劃在一定幾何約束條件下,確定芯片面積及優化模塊形狀,決定標準單元、I/O Pad和宏單元的位置。常用的布局規劃算法有布局尺寸變化算法、基于群生長擺放模塊的方法、仿真退火迭代算法,以及將問題映射為等式集合進行解析求解的方法等。

物理布局又稱為總體布局和詳細布局,是指將標準單元擺放到版圖核心區域的單元行上且滿足設計規劃的合理位置,使得芯片線長、時序、擁擠度、功耗等多個性能目標得到最優化。布局問題屬于非確定性問題,很難找到一個多項式時間復雜度算法來得到最優解。在實際應用中通常尋求可行解來作為最優解的近似。常見的解決布局問題的算法可以分為圖論算法(深度優先搜索、關鍵路徑等)、確定性算法(線性規劃、非線性規劃、動態規劃等)、隨機算法(仿真退火等)3種。

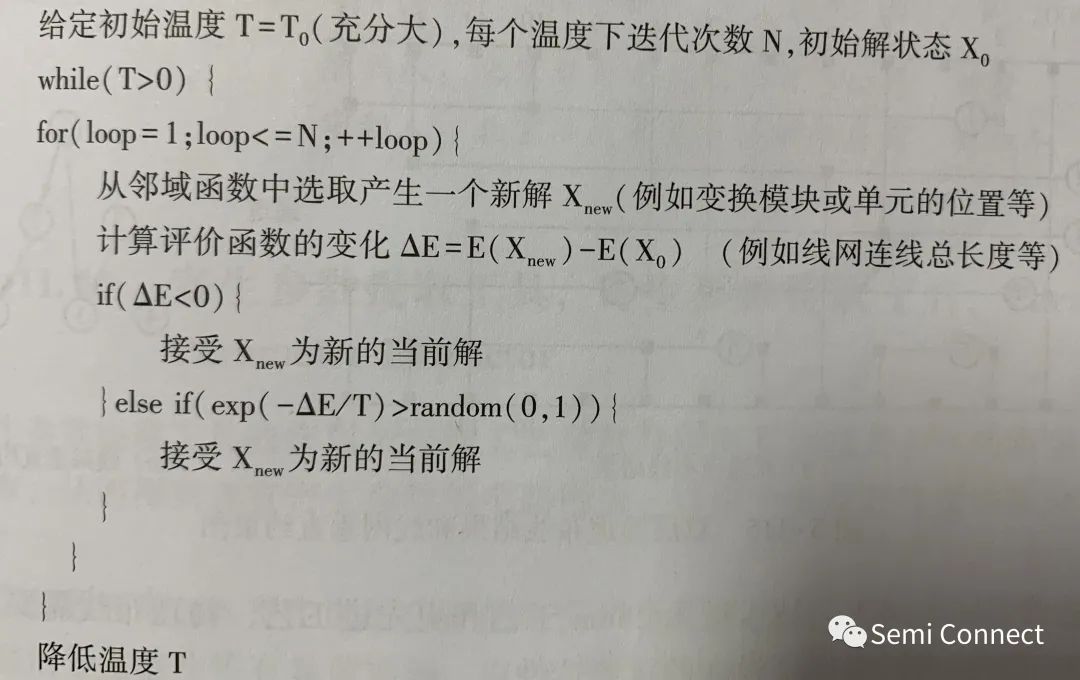

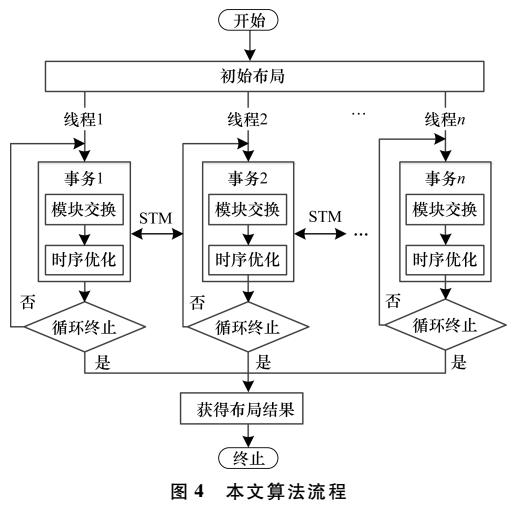

利用仿真退火算法求解布局問題的流程如下。

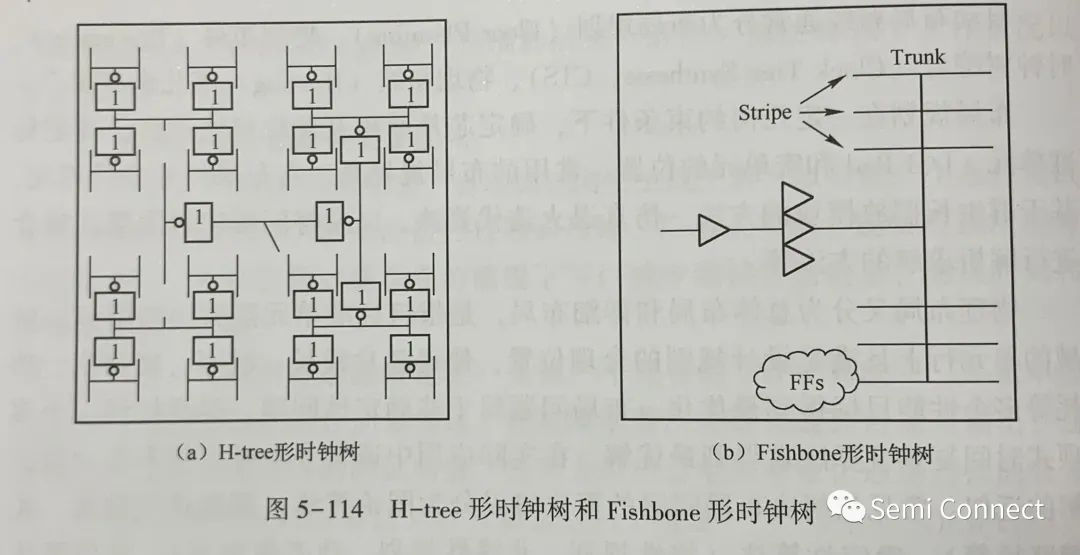

時鐘樹綜合在時鐘電路中插入緩沖器單元,將時鐘信號傳遞到各個同步單元(觸發器等),其優化目標在于盡量減少時鐘路徑延遲和時鐘偏差。常見的時鐘樹綜合算法有H- Tree 算法、Fishbone算法等,如圖5-114所示。為了減少時鐘偏差和受參數變化的影響,高性能的時鐘系統設計還會采用網形(Mesh)結構,但同時也會占用更多的布線資源和面積。

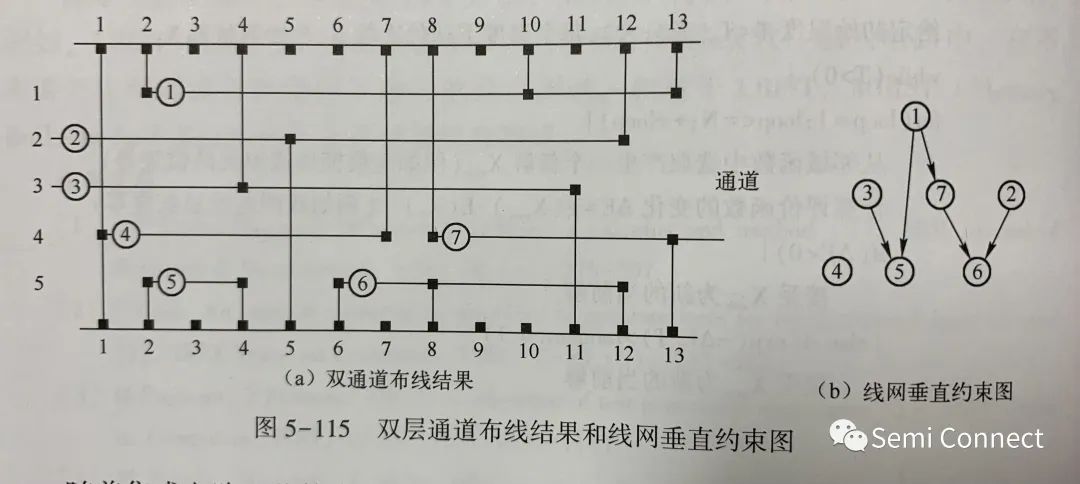

物理布線階段分為總體布線和詳細布線兩個步驟:總體布線把網線合理地分配在合適的布線區域,盡量避免局部擁擠;詳細布線實現線網通過布線層連線和通孔的具體連接,避免線網的短路、開路錯誤。根據布線區域和線網端點在區域中的分布情況有可以把詳細布線分為通道布線、開關盒布線和區域布線。雙層通道布線結果和線網垂直約束圖如圖5-115所示。

隨著集成電路工藝技術進入28nm工藝和更先進工藝,物理布線需要支持多重曝光工藝技術,以保證設計的可制造性。

在集成電路的版圖設計中,人工編輯主要依靠版圖編輯工具。版圖編輯工具提供一個以多邊形為基礎的二維幾何圖形創建與編輯環境,根據集成電路版圖的特點及設計規則提供交互式的編輯與操作功能,最終以GDS或者OASIS等格式輸出物理版圖。版圖編輯工具的基本功能如下。

(1)支持層次化編輯。

(2)與工藝綁定,并以一定的顏色、線型和填充方式區分不同的工藝層。

(3)支持矩形、多邊形、路徑等基本圖形的創建、縮放、拉伸等。

(4)采用參數化單元(Parameterized Cell),減少重復輸入。

隨著集成電路設計方法學的發展,對版圖編輯工具的要求也越來越高,主要體現在以下方面。

(1)與電路圖的交互,由此產生了電路圖驅動版圖(Schematic-Driven Layout,SDL)和約束驅動版圖(Constraint Driven Layout,CDL)兩項技術。

(2)模擬和數字集成電路的融合,衍生出模擬電路的自動布局和自動布線技術。

(3)設計規模的急劇膨脹對工具效率提出更高要求,催生快速顯示、多線程查詢等技術。

(4)工藝技術的發展需要新的版圖編輯技術,例如鰭式場效應晶體管(FinFET)的設計需要多格點對齊技術等。

審核編輯:湯梓紅

-

集成電路

+關注

關注

5381文章

11381瀏覽量

360850 -

布線

+關注

關注

9文章

766瀏覽量

84289 -

物理設計

+關注

關注

0文章

5瀏覽量

6869

原文標題:可編程邏輯電路設計—物理設計工具

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

HFSS 仿真算法及其應用場景詳解:有限元算法、積分方程算法、PO算法

怎么用模擬退火算法求全局最優解?

可支持任意流程的微機電系統設計工具技術

基于LabVIEW仿真實現TSP問題的模擬退火算法

基于退火算法的非合作對策求解

FPGA并行時序驅動布局算法

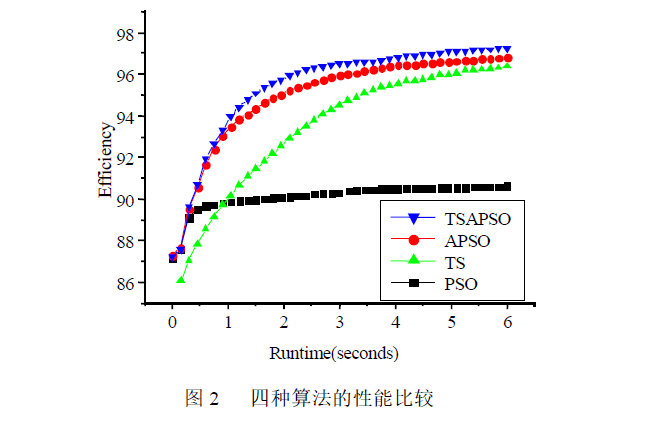

如何使用禁忌退火粒子群算法解決火力分配的問題

【優化選址】基于模擬退火結合粒子群算法求解分布式電源定容選址問題matlab源碼

物理設計工具的作用 利用仿真退火算法求解布局問題的流程

物理設計工具的作用 利用仿真退火算法求解布局問題的流程

評論