你知道嗎?計算機和計算器使用觸發器來進行記憶。一定數量的觸發器組合將產生一定數量的內存。觸發器是使用邏輯門形成的,而邏輯門又由晶體管制成。

觸發器是電子設備內存中的基本構建塊,每個觸發器可以存儲一位數據。觸發器有兩個穩定狀態,因此它們是雙穩態多諧振蕩器,兩個穩定狀態分別是高(邏輯 1)和低(邏輯 0)。

之所以使用術語觸發器,是因為它們可以在控制信號的影響下在狀態之間切換,即它們可以“翻轉”到一個狀態并“翻轉”回另一個狀態。其主要特點包括:

觸發器是二進制存儲設備,因為它們可以存儲二進制數據(0或1)。

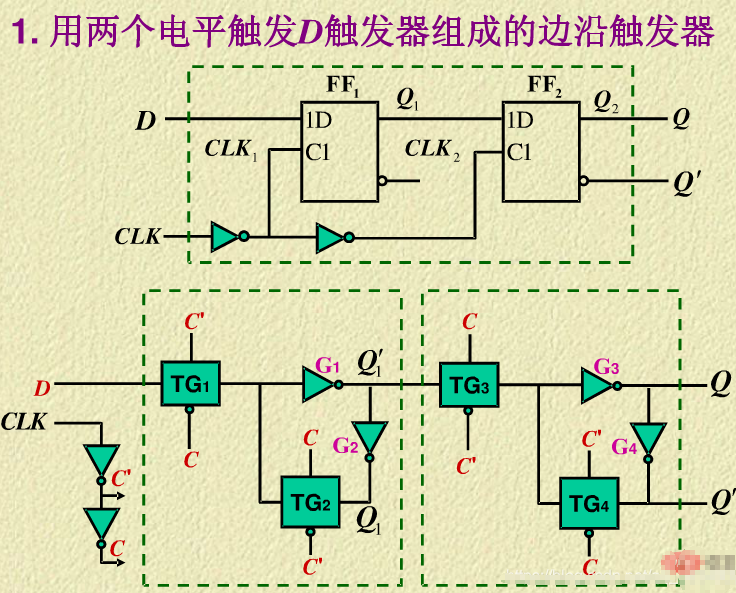

觸發器是邊沿敏感或邊沿觸發設備,即它們對轉換敏感,而不是對時鐘信號的持續時間或寬度敏感。

也被稱為信號變化敏感器件,即時鐘信號電平的變化會帶來觸發器輸出的變化。

工作方式取決于時鐘脈沖。

也用于控制數字電路的功能,因為可以根據狀態改變數字電路的操作。

觸發器的種類

一些最常見的觸發器包括SR觸發器、D觸發器、JK觸發器和T觸發器,下面分別來介紹下。

1、SR觸發器

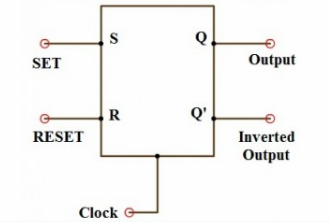

SR觸發器是所有觸發器中的基本觸發器,所有其他觸發器都是在SR觸發器的基礎上開發的。SR觸發器如下圖所示:

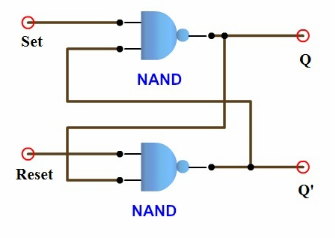

SR代表SET和RESET,這也可以稱為RS觸發器。不同的是RS是反相SR觸發器。任何觸發器都可以使用邏輯門構建。使用NAND和NOR門,因為它們是通用門。

下面是使用NAND門的SR觸發器。

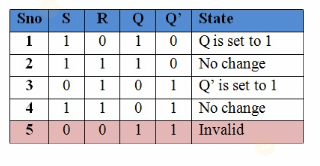

SR觸發器的真值表:

工作過程:

從上面的真值表可以清楚地看出,SR觸發器將在四個條件下置位或復位。

對于最后一個條件,它將處于無效狀態。

當S=1且R=0時,SR觸發器將被設置,如果S=1且R=1,則觸發器會記住先前的狀態。

當S=0且R=1時,觸發器將被復位,如果S=1且R=1,則它會記住之前的狀態。

但是當兩個輸入都為零時,SR觸發器將處于不確定狀態,其中Q和Q'將相同,這是不允許的。

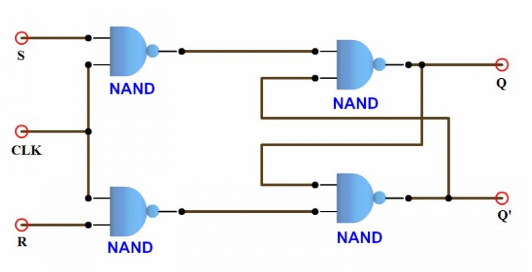

通過向現有觸發器添加門額外的門來避免這種不確定狀態。這稱為時鐘或門控SR觸發器,這僅產生高時鐘脈沖的輸出。以下是使用NAND門的時鐘SR觸發器的電路:

2、D觸發器

在SR觸發器中發生了一個不確定的狀態,這可以通過使用D觸發器來避免。這里D代表“數據(Data)”。它由SR觸發器構成,其中計時SR觸發器的兩個輸入 (S&R) 連接到反相器。

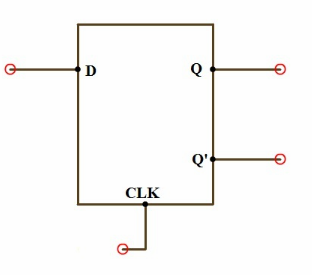

D觸發器是使用最廣泛的觸發器之一,它有一個時鐘信號(Clk)作為輸入,數據(D)作為另一個輸入。有兩個輸出,這些輸出相互補充。D觸發器的符號如下圖所示。

真值表圖如下:

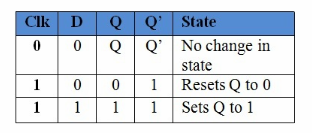

使用NAND門的D觸發器如下圖所示:

工作過程:

D觸發器將根據時鐘信號工作。

當時鐘為低電平時,觸發器的輸出不會發生變化,即它會記住先前的狀態。

當時鐘信號為高電平并且在其數據引腳上接收到任何數據時,它會改變輸出狀態。

當數據為高時,Q復位為0,如果數據為低,Q被設置為0。

可以使用D觸發器構建主從D觸發器。

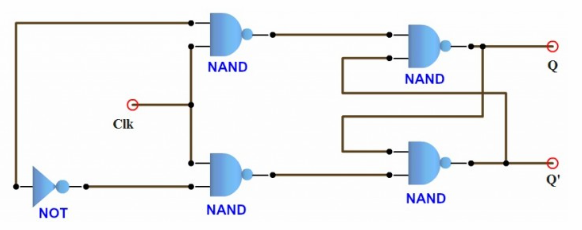

3、JK觸發器

JK觸發器以發明IC的電氣工程師Jack Kilby的名字命名。

JK觸發器是對SR觸發器的修改。其中J輸入類似于SR觸發器的置位輸入,而K輸入類似于SR觸發器的復位輸入。SR觸發器 (S=R=1) 中不允許的條件J=K=1被解釋為切換命令。

在JK觸發器中,共有:

兩個數據輸入J和K。

一個時鐘信號輸入 (CLK)。

兩個輸出Q和Q'。

JK觸發器的符號如下所示:

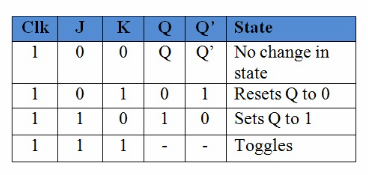

真值表圖如下所示:

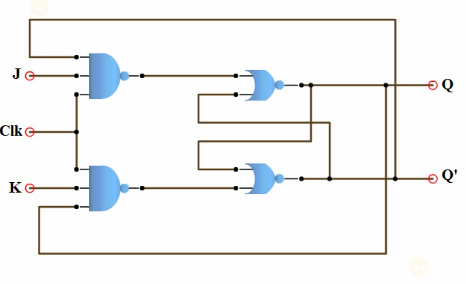

使用門的JK觸發器的電路如下所示,它類似于修改后的NAND SR觸發器:

工作過程:

當 J為低且K為低時,Q返回其先前的狀態值,即它保持當前狀態。

當J為低而K為高時,觸發器將處于復位狀態,即Q=0,Q'=1。

當J為高而K為低時,觸發器將處于置位狀態,即Q=1,Q'=0。

當J為高且K為高時,觸發器將處于Toggle狀態或翻轉狀態,這意味著輸出將補充先前的狀態值。

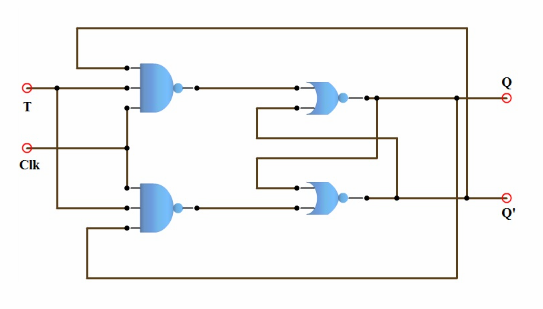

4、T觸發器

T觸發器也被稱為“Toggle Flip – flop”,切換是在存在時鐘輸入信號的情況下將輸出更改為先前狀態的補碼。

T觸發器共有:

T輸入。

一個時鐘信號輸入 (CLK)。

兩個輸出Q和Q'。

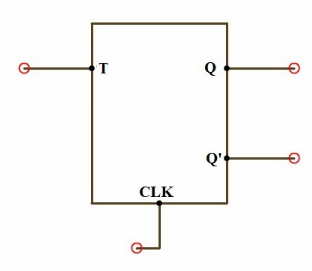

T型觸發器的符號如下圖所示:

其實可以通過使用任何其他觸發器來構造一個T觸發器。

SR觸發器:通過將S 觸發器的輸出反饋連接到輸入 (S & R)。

D觸發器:將Q'連接到其D觸發器的數據輸入端作為反饋路徑。

JK觸發器:通過將JK觸發器的J&K輸入組合成單輸入,可以設計出T觸發器。

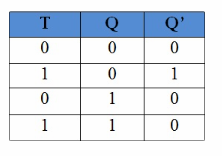

真值表如下圖所示:

由NAND JK觸發器制成的T觸發器電路如下圖所示。

工作過程:

當T輸入為低電平時,T觸發器的下一個狀態與當前狀態相同,即保持當前狀態。

T=0并且當前狀態=0然后下一個狀態=0。

T=0并且當前狀態=1然后下一個狀態=1。

當T輸入為高時,T觸發器的下一個狀態被切換,即它與時鐘轉換時當前狀態的補碼相同。

T=1并且當前狀態=0然后下一個狀態=1。

T=1并且當前狀態=1然后下一個狀態=0。

關于觸發方式

觸發器輸出的變化可以通過輸入信號的微小變化來完成,這種微小的變化可以在時鐘脈沖的幫助下完成,而該時鐘脈沖稱為觸發脈沖。

所以觸發器也被稱為“觸發”,當觸發脈沖施加到輸入時,會導致輸出發生變化。觸發器是寄存器和計數器中的基本組件,它們以多位數字的形式存儲數據。連接數個觸發器構成時序電路,所有這些觸發器都需要觸發脈沖。施加到輸入的觸發脈沖的數量決定了計數器中的數量。

目前主有兩種觸發方式:電平觸發和邊沿觸發。

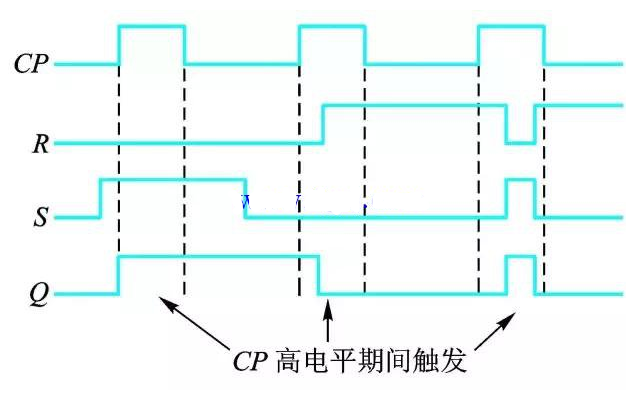

電平觸發

根據輸入的有效電平改變輸出狀態的觸發過程稱為“電平觸發”。電平觸發有兩種類型,它們是:

高電平觸發。

低電平觸發。

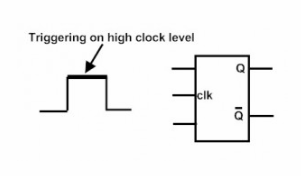

1、高電平觸發

在高電平觸發中,觸發器的輸出僅在其使能輸入處于高電平狀態即邏輯高或邏輯1時發生變化。高電平觸發的符號表示如下所示:

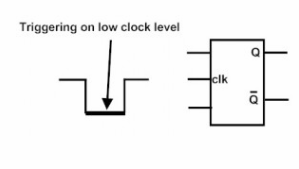

2、低電平觸發

在低電平觸發中,觸發器的輸出僅在其使能輸入處于低狀態即邏輯低或邏輯0時才發生變化。低電平觸發的符號表示如下所示,低電平觸發通常由時鐘輸入上的氣泡標識。

邊沿觸發

在邊沿觸發中,僅當輸入出現在時鐘脈沖的任一跳變時,輸出才會改變,即從低到高(0 到 1)或從高到低(1 到 0)。

邊沿觸發也有兩種類型,它們是:

正邊沿觸發。

負邊沿觸發。

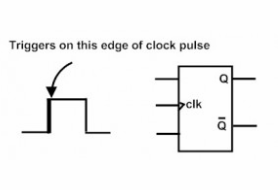

1、正邊沿觸發

在正邊沿觸發中,僅當輸入處于時鐘脈沖輸入的正邊沿時,輸出才會改變,即從低到高(0 到 1)的轉換。當需要觸發器在低電平到高電平轉換狀態下響應時,使用正邊沿觸發方法。正邊沿觸發沿觸發的符號表示如下所示。

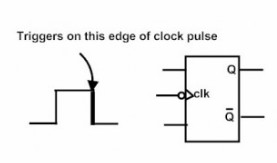

2、負邊沿觸發

在負邊沿觸發中,只有當輸入處于時鐘脈沖輸入的負邊沿時,輸出才會改變,即從高電平到低電平(1 到 0)的轉換。當需要觸發器在高電平到低電平轉換狀態下響應時,使用負邊沿觸發方法。負邊沿觸發的符號表示如下所示:

為什么說邊沿觸發優于電平觸發?

最好使用邊沿觸發而不是電平觸發。這是因為對于電平觸發觸發器的特定情況,電平觸發可能會導致電路不穩定,其中在觸發器輸出發生變化的同時,時鐘脈沖被提供給輸入。從輸出到輸入的反饋會導致這種不穩定性。為了避免這種不穩定性,使用了邊沿觸發觸發器。

觸發器的應用

觸發器的應用非常廣泛,可以說在數字電路中很是常見,下面簡單整理一些:

寄存器:由于觸發器有兩個穩定狀態,所以將它們用于寄存器等存儲元件中,用于數據存儲。通常在計算機等電子設備中使用寄存器。

計數器:相互連接的觸發器組用作計數器,對事件發生的增量或減量進行計數。

分頻電路:觸發器用作分頻電路,將輸入頻率精確地分成一半。分頻電路用于規范電子電路的頻率。

數據傳輸:使用移位寄存器(一種特殊類型的寄存器)將數據從一個觸發器傳輸到另一個觸發器,它們以特定的順序連接。

總結

簡單來說,觸發器就是同步時序電路的構建塊。它有兩個穩定狀態,可以存儲一位信息。觸發器將具有時鐘信號,它們的狀態根據時鐘脈沖而變化,這些設備將具有兩種狀態和一條反饋路徑。

需要注意的是,觸發器是邊緣敏感的,當時鐘信號從低到高或從高到低轉換時,它們將改變它們的狀態。在時鐘信號從0到1或1到0的轉換之后,即當時鐘處于恒定的0或1時,即使輸入發生變化,狀態也保持不變。

-

晶體管

+關注

關注

77文章

9634瀏覽量

137844 -

D觸發器

+關注

關注

3文章

164瀏覽量

47862 -

觸發器

+關注

關注

14文章

1995瀏覽量

61051

發布評論請先 登錄

相關推薦

施密特觸發器,施密特觸發器是什么意思

同步觸發器的觸發方式和空翻問題

什么是邊沿觸發器_邊沿D觸發器介紹

觸發器的常用觸發方式

觸發器的種類與觸發方式

觸發器的種類與觸發方式

評論