隨著集成電路工藝進(jìn)入納米尺度,復(fù)雜工藝的采用使得工藝偏差日益嚴(yán)重。工藝偏差是指在集成電路制造過程中,電路幾何和電學(xué)參數(shù)的隨機波動。例如,采用193nm波長光源的亞波長光刻造成硅片圖形偏差,化學(xué)機械拋光導(dǎo)致銅互連線高度嚴(yán)重偏差,摻雜的隨機波動導(dǎo)致器件參數(shù)的偏差等。工藝偏差使得集成電路設(shè)計性能與制造后的性能具有較大差異并呈現(xiàn)隨機分布。工藝缺陷如塵埃導(dǎo)致的斷路和短路也會使電路出現(xiàn)功能失效。

成品率設(shè)計主要是通過早期的設(shè)計手段來降低工藝缺陷和工藝偏差對電路性能的影響,提高電路制造后的成品率。相比來說,可制造性設(shè)計則更偏向于通過設(shè)計手段,解決芯片制造中可能存在的化學(xué)機械拋光平整性、亞波光光刻等制造苦難。

成品率設(shè)計首先需要建立工藝參數(shù)的隨機模型以及支持隨機參數(shù)的器件模型。在此基礎(chǔ)上,通過電路仿真可以支持電路的成品率分析和優(yōu)化;通過建立單元電路的隨機延時模型,支持數(shù)字電路的成品率分析和優(yōu)化。

模擬電路對工藝偏差更為敏感,因此設(shè)計者很早就已經(jīng)考慮尺度失配對電路性能的影響;而在成品率設(shè)計中,還需要進(jìn)一步考慮工藝參數(shù)偏差對設(shè)計的影響。模擬電路設(shè)計者一般通過增加裕量、中心化設(shè)計等方法來提高電路成品率。近年也有直接以成品率為優(yōu)化目標(biāo)的模擬電路自動成品率優(yōu)化方法的相關(guān)研究。Cadence公司的Virtuoso設(shè)計環(huán)境提供了多工藝角優(yōu)化、成品率優(yōu)化等工具。

數(shù)字電路的成品率設(shè)計分為眾工藝角優(yōu)化方法和統(tǒng)計優(yōu)化方法兩類。眾工藝角設(shè)計是傳統(tǒng)數(shù)字電路抗工藝偏差設(shè)計的延伸,通過引入更多工藝角,經(jīng)過優(yōu)化來保證電路在眾多工藝角下都能滿足性能要求,提升電路的成品率。Synopsys公司的IC Compiler、Cadence公司的Innovus均提供了眾工藝角優(yōu)化功能。基于統(tǒng)計的優(yōu)化方法目前發(fā)展得尚不成熟。IBM公司最早開發(fā)了統(tǒng)計時序分析的工具,并基于該工具來進(jìn)行電路成品率優(yōu)化。但基于統(tǒng)計的成品率分析和優(yōu)化方法還沒有被大規(guī)模使用。Synopsys公司和Cadence公司最近也發(fā)布了統(tǒng)計時序分析工具,基于統(tǒng)計的分析及成品率優(yōu)化方法也許會成為未來的發(fā)展趨勢。

成品率增長技術(shù)(Yield Enhancement)包含的內(nèi)涵越來越豐富。傳統(tǒng)上是指在不犧牲面積的前提下,通過冗余通孔插入、互連展寬等技術(shù)來減少由于塵埃缺陷引起的短路、斷路以及通孔缺陷引起的斷路失效。成品率增長技術(shù)現(xiàn)在涵蓋了更多的內(nèi)容,如光學(xué)鄰近效應(yīng)校正(Optical Proximity Correction,OPC)、針對化學(xué)機械拋光的啞元金屬插入、光刻熱點檢測及修正等可制造性設(shè)計方法,以及前面提到的各種成品率優(yōu)化方法等。

為了應(yīng)對工藝偏差引起的成品率的嚴(yán)重下降,近年來還提出了一些可調(diào)或自修復(fù)的電路設(shè)計方法。這些方法在電路設(shè)計階段引入一些可調(diào)單元來調(diào)整電路的偏置、驅(qū)動能力和負(fù)載等;在電路制造后,根據(jù)電路的實際偏差,通過人工測試或自動測量電路性能,對可調(diào)單元進(jìn)行手工或自動調(diào)整,以提高電路性能和成品率。這種設(shè)計方法由于可以在制造后調(diào)整,可以降低為應(yīng)對工藝偏差引入的不必要的面積和功耗開銷。

成品率設(shè)計是集成電路進(jìn)入納米尺度后必須采用的設(shè)計方法,只有在設(shè)計階段考慮工藝偏差的影響,才能有效地提高集成電路的成品率。隨著工藝尺寸的進(jìn)一步縮小,成品率設(shè)計方法將變得更加重要。

審核編輯:劉清

-

集成電路

+關(guān)注

關(guān)注

5382文章

11396瀏覽量

360950 -

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42581 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

514瀏覽量

44074

原文標(biāo)題:可編程邏輯電路設(shè)計—成品率設(shè)計

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

邏輯電路芯片-組合邏輯電路芯片-時序邏輯電路芯片

什么是現(xiàn)場可編程邏輯陣列?它有哪些特點和應(yīng)用?

高性能沖擊可編程陣列邏輯電路數(shù)據(jù)表

標(biāo)準(zhǔn)高速可編程陣列邏輯電路數(shù)據(jù)表

高性能沖擊可編程陣列邏輯電路數(shù)據(jù)表

高性能Impact X可編程陣列邏輯電路TIBPAL16C數(shù)據(jù)表

FPGA零基礎(chǔ)學(xué)習(xí)系列精選:半導(dǎo)體存儲器和可編程邏輯器件簡介

現(xiàn)場可編程門陣列的基本結(jié)構(gòu)和優(yōu)缺點

現(xiàn)場可編程門陣列的原理和應(yīng)用

現(xiàn)場可編程門陣列簡介

現(xiàn)場可編程門陣列是什么

可編程邏輯器件的特征及優(yōu)勢科普

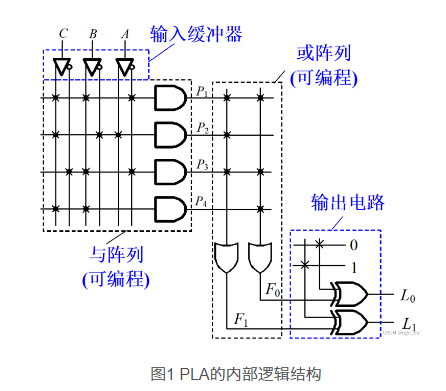

可編程邏輯陣列PLA內(nèi)部邏輯結(jié)構(gòu)示意

可編程邏輯電路之成品率設(shè)計簡介

可編程邏輯電路之成品率設(shè)計簡介

評論