做項(xiàng)目實(shí)現(xiàn)某個(gè)feature時(shí)經(jīng)常會(huì)考慮一個(gè)問題,硬件實(shí)現(xiàn)還是軟件實(shí)現(xiàn),還是軟硬件結(jié)合。

要想回答好這個(gè)問題,就要理解硬件和軟件的各自的優(yōu)劣勢。

優(yōu)劣勢

軟件程序其實(shí)是運(yùn)行在CPU上的,所有的程序都要分解為一條一條的機(jī)器指令去運(yùn)行。CPU作為一種通用的架構(gòu),它最大的優(yōu)勢自然也是通用,擅長復(fù)雜的邏輯和運(yùn)算操作。但也因?yàn)槠渫ㄓ玫募軜?gòu),使得CPU在某些特定的應(yīng)用場景性能不足,比如視頻渲染,不然也不會(huì)出現(xiàn)GPU。

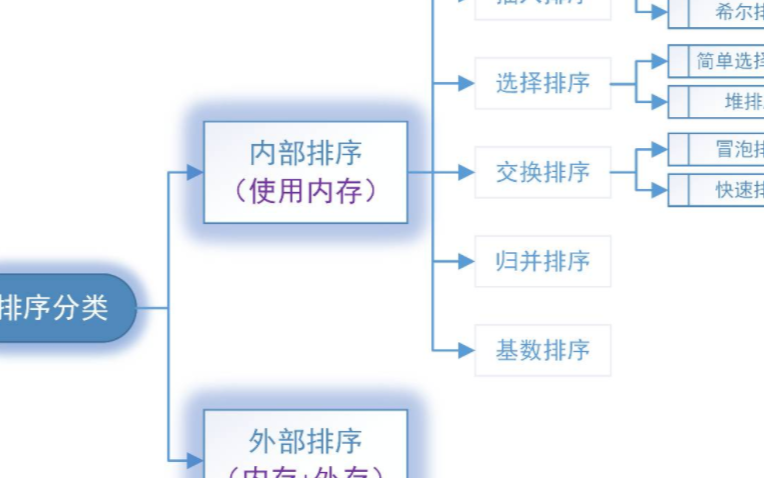

FPGA則恰恰相反。FPGA非常擅長并行計(jì)算,同時(shí)能夠提供極低的延遲。但是卻不擅長復(fù)雜的邏輯和數(shù)學(xué)運(yùn)算操作,比如調(diào)度算法,甚至某些看起來比較簡單的排序算法在FPGA上實(shí)現(xiàn)也比較麻煩。

軟硬件結(jié)合的經(jīng)典設(shè)計(jì)

計(jì)算機(jī)系統(tǒng)中的地址翻譯可以看做一個(gè)經(jīng)典設(shè)計(jì)。

地址翻譯是將虛擬地址轉(zhuǎn)換為物理地址。這個(gè)過程是通過查找表(頁表)的方式實(shí)現(xiàn)的。頁表中存儲(chǔ)著物理地址,那么要存儲(chǔ)哪些物理地址,哪個(gè)物理地址存儲(chǔ)在哪一個(gè)表項(xiàng),是一個(gè)比較復(fù)雜的邏輯,這個(gè)過程是通過操作系統(tǒng)即軟件來實(shí)現(xiàn)的。當(dāng)程序或者進(jìn)程在運(yùn)行期間需要訪問某一個(gè)地址,我們希望用最快的速度來實(shí)現(xiàn)地址翻譯,這個(gè)過程用到的便是硬件,硬件讀取頁表的內(nèi)容獲得物理地址即可。

最后回到最初的問題,用硬件還是用軟件,一句話總結(jié),復(fù)雜的對(duì)性能要求較低的交給軟件,簡單的性能要求高的交給硬件。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21678瀏覽量

602037 -

硬件

+關(guān)注

關(guān)注

11文章

3260瀏覽量

66132 -

排序算法

+關(guān)注

關(guān)注

0文章

52瀏覽量

10053

原文標(biāo)題:硬件(FPGA)vs 軟件

文章出處:【微信號(hào):FPGA開發(fā)之路,微信公眾號(hào):FPGA開發(fā)之路】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

Python實(shí)現(xiàn)的常見內(nèi)部排序算法

十大排序算法總結(jié)

基于FPGA的中值濾波算法實(shí)現(xiàn)

算法的原理是什么?基數(shù)排序是如何實(shí)現(xiàn)的?

雷達(dá)視頻積累算法在FPGA上的實(shí)現(xiàn)

在FPGA上實(shí)現(xiàn)CRC算法的程序

淺談希爾排序算法思想以及如何實(shí)現(xiàn)

php版冒泡排序是如何實(shí)現(xiàn)的?

FPGA實(shí)現(xiàn)雙調(diào)排序算法的探索與實(shí)踐

排序算法在FPGA上的實(shí)現(xiàn)

排序算法在FPGA上的實(shí)現(xiàn)

評(píng)論