實現可編程邏輯電路可以選擇三種主要的技術,它們有兩種主要的特性:是否可重新編程以及是否易失。我們將介紹三種主要的器件,它們是支持可編程電路的技術基礎: 反熔絲、雙柵晶體管和基于SRAM的可編程電路。

01

反熔絲

反熔絲的概念至少可以追溯到1957年,那時人們考慮將其用在存儲器中。當一個編程電流加在反熔絲器件上時,它會由正常的開路狀態變為短路狀態。它可以通過將一層絕緣層加在兩層導電層中間實現,當通以大電流時會在較小的面積上產生較大的功率耗散,會熔斷絕緣層。這是一種可單次編程的技術,因為編程后絕緣材料已被破壞不可恢復。制造反熔絲器件可以采用兩種主要結構:多晶硅擴散區結構和金屬-金屬反熔絲結構。

02

雙柵晶體管

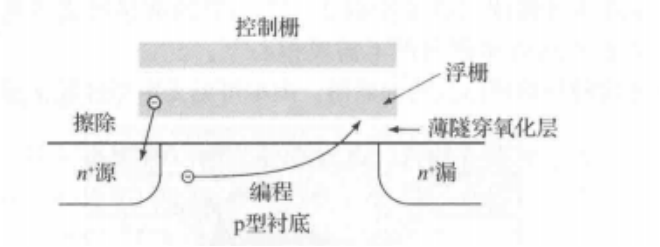

反熔絲技術的主要缺陷在于它的單次可編程特性。雙柵(或者浮柵)器件是一種特殊的晶體管,它的控制柵和晶體管溝道之間還有一個浮柵,可以進行非易失性的編程和擦除。Flash存儲器件(閃存)便利用了浮柵器件最新的技術,即EEPROM器件。EEPROM晶體管(電可擦除)是UVEPROM器件(紫外線可擦除)的改進版,比后者更為進步---UVEPROM是一種可通過電學機制編程(即在特定的電壓偏置狀態下)、通過紫外光擦除(因此它們的名稱里UV表示用來擦除的紫外線,而E表示通過電學方式寫入)的晶體管。UVEPROM器件并不實用,因為要想重新編程,必須從系統中移出然后擦除,而且還需要昂貴的帶有供紫外光通過窗口的封裝結構。EEPROM晶體管利用電學偏置實現編程和擦除(因而采用EE命名)。由于它們可以現場重新編程,因而更為靈活。EEPROM晶體管的結構如下圖所示,它就是一個改進的MOS晶體管。控制柵和普通晶體管的柵極類似,而浮柵被氧化層包圍,并不能被電極直接連接。將存儲內容寫入器件需要將電子打入浮柵中,使之聚集負電荷。浮柵上的負電荷掩蔽了器件的溝道,使之在某種程度上受控制柵上和襯底之間所加電場的影響變小,因而即便控制柵加到Vdd的電平,導電溝道仍無法形成。因此,寫入信息后的器件不會導通,而未寫入的器件的特性則像普通晶體管一樣。

寫入過程是這樣完成的:將器件置于過飽和區,這樣溝道中的熱電子被加速,與襯底中的原子碰撞,然后離開襯底,通過薄的氧化層隧穿到浮柵。擦除過程則是通過將控制柵壓反置為負,讓電子從浮柵中隧穿回晶體管的源極。

03

SRAM

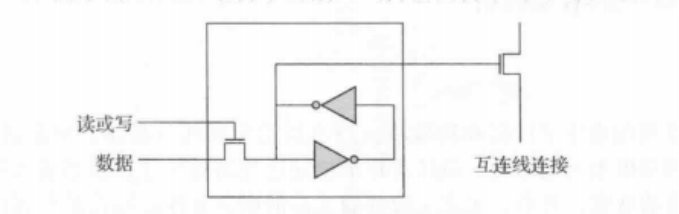

靜態RAM開關技術使用了典型的采用交叉耦合反相器的SRAM單元,以存儲傳輸晶體管或者下圖所示的FPGA結構中的嵌入式傳輸門傳來的導電狀態。

這種技術的優勢從根本上來講在于其與浮柵器件相比,需較短的編程時間。而其缺陷在于它相對較大的面積(這是由于晶體管數更多),并且在每次上電后還需要重新寫入。早期的FPGA在每次上電之后都必須從外部ROM或者flash電路中重新寫入。現今,許多基于SRAM技術的FPGA都含有flash存儲模塊,它們保存了電路的配置數據,可以在每次上電后對電路進行內部寫入。

-

電流

+關注

關注

40文章

6744瀏覽量

131855 -

晶體管

+關注

關注

77文章

9633瀏覽量

137841 -

可編程邏輯

+關注

關注

7文章

514瀏覽量

44072

發布評論請先 登錄

相關推薦

【轉】 時序邏輯電路的三種邏輯器件

PLD可編程邏輯器件

可編程邏輯器件基礎及應用實驗指導書

什么是PLD(可編程邏輯器件)

基于可編程邏輯器件的數字電路設計

實現可編程邏輯電路的三種主要器件

實現可編程邏輯電路的三種主要器件

評論